|

设计要求

|

一、 上电初始化模块状态时序分析

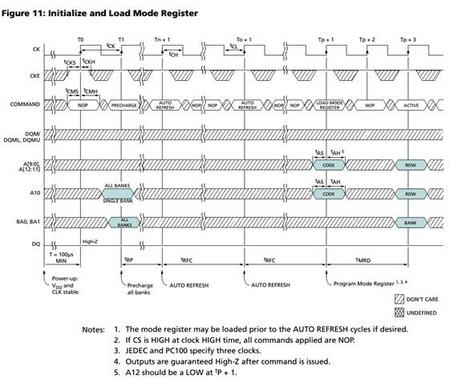

图1.1为MT48LC32M16A2数据手册提供的该芯片的上电初始化以及模式设置寄存器的时序图,因此,该上电初始化模块的状态设计将严格按照此时序图进行。

图(1.1)MT48LC32M16A2上电与模式寄存器设置时序图

该芯片上电初始化包含了以下几个过程:

1、 上电最小100us的延时;

2、 1个周期的空操作指令;

3、 1个预充电过程;

4、 2次自动刷新命令;

5、 设置模式寄存器命令;

6、 等待激活。

其中,预充电命令到第一个自动刷新命令之间的时间延迟最小要求为tRP=20ns。

一次自动刷新时间最小要求为tRFC=66ns。模式寄存器设置时间最小要求为tMRD=2tCLK。当模式寄存器设置完毕后,系统即进入等待激活状态。

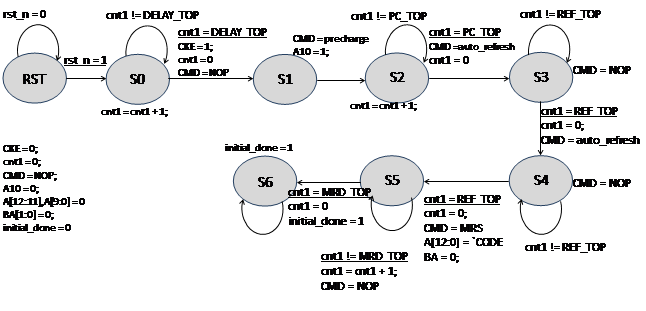

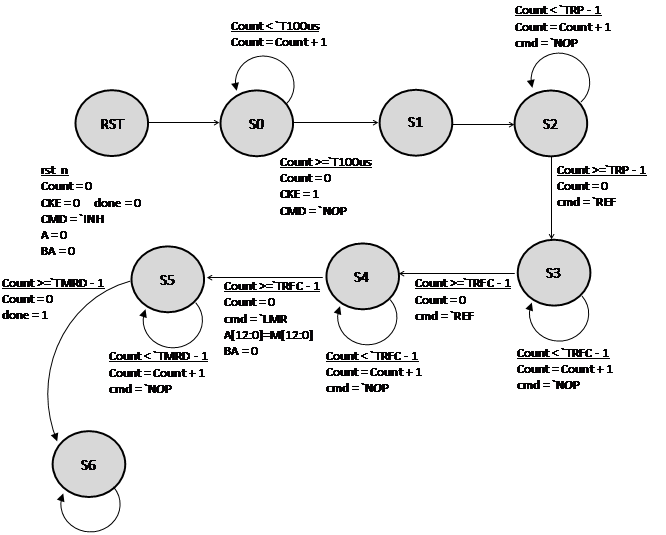

二、 上电初始化模块状态转移图设计

状态设置:

RST:复位状态

S0:上电延时状态(DELAY)

S1:NOP(DO_NOP)

S2:预充电状态(PRECHARGE)

S3:自动刷新状态1(REFRESH_1)

S4:自动刷新状态2(REFRESH_2)

S5:设置模式寄存器(SET_MR)

S6:等待(WAIT)

因为本模块只设计了上电复位,因此上电复位状态结束后就会一直停留在WAIT状态,直到下一次复位信号的到来。

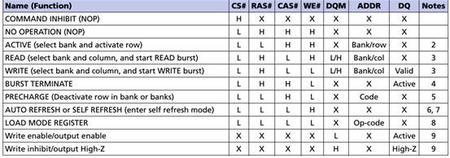

控制命令(CMD)与各控制引脚状态对应关系

本状态迁移图由李老师设计,通过对比,发现我的设计基本能够达到老师的要求,只是老师的更规范,命名更合理,相比之下,我的设计还有很多的不规范不合理的地方,特此对比。在实际代码编写过程中,为了保证代码的规范易读,所以均采用和老师提供的一致的信号名。

|

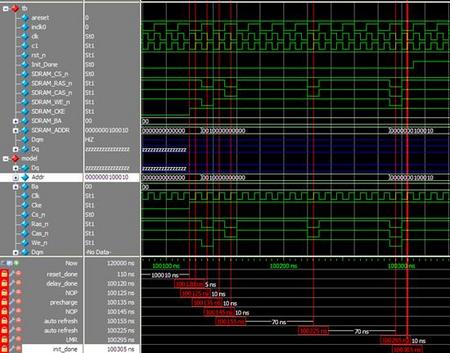

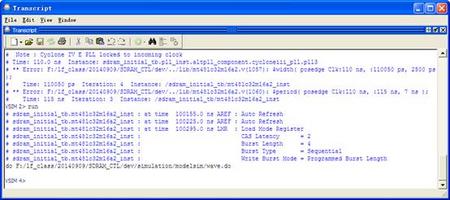

三、 上电初始化模块仿真结果分析

下图为上电初始化模块的仿真波形图,由图可知,该上电初始化模块能够正确的对仿真模型进行初始化,图3.2为Micron官网提供的仿真模型打印出的仿真信息,通过该打印信息也可知上电初始化是成功的。

图(3.1)上电初始化模块仿真波形图

图(3.2)仿真模型输出的信息

用户1728380 2015-1-21 12:55

小梅哥 2014-11-23 15:17

用户1635984 2014-11-23 13:32

小梅哥 2014-10-3 23:31

用户1773503 2014-10-3 08:54

用户1772825 2014-9-11 09:54