写在前面:

此前,我一直知道,在QQ空间发所谓的技术文章不过是为了炫耀什么。可是当我越来越多的读了特权大神,读了彬哥的文章后,我慢慢发现,正是他们的对技术的这种执着和坚持激励着我,正是他们那些新奇严谨的设计吸引了我,让我坚持学习FPGA技术,如果没有他们的文章,我可能不会走上FPGA的道路,一条我认为充满未来的路。回想大学四年,我总是在吸引一些同学来加入我的行列,和我一起学习、进行电子设计,我总希望身边的人有更多能够和我一样喜欢电子技术。想想特权和彬哥对我的影响,我深切感受到,只有自己不断探索,并将探索的结果和人分享,才能吸引更多的人加入到我们的行列中来。于是,我决定继续写我的技术文章,一篇放在QQ空间,供QQ圈子里搞电子的人观看学习,其实也谈不上学习,这些,只是我在北京至芯科技学习到的知识和技术的一个简单记录,我只是希望把自己接触到的东西分享给大家。另一篇,勇敢的挂到热门论坛上,让各路大神来指导我的学习。

文章由Word导入博客后,图片被压缩的很严重,导致图片上的文字都看不清了,因此我在附件中加上了本文的原版PDF,图片内容清晰些,有兴趣想看清图片上文字的,请自行下载PDF文件

今天,李凡老师给我们讲解了Avalon总线的结构,虽然以前做过SOPC,对Avalon总线有一定的了解,但今天听李老师讲过之后,才发现自己原来知道的还太少太少 ,今天,我就分享一个李老师布置给我们的作业,以及我在完成这个作业时的思路和流程。

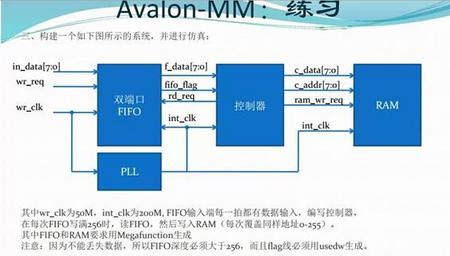

具体Avalon总线是什么,具体结构如何,有何特性,内容实在太多,不是这一篇文章能讲述清楚的,这里,我只取其中很小的一点来讲做。下图为练习的题目,题目要求写的很清楚,因此这里不再赘述。

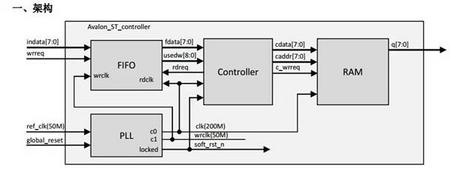

下图为李老师为我们设计好的具体架构实例,在这里不得不说李老师是劳模级的老师,因为我们刚开始接触这个,都没经验,做起来特别困难,于是李老师就一步一步的给我们做示范。一个退休老工程师还能有这份耐心,实在让人感动。

其中,灰色方框外的信号为外部接口信号,方框内的信号均为内部信号,相信看了这个结构图以后,对于这个该系统改怎么去实现也是一目了然。李老师要求我们做设计时,不能先写代码,最后再总结结构,而是要先把结构想清楚,并绘制出状态转移图或状态转移表,最后再根据图或者表进行代码的输入,这样能够保证设计的正确性和结构的合理性。

当架构设计出来后,李老师要求我们必须先绘制出正确的状态转移图,然后再编写代码。下面先贴上对该系统设计的状态转移图。

因为结构简单, 信号线较少,因此该状态转移图设计起来较为简单。但是从这个图中我们可以看到,还是有很多内部信号,我们的设计,就是要有序的组织这些内部信号,让信号按正确的节拍走,这样才能得到正确的结果。但是,因为我经验不足,能力有限,在设计状态转移图的时候就遇到了困难。图中,rdreq、c_wrreq、cdata、caddr之间的关系我并不十分清楚,这些都是IP核的信号线,IP核的工作时序是怎么样的,我并不是十分清楚,因此在设计状态转移图的时候就会遇到问题,这些信号究竟该怎么组织才能让这些IP核争取的输入和输出呢?没办法,我只能采用最笨但也是最保险的办法,先对这些IP核进行一下仿真,通过仿真波形,就能知道其工作时序了。

三、系统使用的IP核工作时序分析

本系统中使用到了三个IP核,分别为异步fifo,锁相环(pll),单口ram。为了保证整个系统时序的正确性,必须先对这三个IP核的时序有一个清晰的了解。下面,就通过modelsim对这三个模块进行仿真,通过仿真来确定这三个IP核的正确应用时序。

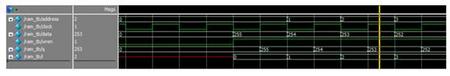

3.1 fifo的工作时序分析

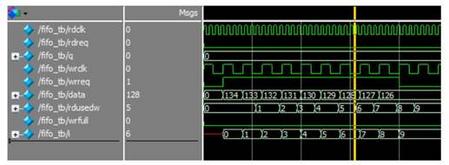

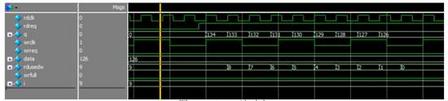

本系统中,fifo配置为异步读写,其它为配置时的默认设置。以下图(3.11)为fifo写时序,图(3.12)为读时序。由图可知,写请求信号可以和待写入数据同时有效,下一个时钟周期,数据即被写入fifo。读请求发出后,数据会在读信号有效的第一个时钟上升沿即出现在数据总线上。

图(3.11)fifo写时序

图(3.12)fifo读时序

3.2 pll的工作时序分析

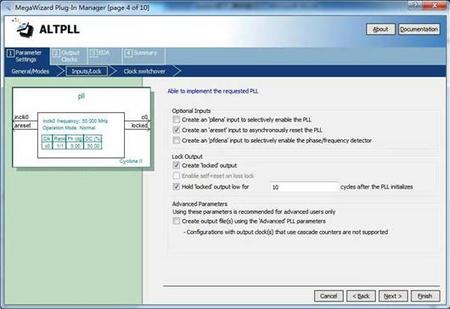

本设计中pll的配置情况为50MHzsink时钟输入,带areset信号和locked信号,并保持locked信号10个周期的低电平,该配置具体见图(3.21)。两路时钟输出c0 = 200M,c1=50M,相位相差0°。

图(3.21)PLL端口信号配置详情

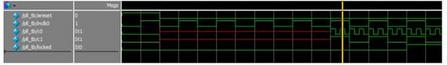

pll仿真结果如图(3.22)所示。该时序图中出现了和我们预设有出入的地方,locked并不是在pll稳定之后保持了10个周期的低电平,而是8个,更换不同的保持周期,仿真结果不变,因此这是一个问题,目前还没有查阅到合理的解释。

图(3.22)pll仿真结果

3.3 ram的工作时序分析

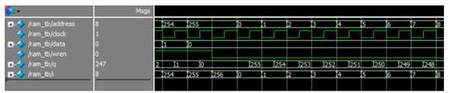

图3.31为ram的写时序,通过写使能(wren)、地址(address)、待写入数据(data)和ram输出口(q)上的数据可知,当写使能有效后,下一个时钟上升沿数据会被立即写入ram中,这一点从ram输出口上的数据在写使能有效后的下一个时钟上升沿出现写入的数据可以得到验证。(本设计中q输出为组合逻辑,没有被时钟同步,因此一旦内部数据变化,会立即反应在输出口q上)。

图3.32为ram的读时序,因为ram的结构是输入地址会被时钟同步,因此当地址发生变化后,会在下一个时钟上升沿到来时变为有效,因此,有效数据也会在此时输出。即ram的读时序为,当写使能(wren)无效时(由ram的写时序图可知,当wren有效时q上也会出数据,但是ram内部的数据会被改写,因此当写操作有效时,默认q输出数据无效),地址变化后下一个时钟周期输出该地址对应的有效数据。即读ram数据会有一个时钟周期的滞后。

图(3.31)ram写时序

图(3.32)ram读时序

本来最后还应该贴上我的练习设计最终仿真结果,但是波形太多,看起来特别杂乱,再说,读者可能更看重设计思考的过程而读结果无暇做过多的研究,因此我就不在贴上结果。

本次练习,主要熟悉了fifo、pll、ram的使用,通过仿真观察时序来得到其正确的使用方法,是本文的重点。

/4

/4

用户3679016 2016-3-17 15:10

用户1567715 2015-9-25 11:36

hot.summer_2010_438634915 2014-8-30 06:05