曾经有一位彪悍的女同事,去了新单位后要确认一下静电电容到底能起多大的作用,能抗多大的静电,她把模块上所有的静电电容全部去掉,然后打一下静电,单片机就重启一下。

前面写过两篇文章是关于静电电容的

ESD电容问题

谈谈模块的的引脚布置和ESD问题

在这两篇以外举几个实例说明一下:

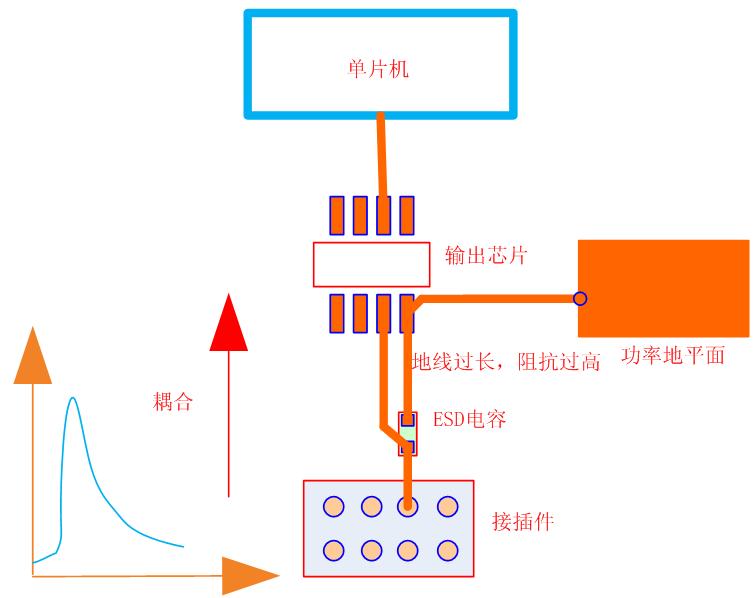

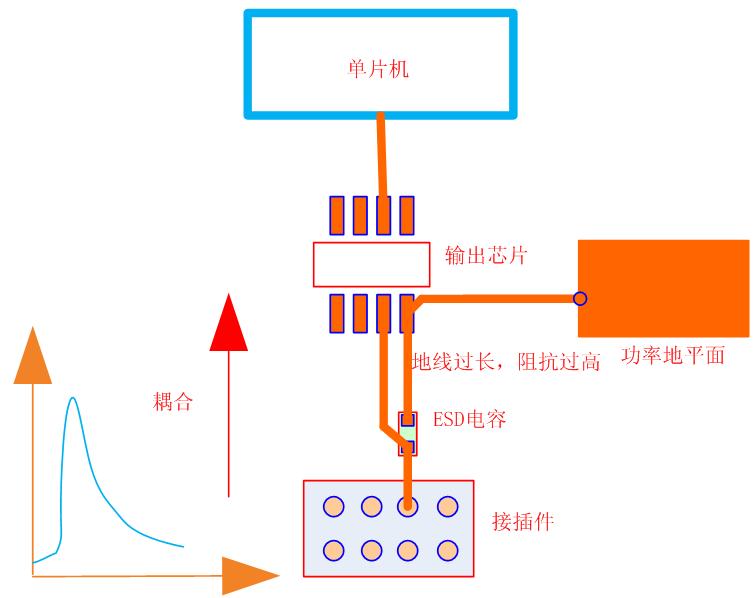

第一个例子是这样的,在打静电的时候测试EMC的性能(国内一般不这么BT的要做合成实验),出现了两个问题,第一个是单片机Reset了,第二个是某个频率段发射限值超标。

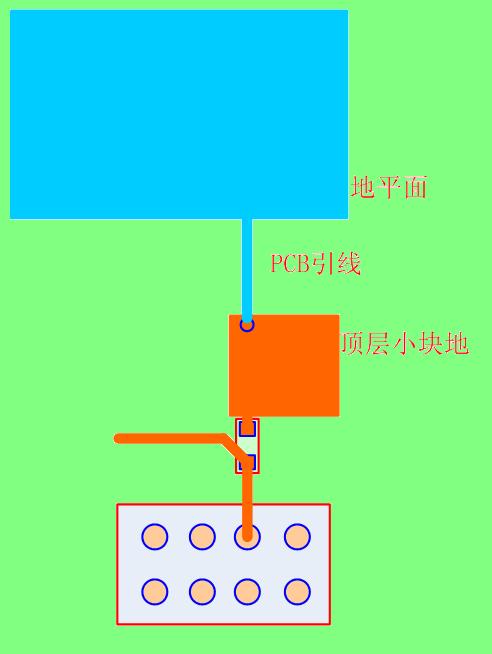

经过调查发现了原因是一个输出IC,由于是功率地,因此静电电容并没有直接打在地平面上,而是通过一根很长的PCB连线连接至地,因此阻抗比较高,这就变成了一跟天线,并且耦合至单片机,导致了单片机的Reset.

静电电容布线有三个原则,第一是必须给每个接插件引脚配上静电电容,第二是尽可能使得电容靠近接插件的引脚,第二个是尽可能使电容靠近地平面。

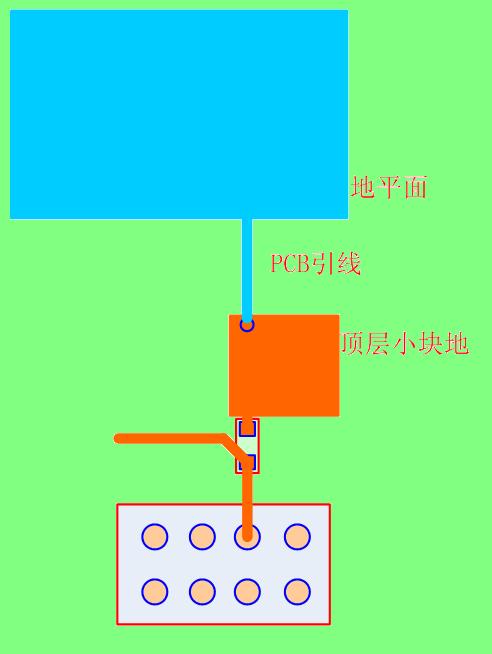

看下面一个例子,这次ESD直接把模块引脚打坏了

上例是在电容接到的是顶层一小块地,通过小的通孔连接后在内层连接地平面,距离过长,阻抗过高。

在某些极端情况下,ESD还会损坏MCU,特别是某些单片机有内部的稳压器,和它相近的IO口如果用来做输出而且没有很好的接静电电容(包括电容地没接好的情况)可能严重损坏单片机的稳压器,这会导致非常严重的结果。

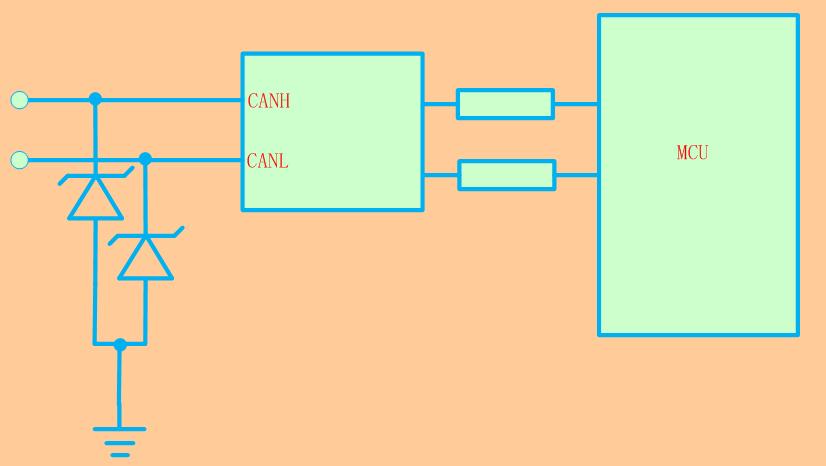

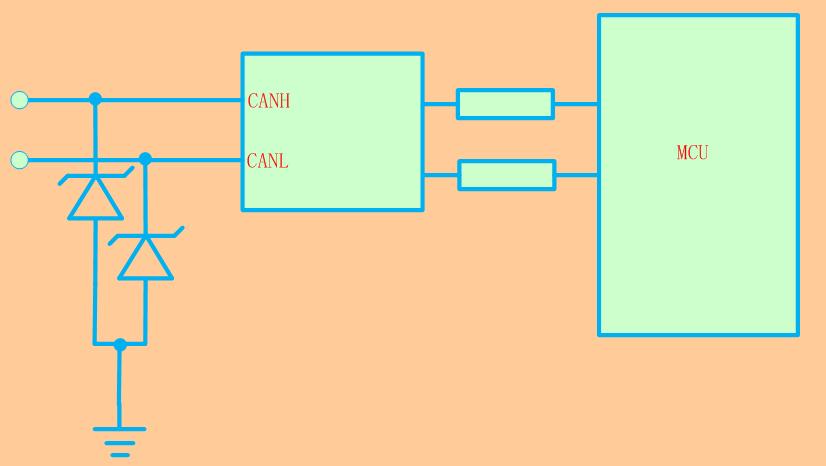

还有一个值得注意的CAN的通讯口,一般高速的CAN不允许接大一些电容,这时候只能通过附加K级的电阻来防止信号耦合后损坏器件了,有钱的话可以选择TVS。

/4

/4

朱玉龙 2009-11-5 00:10

dongbei06_409353400 2009-11-4 16:35

朱玉龙 2009-11-4 12:04

用户1359678 2009-11-4 09:01