原创

检查RC时间常数

2009-11-5 20:39

4745

7

8

分类:

模拟

这次设计的问题和下面三个博文:

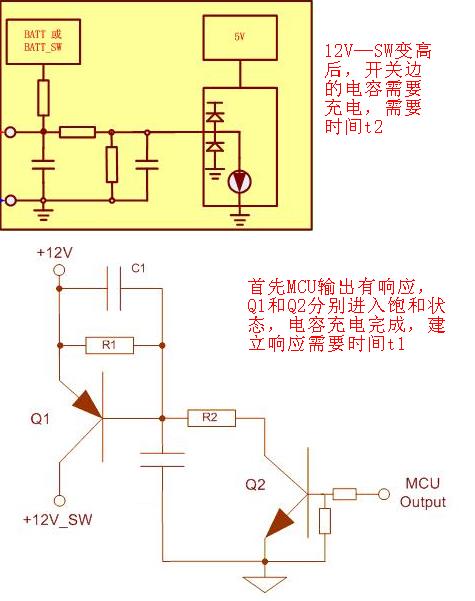

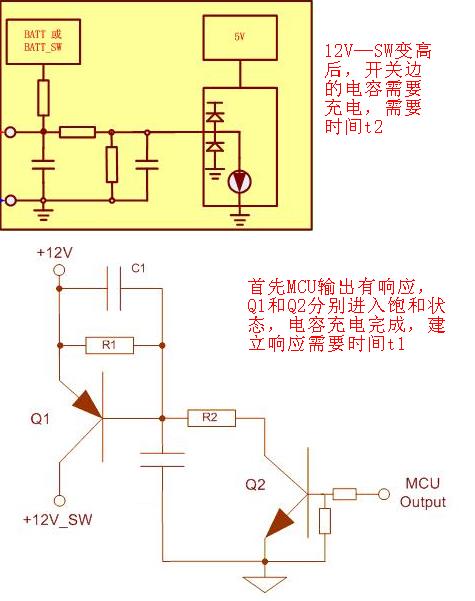

三极管的开关电路分析(12V—SW)设计模块的低有效接口电路

设计模块的高有效接口电路

模块静态电流设计

我们设计的睡眠策略是建立在以下的基础上的:

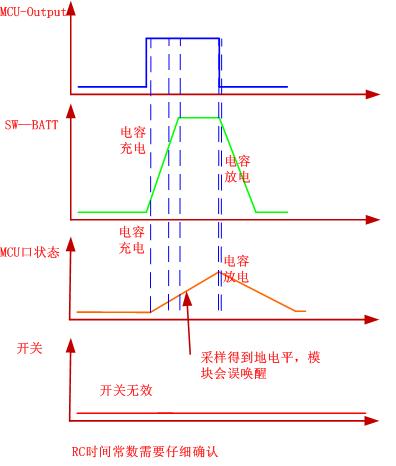

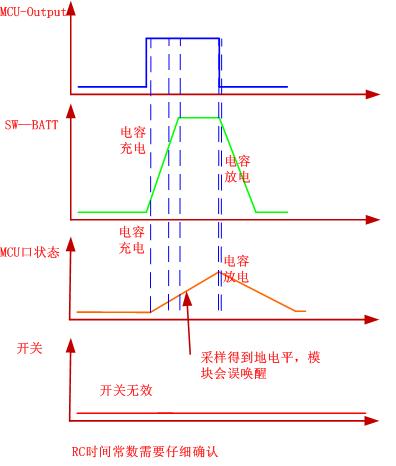

为了使静态电流变小,BATT—SW开启是间歇性的,因此就需要在开启后延迟一定的时间,时序如下:

因此我们在设计RC时间常数的时候需要非常小心。

设计的方法为暂态响应计算:

暂态分析和拉普拉斯变换1

暂态分析和拉普拉斯变换2

另外一则例子与之是非常相似的,要始终注意电容是否有泻放回路和泻放时间是否符合设计要求。

/4

/4

dongbei06_409353400 2009-11-5 20:02