特权同学,版权所有

配套例程和更多资料下载链接:

http://pan.baidu.com/s/1jGjAhEm

在上一个实例的基础上,如图所示,我们先到工程所在文件夹中,创建一个名为“source_code”的空文件夹,将来新创建的Verilog源文件,我们都把它们存放在这里,这样做的好处是便于查看和管理。

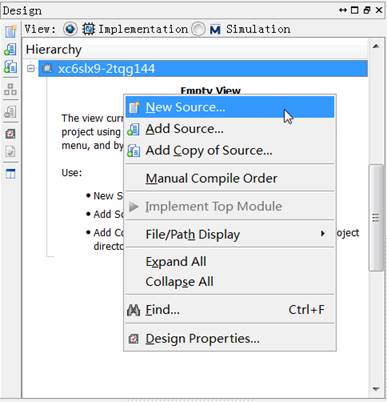

接着回到ISE中打开sp6ex1工程。我们在“Design à Implementation à Hierarchy”中的任意位置单击鼠标右键,弹出菜单中选择“New Source..”。

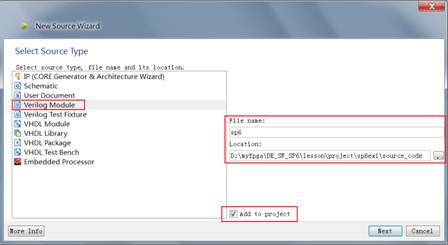

在“New Source Wizard”中,做如图所示的设置。

● “Select Source Type”中选择新建文件类型为“Verilog Module”。

● “File name”即文件名,因为这个文件要作为工程的顶层文件,所以最好是和工程名称一致,即“sp6”,如果不是工程顶层源文件,名称随意起,当然了也不要有中文和符号(还是要以字母、数字、下划线为主)。

● “Location”下面输入这个新建文件所存放的路径,我们将其定位到新创建的“source_code”文件夹下,整个路径为“D:\myfpga\DK_SF_SP6\lesson\project\sp6ex1\source_code”。

● 勾选上“Add to project”。

完成以上设置后,点击“Next”继续。

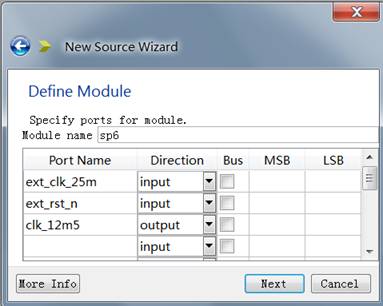

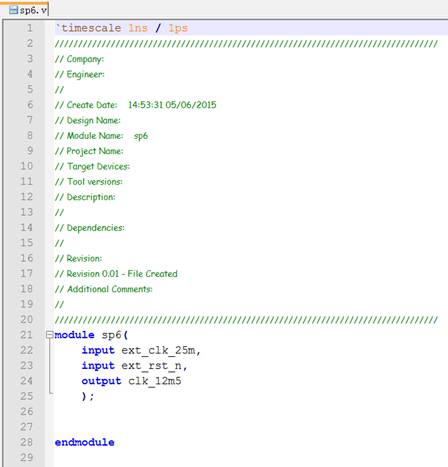

在接着弹出的“Define Module”窗口中,默认出现了“Module name”为“sp6”,即我们上一个页面设定的名称,不需要修改。接着如图所示,我们分别设定三个信号ext_clk_25m(input)、ext_rst_n(input)、clk_12m5(output)作为设计文件的对外接口。这个地方也可以不用设置,创建好Verilog源文件后直接在文本中编辑也行。完成设置后,点击“Next”继续。

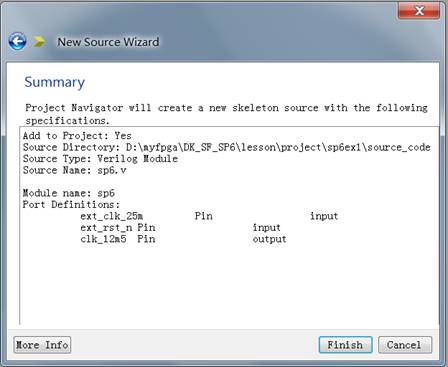

最后弹出“Summary”页面,点击“Finish”完成创建。

此时,弹出了Notepad++打开的sp6.v文件,即我们刚刚创建好的Verilog工程源码文件。

此时,在source_code文件夹下也出现了sp6.v文件。

在sp6.v源文件中,输入一段对时钟二分频的代码,编辑好后的sp6.v源文件代码如下。

//对外部输入时钟做二分频

module sp6(

input ext_clk_25m, //外部输入25MHz时钟信号

input ext_rst_n, //外部输入复位信号,低电平有效

output reg clk_12m5 //二分频时钟信号

);

always @(posedge ext_clk_25m or negedge ext_rst_n)

if(!ext_rst_n) clk_12m5 <= 1'b0;

else clk_12m5 <= ~clk_12m5;

endmodule

这段代码的功能是:

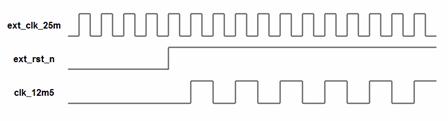

● 输入复位信号ext_rst_n为低电平时,即复位状态。无论输入时钟ext_clk_25m是否运行,输出信号clk_12m5始终保持低电平。

● 输入复位信号ext_rst_n为高电平时,即退出复位。每个ext_clk_25m时钟信号的上升沿,信号clk_12m5的输出值翻转。

如图所示,这便是前面的代码将要实现的功能。

/3

/3

用户593939 2015-9-27 17:43

用户1778417 2015-9-24 19:35