首先第一步是博士在第59讲里讲到的钻孔(NC Drill)操作,即生成钻孔处理文件。参考博士的视频操作即可。

其次是出光绘,即最后一讲博士第60讲的内容。

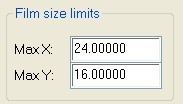

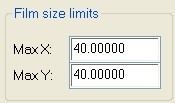

在出光绘时,设置参数界面有个底片尺寸,如果采取默认值,如图1所示,那么我的板子会报错,一开始没注意是这个问题,后来一想我的板子物理尺寸较大以致都大于Allegro默认的底片尺寸。改成如图2所示即可。

图1

图2

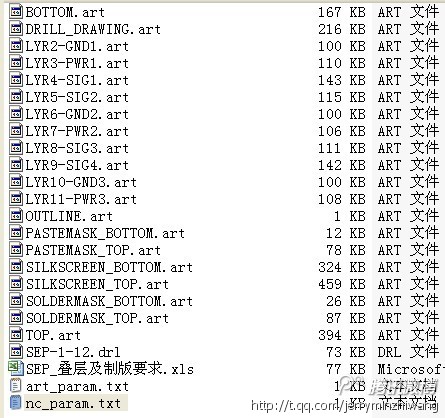

本人的板子是12层,那么提交给制板厂的文件有哪些呢,如图3所示。

虽然视频以及图3详细给出了提交给PCB厂生成所需的所有文件,这里还是要总结一下除了钻孔文件之外,出光绘所需要的层(film):

1、当进入artwork,默认所有的电气层已自动添加了相应的film。

2、丝印层,包括顶层和底层丝印层。而每层一般又包括以下三个subclass,即(1)Package Geometry Silkscreen,(2)Manufaturing Auto Silk,(3)Board Geometry Silkscreen。

3、Solder Mask,包括顶层和底层。而每层都包括了Stackup和Geometry下相应的Subclass。

4、Past Mask,同3.

5、Outline(可以单独出,也可以在每层作为一个subclass形式出,个人建议单独出)。Geometry->Board Geometry->Outline.

6、Dirll Drawing。Manufacturing->NClegend-1-12.

注:添加每个subclass的时候,先把”color and visibility“下所有层都关闭显示,然后将需要的层打开显示,之后用Artwork点available films任一个(右击)用”add film“。

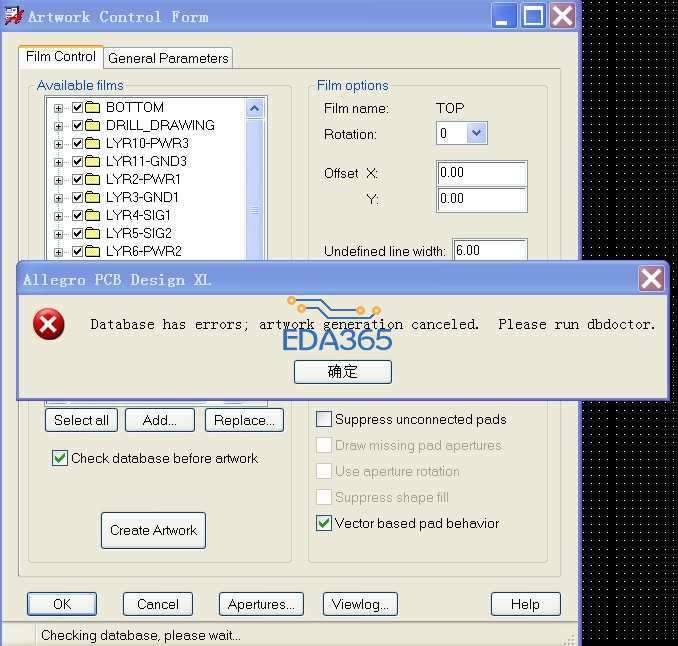

最后就是Create Artwork了,只是我在这一步的时候出现一个问题,如图4所示

图4

上述出错弹出的窗口信息告诉我要运行DBdoctor,先查看log文件发现我的pcb文件有高达2100个相同error:

ERROR IN RATSNEST

POINTER TO RATSNEST INVALID

ERROR IN RATSNEST net name = ANALOG24

POINTER TO RATSNEST INVALID

只有最后一个error给出了net name。

运行DBdoctor并”check“之后查看log文件提示所有error都被fixed的了。

ERROR IN RATSNEST

POINTER TO RATSNEST INVALID

Error was fixed.

ERROR IN RATSNEST net name = ANALOG24

POINTER TO RATSNEST INVALID

Error was fixed.

WARNING IN NET name = ANALOG24

WARNING(SPMHDB-43): Ratsnest lines are out of date.

Warning was fixed.

WARNING IN NET name = ANALOG10

WARNING(SPMHDB-43): Ratsnest lines are out of date.

Warning was fixed.

WARNING IN NET name = GND

WARNING(SPMHDB-43): Ratsnest lines are out of date.

Warning was fixed.

WARNING WARNING(SPMHDB-42): Run batch DRC to correctly regenerate DRC errs.

4 warnings, 2100 errors detected, 2100 errors fixed.

/5

/5

coyoo 2014-7-30 11:46

用户377235 2014-7-30 11:19

怎么没有下文了??我也遇到这样的问题,不知道怎么解决。