首先,介绍本人为何要使用Xnet。本人使用Xnet的场合主要有两种场合,一种是走线路径阻抗匹配,所以走线中串接了一个匹配电阻,如果需要等长,所以要给这一组走线设置Xnet;另一种是高速差分走线以及像Altera的高速Transciever的差分走线一般都需要对高速差分线进行AC耦合,所以每根线上串接了一个0.1uF的电容,而差分走线都需要进行等长,所以需要计算电容两端走线之和来进行等长控制。

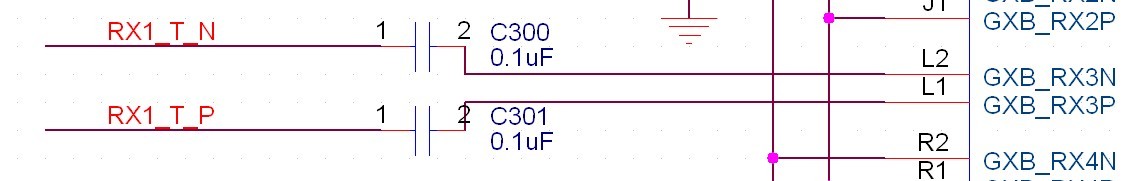

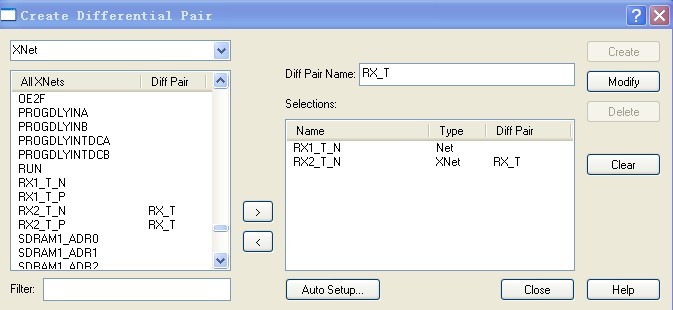

如果没有建立Xnet,如图1所示的差分走线的每一根就会分为2段net。那么在Allegro的约束管理器中进行等长设置的时候需要首先建立差分对(Diff pair),这时候你会发现有图2所示的情况出现。从图2能发现什么呢?即RX1_T_N和RX2_T_N的“type”是不一样的,显然RX1_T_N的type是net而RX2_T_N的type是Xnet,也就是在建立差分对约束的时候前者只是约束了一部分,而后者是约束了整根线。

图1 Altera的GXB高速接收通道

图2 在Allegro16.3的约束管理器中建立建立差分对

根据文章介绍,第一步是要建立Xnet,建立Xnet的过程如下所示

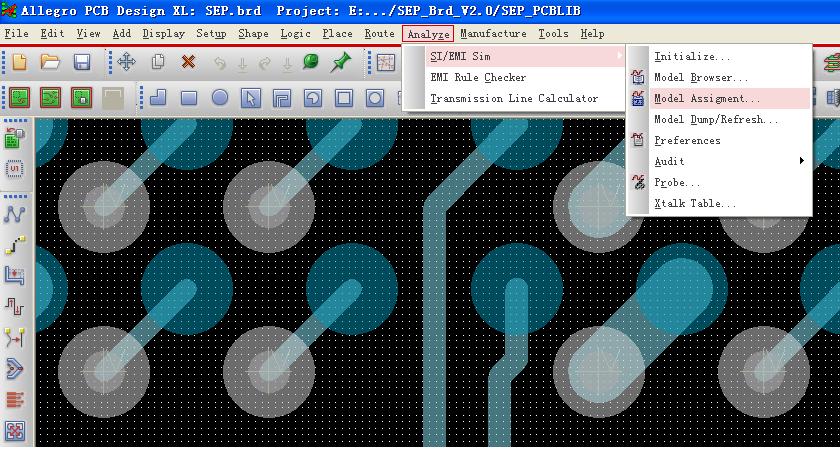

第1步,在Allegro的PCB Editor的Analyze菜单下选择SI/EMI Sim->Model Assignment命令,如图3所示

图3 启动开始建立Xnet

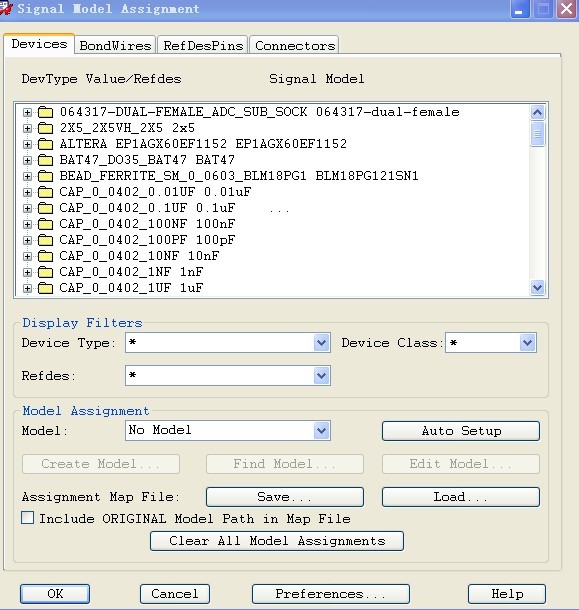

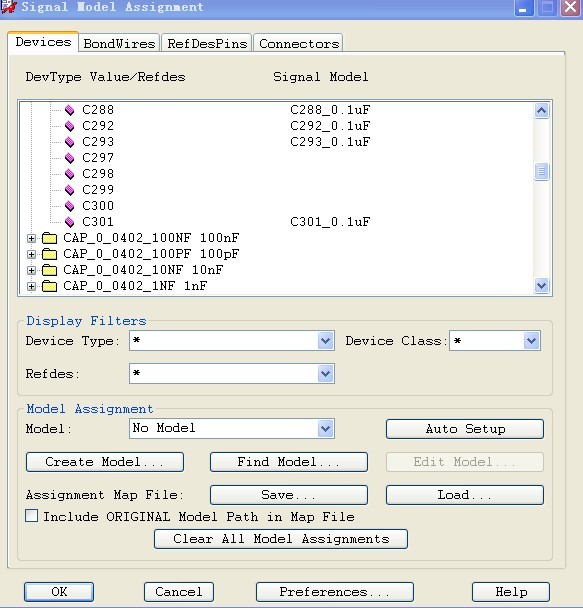

第2步,进去以后会看到如图4所示的界面,由于差分线中串接的是0402封装的0.1uF的电容,所以选择此项。可以看到此项下包含了所有工程里使用的所有的该类电容,选择你需要建立Xnet的电容,如图5所示。

图4

图5

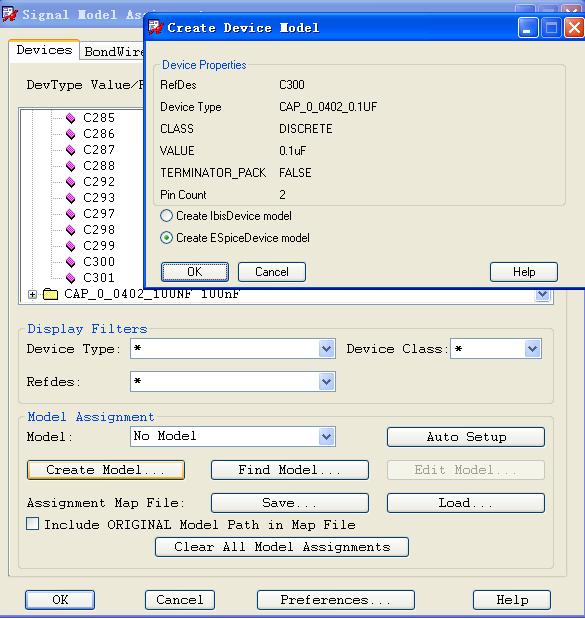

第3步,在上述图4,和图5中选择相应的电容,这里是C300,(注意,这里我们事先已经将C301建好了Xnet),然后点击“Create Model”命令进入创建模型界面,如图6所示。

图6

第4步,在图6的create device model界面,选择“create ESPisedevice model”,然后点击“ok”进入下一步,如图7所示

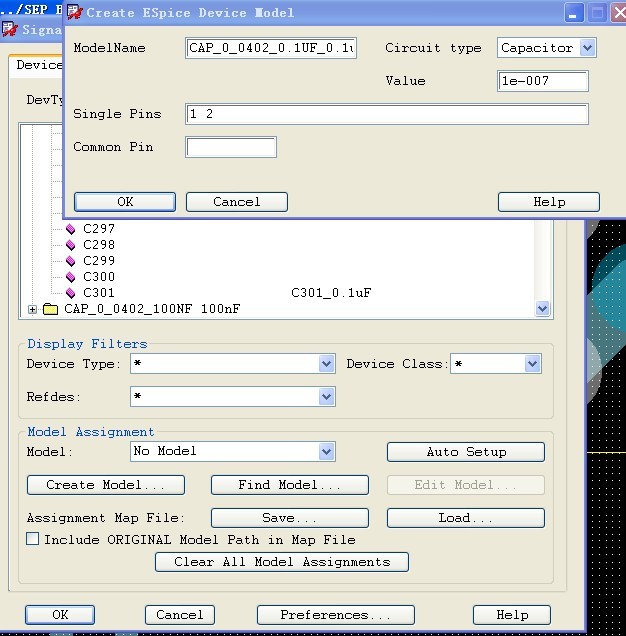

第5步,进入这一步以后如图8所示,基本无需任何修改,直接“ok”即可完成设置。

图8 完成Xnet设置

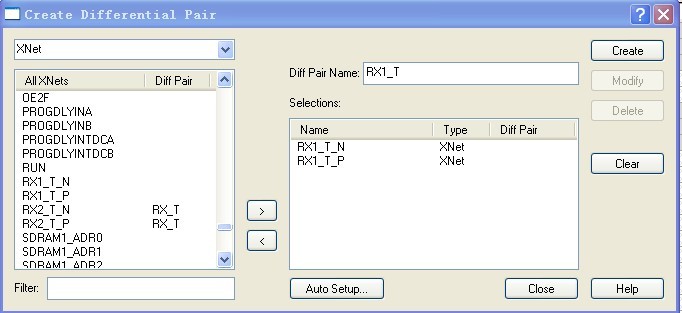

在完成Xnet设置以后,下面就可以进行等长设置,这里是差分对等长设置,所以要先建立差分对,那么就回到了图1所示界面。如图9所示,比较下这两个图的区别,就可以发现这时候RX1_T_N和RX1_T_P的“type”都是Xnet了。

图9

创建差分对以后就可以进行等长约束了,这里就不做介绍了。

用户493620 2015-8-15 12:34

用户377235 2015-3-16 18:01

挺好的

jackbreak_336310931 2015-1-27 11:12

用户377235 2013-7-11 13:17

用户1380173 2013-6-9 17:26

用户403664 2012-7-10 09:23