原创

仿真Xilinx的PCIe时使用pio_writeReadBack_test0测试问题分析

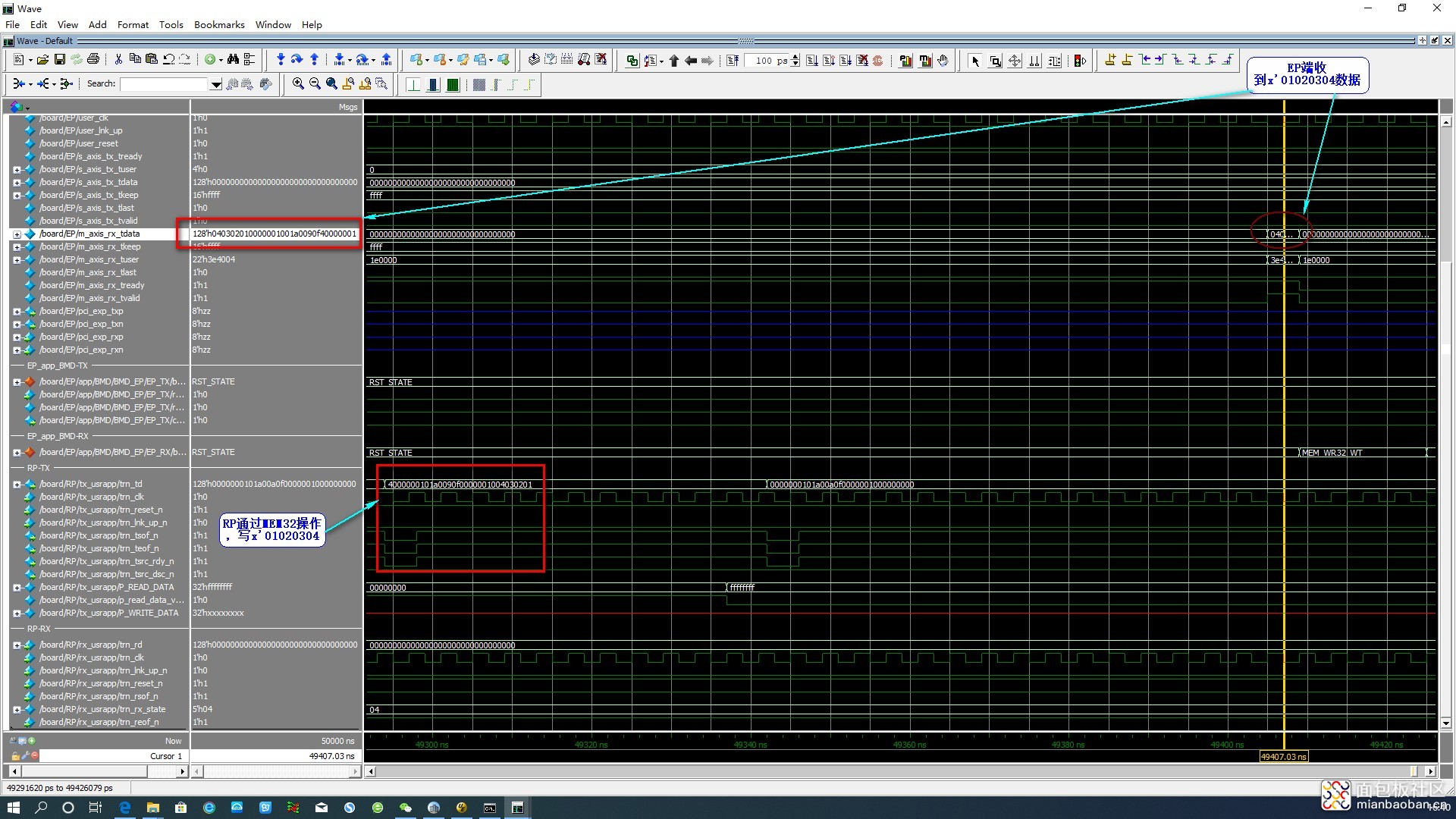

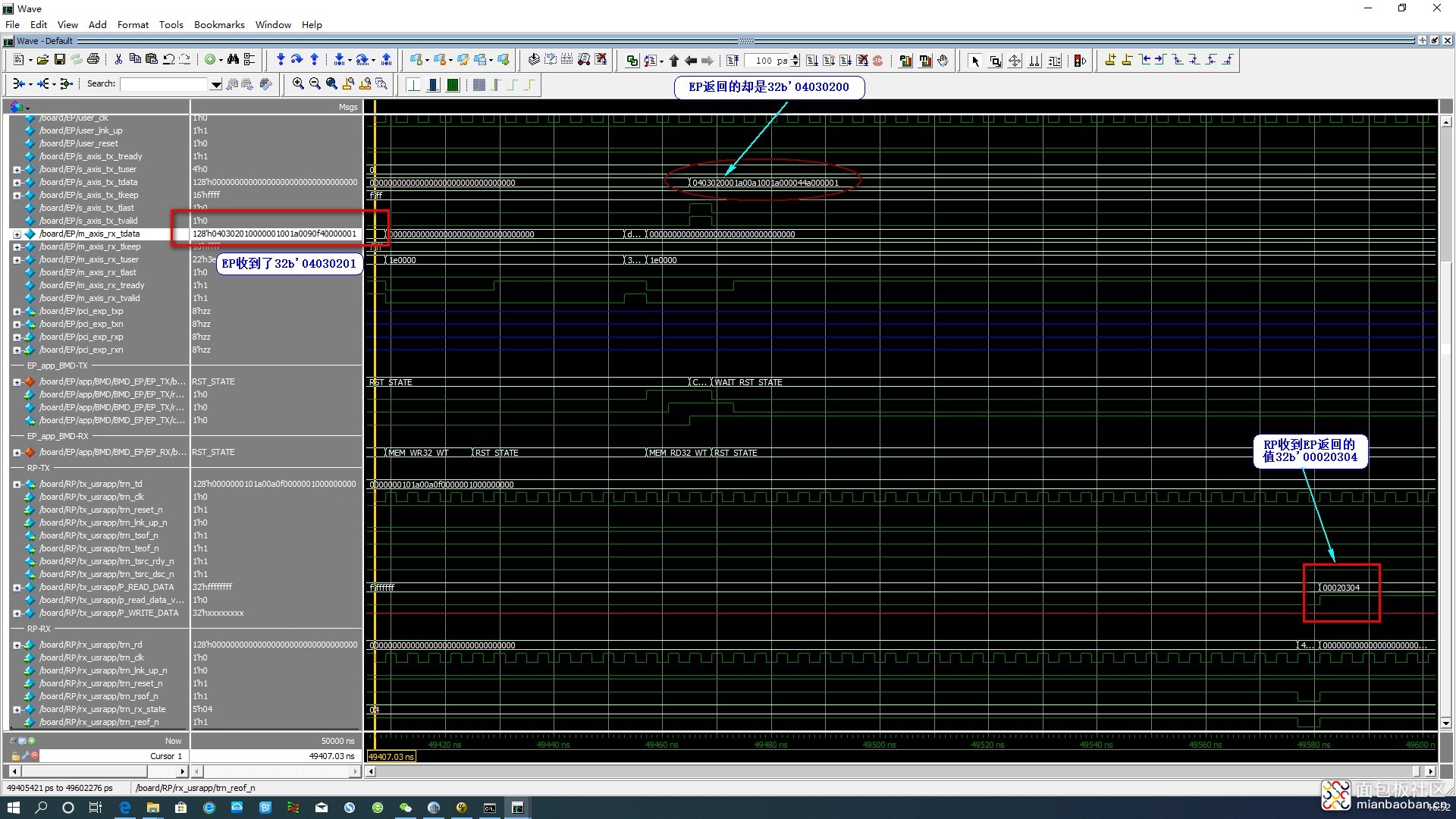

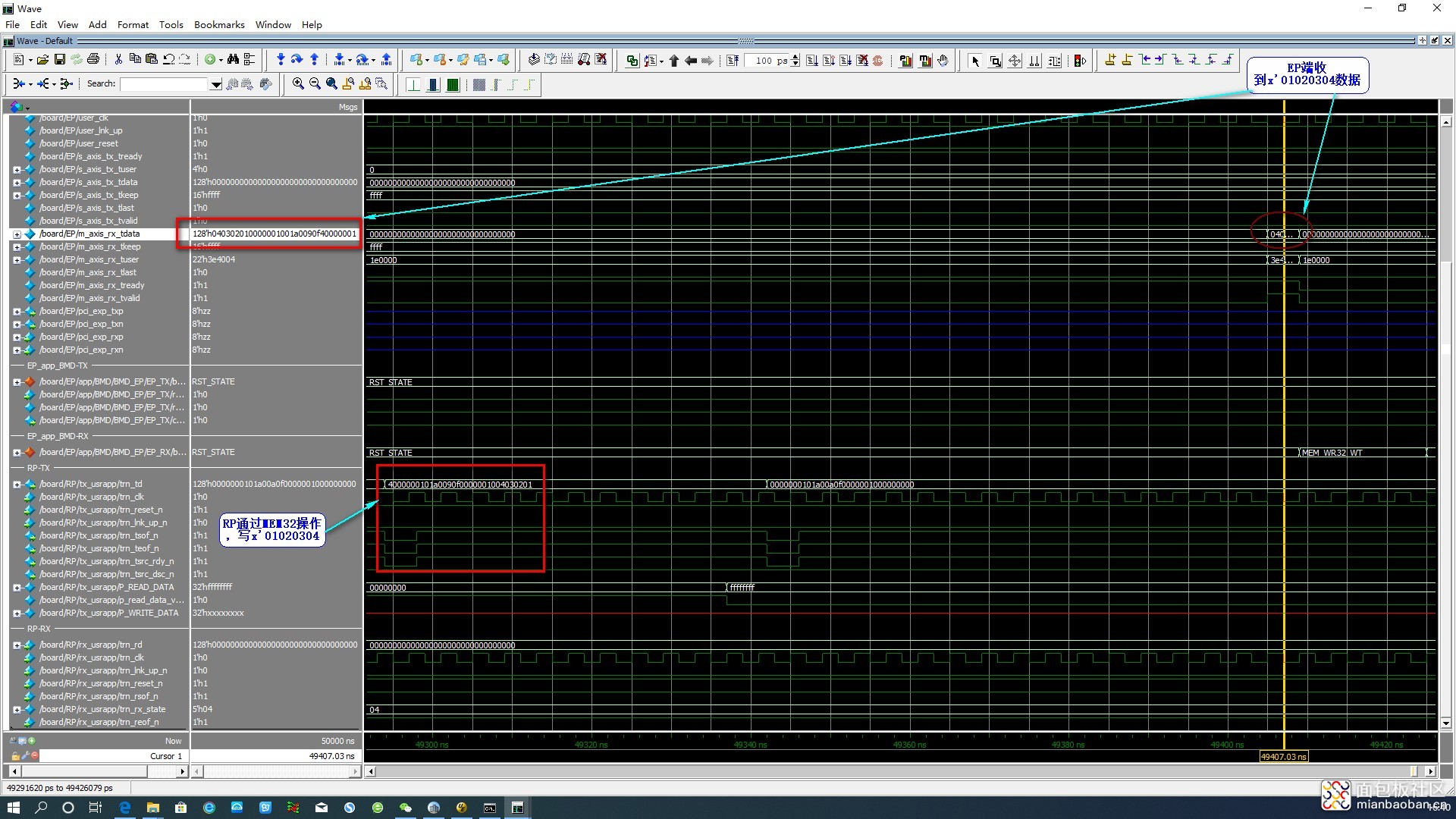

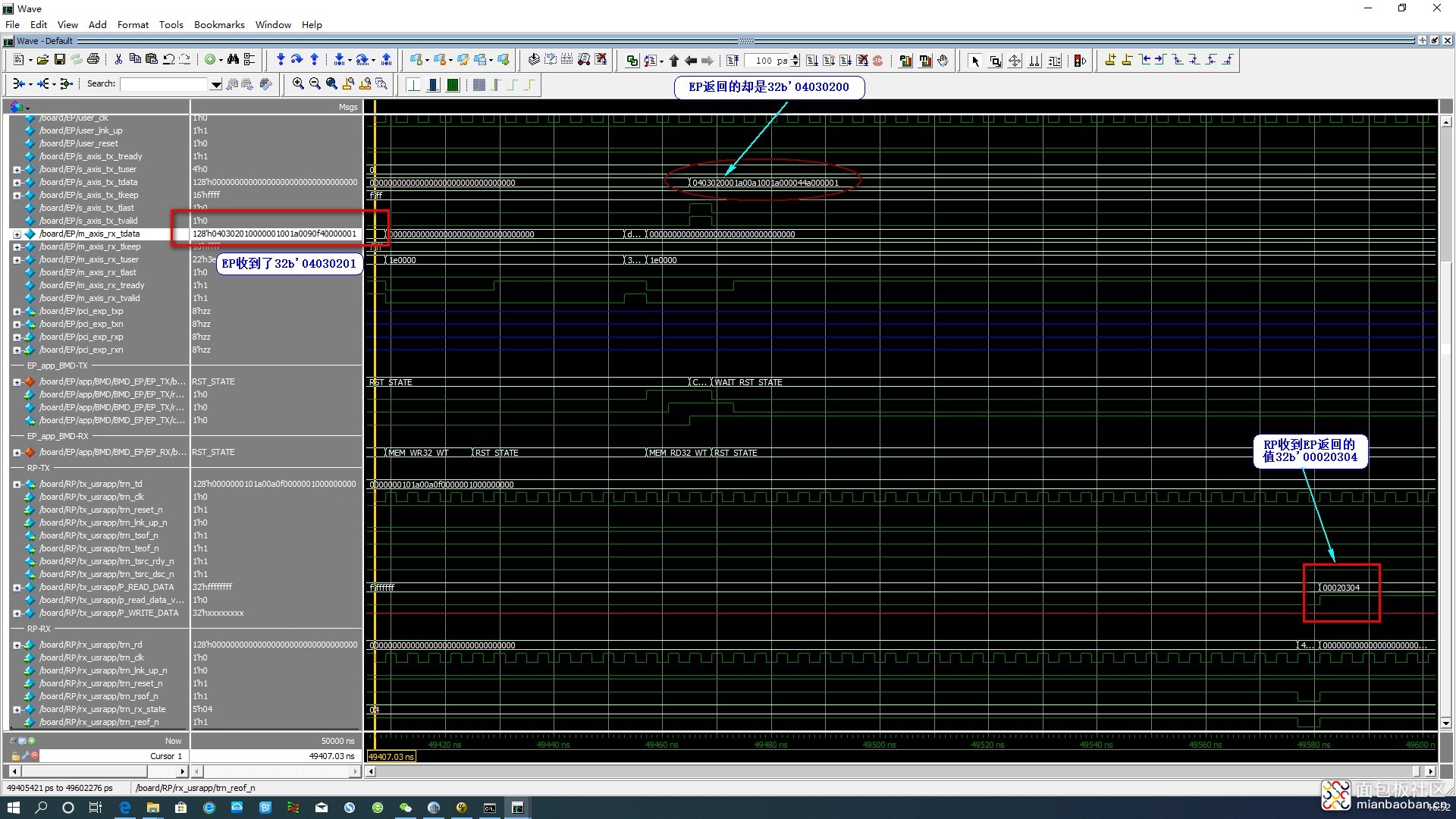

Xilinx的参考设计仿真给出RP模型下3个测试函数,前两个仿真都通过,只有pio_writeReadBack_test0测试默认的MEM32写和读回的时候,写入和读回的数据不匹配,写入32b'04030201,读回来的却是32b'04030200。

如上图所示,RP发送32b'01020304到EP,并读回,EP也能正确收到该值。然后,在EP返回的时候,却变成了32b’04030200(注:自己颠倒是正常了,问题出在字节“01”变成了“00”)。如下图所示,RP确实收到是32b'00020304。

这个问题最终的解决,可以参考博文https://mbb.eet-china.com/blog/1010859-407798.html,在比较BMD128和BMD64的时候,发现相同MEM32写+读回操作,Xilinx给出的基于K7系列参考设计测试激励发送的addr_i是“4”,而在BMD64模式下,该值是“2”。请对照上述博文中128与64位的仿真时序图查找addr_i值,这个参数在BMD_EP_MEM.v中用于解码不同的功能,在“2”时,对应MEM32写的值直接赋值到MEM32读的数据,所以如此仿真才会Test Passed,写入和读回的值相同。

我是修改测试激励中读写操作对应参数,使得addr_i得到一个“2”,问题是该测试激励是一直继承下来,根本解决方法应该不是修改测试激励,这个需要Xilinx给出答复。具体修改如下,一共需要修改2处,分别是MEM32写和MEM读,将“+8‘h10”修改为“+8’h08”

//board.RP.tx_usrapp.BAR_INIT_P_BAR[board.RP.tx_usrapp.ii][31:0]+8'h10, 4'h0, 4'hF);//Modified by Jerry

board.RP.tx_usrapp.BAR_INIT_P_BAR[board.RP.tx_usrapp.ii][31:0]+8'h08, 4'h0, 4'hF);复制代码

作者: coyoo, 来源:面包板社区

链接: https://mbb.eet-china.com/blog/uid-me-1010859.html

版权声明:本文为博主原创,未经本人允许,禁止转载!

/5

/5

文章评论(0条评论)

登录后参与讨论