PLLCK为时钟源,分频系数为1

PLLCK的MUL=25,DIV=5,即PLLCK为96MHz左右

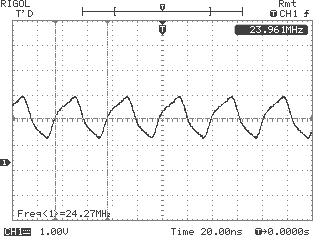

20M以上波形已经变成三角波而且幅值变小很多

| Question |

|---|

Can I use a Programmable Clock Output (PCKx pin) to clock my Ethernet PHY? |

| Answer |

Most of our on-chip PLLs feature 5% max of cycle jitter in percent of the output clock period. Ethernet PHY are used to having a frequency tolerance of ±50ppm. That means it is not possible to generate a frequency with a tolerance of ±50ppm through our PLL and so on a PCKx output pin. |

/3

/3

文章评论(0条评论)

登录后参与讨论