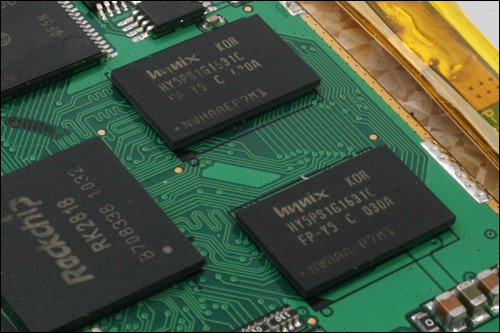

这次选择的DDR2存储器棵粒是现代的,型号为HY5PS1G1631C,结构为64M*16,很适合我的项目需求。附件1是数据手册,供参考。

其实选择哪个公司的存储器并不重要,因为都是标准产品,所以相差也不会太大。主要的是封装,DDR1还是TSSOP封装,自己还可以焊接;DDR2标准已经变了,全是BGA封装了。这一点是主要的了。棵粒HY5PS1G1631C外观下如下,

下面是EP3C25F324与DDR2相连的几组管脚,在设计时都需要仔细考虑。

1、数据线(DQ,data)。数据线是双向的,简称DQ线。从FPGA的方向看,向存储器写数据称之为D;从存储器读数据称之为Q,两者合在一起就是DQ了。EP3C25F324支持双向的数据通道路,DDR2的DQ线一定要连接到EP3C25F324的DQ引脚上。

2、数据选通线(DQS,data strobe)。在Cyclone III系列中(以下简称C3),DQS信号在向DDR2写数据的过程中,并没有实际使用,即使是这样,在硬件上也必须将两者的DQS线连接在一起。DQS信号是由PHY内部产生的。(此处需要查证)

EP3C25F324共有四个组(BANK),分为上下左右四个,每个组都支持DQ和DQS信号。具体是每个组支持2个X8的DQ信号,只支持1组X16的DQ信号,这个在设计的时候需要注意。

3、时钟线(CK,CK#)。差分时钟信号用来捕获地址和命令信号。在设计时,一定要将差分时钟信号固定在差分I/O引脚上(differential I/O),不能放在DQ引脚上。

4、命令线(command signals)。DDR2的命令线比较简单,可以绑定在任何一个用户I/O上。

5、地址线(address signals)。DDR2的地址线比较简单,可以绑定在任何一个用户I/O上。

更多文章请访问:

我的博客1:http://bbs.ednchina.com/BLOG_liangziusb_440752.HTM

我的博客2: http://www.eefocus.com/liangziusb/blog/

EDN小组http://group.ednchina.com/GROUP_GRO_14600_3466.HTM

LZ3684 USB2.0开发板(CY7C68013A), 请访问我的淘宝http://shop64171919.taobao.com

LZ3014 USB3.0开发板(CYUSB3014),请访问我的淘宝http://shop64171919.taobao.com

实体店铺:北京新中发电子市场2557号

良子.2012年

沈阳市东陵区白塔街龙盛家园

欢迎交流:liangziusb@163.com

QQ:2687652834

/4

/4

liangziusb_940932268 2012-1-10 15:00

用户1696769 2012-1-10 08:49

用户339122 2011-5-30 22:33