译者的话:很多同学可能对半导体尖端制造工艺更感兴趣,毕竟 5nm、3nm 这些词听起来就格外的一颗赛艇。不过行业不是整天在说“摩尔定律停滞/放缓”吗?大体上说的就是晶体管器件微缩的速度变慢了,那么驱动整个电子科技行业的底层技术也就变慢了,做不到 12-18 个月单位面积的晶体管数量翻番。

几年前就看到有人提出 More than Moore 还有“超越摩尔”之类的市场营销词汇。包括现在有像 Synopsys 这样的 EDA 公司提出 SysMoore 从系统层面来延续摩尔定律。其实这些都离不开先进封装工艺的发展。

“封装”“封装”,应该是说把芯片给密封、包装起来把?放在纸盒子里?一般我们说,“封装”要达成的是对芯片的支撑和机械保护,以及把电信号从芯片上引出来。在封装技术上做文章,也就是现在我们常说的“先进封装”工艺,应该是当代半导体制造技术发展的一个主旋律。

所以我预计会翻译 4-5 篇这方面的技术文章,个人感觉都还相对通俗易懂,且比较有科普价值的。期望对各位半导体技术爱好者有帮助吧。本文是此系列文章的第一篇,我觉得可以作为先进封装技术的一个概览,从“形式”上让各位同学对“封装”有个基本的概念。后面的几篇会做进一步的深入。

个人转载的请随意,但起码标明原文地址和我这个译者吧(毕竟我翻译的文章都有浓重的个人风味...)...

正文开始:

为什么现在封装技术很重要?

封装(packaging)原本是半导体制造流程后面的一道工序。将小片的硅造出来,然后用某种方法把它连接到什么板子上。随着摩尔定律的发展,工程师们认为应当充分利用芯片的各个组成部分、工序,包括封装,让最终产品达到最佳状态。采用更优的封装方式,能够带来很多好处,比如说更厚的金属片提供了更好的导电性,还有像是 I/O 问题——也仍是半导体产品需要考虑的最重要的问题之一。

只不过以前,封装企业并不像传统的前道(front-end)制造工艺企业那样受重视。封装供应链常被称作“后道”(back-end),被视为成本中心,类似于银行的前厅和后勤办公室的关系。但现在前道生产工艺的器件缩放进度放缓,那么新的技术热点也就随之转移,封装也就受到了重视。本文将讨论各种封装工艺,让你了解包括 2.5D、3D 封装等在内的概念究竟是什么意思。

封装简史

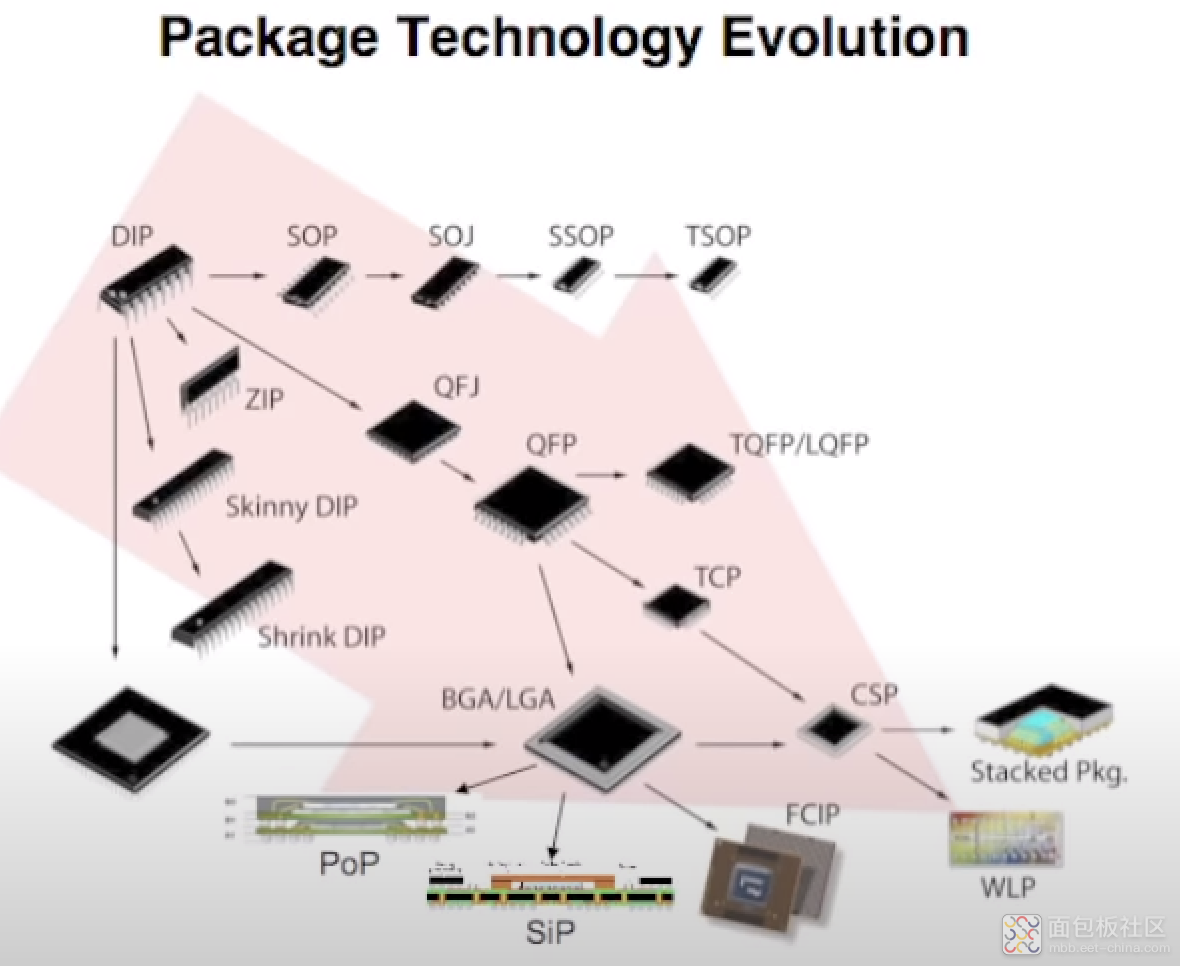

下面这张图是封装技术一个简单的层级关系,来自于某个油管课程。建议有时间的同学

前往观看。这个课程展示了封装技术从过去到现在的发展情况。

简单的进化路径 DIP > QFP > BGA > POP/SiP > WLP

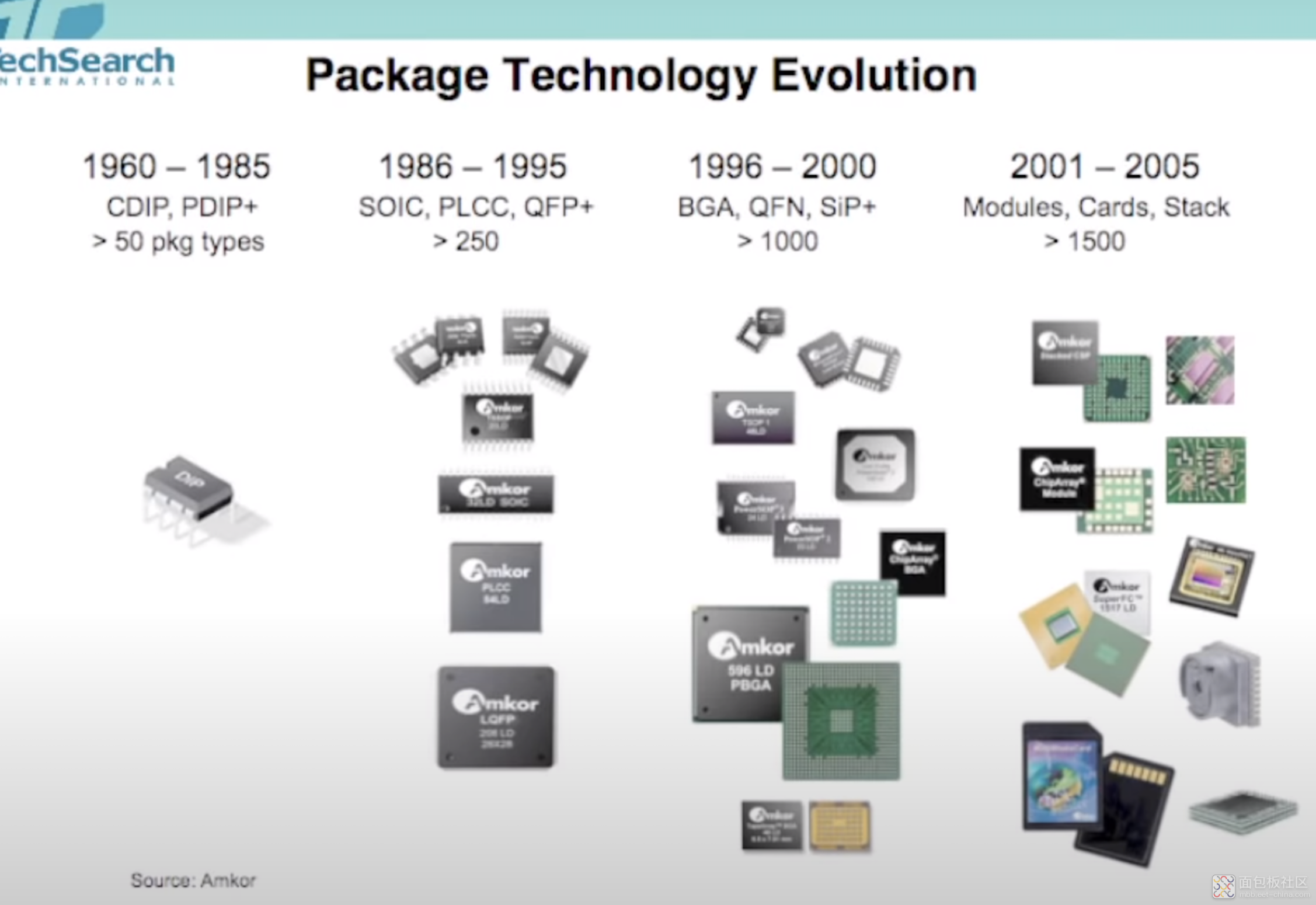

显然有挺多不同的封装技术的,不过我们只谈谈其中简单的一些——具有一定的代表性,然后再谈谈现在的一些技术。下面这张图作为高层级的一个总揽,也相当不错,虽然这张图有些过时了,但内容上没什么问题。

在封装技术发展初期,陶瓷、金属罐(metal cans)很常见;密封以达成最佳可靠性。这类方案绝大部分应用于航天、军用领域——这些领域的可靠性要求非常高。不过这样的要求对于日常民用设备而言就没有必要了,于是我们开始采用塑料封装以及 DIP(dual in-line packaging,双列直插式封装)。

DIP 封装(1964-1980s)

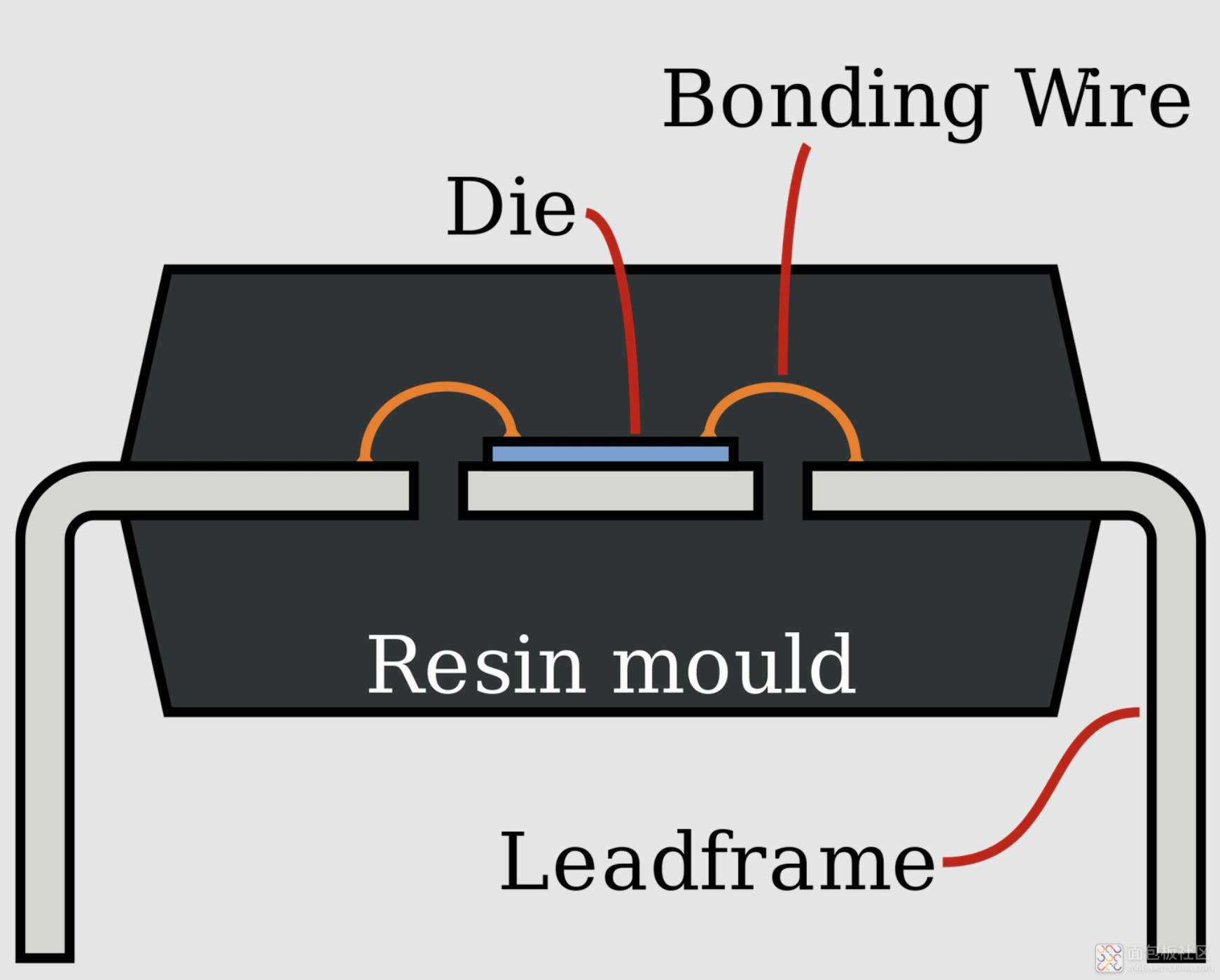

DIP 最早是在 20 世纪 70 年代引入的。在表面贴装技术出现以前,DIP 在大约 10 年的时间里成为一项标准。DIP 采用塑料外壳,包围半导体器件;有两排伸出的 pin 脚——名为引线框(leadframes)——连接到 PCB 板,如下图所示。

内部的芯片 die 通过焊线(bonding wire)连接到两侧的引线框,引线框连接到 PCB 板

DIP 是于 1964 年由仙童半导体打造的。DIP 封装现在是具备了象征意义的,其设计方案在当时也比较好理解。Die 完全密封在树脂里面,达成较高的可靠性,且成本较低。早期不少颇具代表性的半导体器件都采用这种封装方式。Die 是通过引线连接到外部的引线框的,也就让这种封装方式称为“引线键合(wire-bonding)”,后文还将详细介绍。

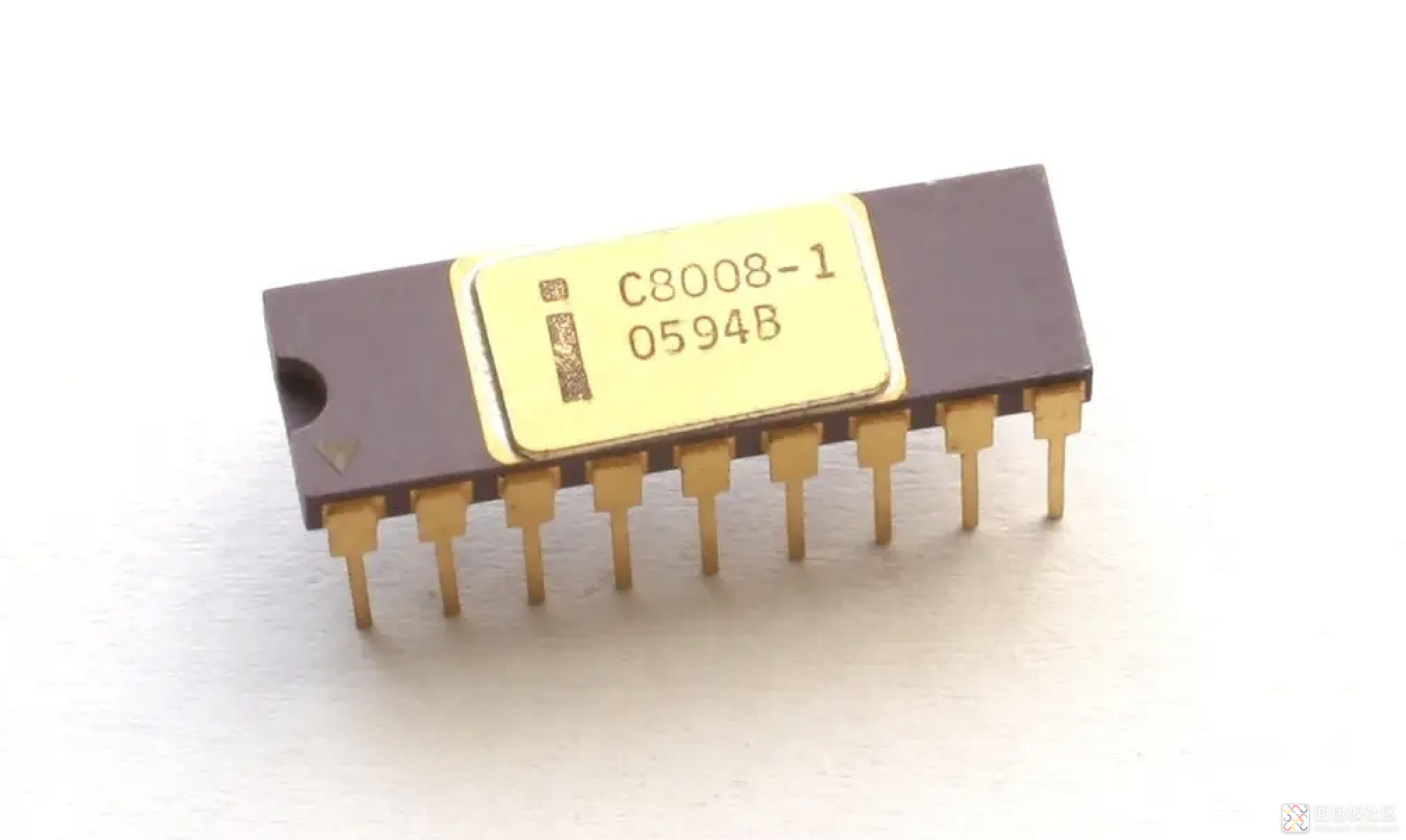

下面这颗芯片是 Intel 8008,应该是最早的一批现代微处理器了。注意这颗芯片就采用了具代表性的 DIP 封装。类似于这种看起来像蜘蛛形态的半导体器件,那就表明是 DIP 封装了。

Intel 最早的微处理器,8008 家族

这样的金属片会焊到 PCB 板上,令其与其他电子器件和系统其余部分连接。下面这张图展示的,就是焊到 PCB 板上的样子。

PCB 本身通常由铜和非导电材料层积而成。PCB 能够从不同位置导通电信号,实现 PCB 板上的器件互联互通。PCB 板上不同电路器件之间会有很精细的线路连接,这些线路嵌入在主板上,扮演着导管的作用。上图的这个模块自然是封装过后的器件,不过其实从系统层级来看,PCB 板也可认为是最高层级的封装形式。

DIP 的传奇故事当然不止于此,不过接下来我们就来谈谈下一个时代的封装技术:表面贴装(Surface Mount Packaging)吧。

表面贴装(1980s-1990s)

表面贴装简称 SMT。顾名思义,表面贴装是直接贴装到 PCB 的表面上。这样一来 PCB 板能容纳更多组件,单基板实现了更低的成本。下面这张图就是典型的表面贴装应用。

这种封装方案有很多不同的变体。在半导体创新发展的全盛时期,这样的封装技术在较长时间里扮演着重要角色。这里需要注意的是,原本 DIP 上的两排引线框,换成了 4 边都有了引线。值得一提的是,封装技术的发展,在于占据越来越小的空间,同时增大连接带宽。每次技术演进,都是期望在这方面做文章。

这项工艺曾经是手工完成的,当然现在已经高度自动化了。除此之外,这项技术其实也给 PCB 带来了不少问题,比如说 popcorning。Popcorning 是指塑料封装内部存在的湿气,在焊接过程中被加热,则导致在快速加热、冷却的过程里,PCB 产生问题。此处值得一提的是,每次封装工艺进步,都意味着复杂度在增加、出错率也在增加。

BGA 封装(1990s-2000s)

随着半导体性能持续进化,封装技术的要求也越来越高。在此期间 QFN(quad-flat no-leads,方形扁平无引脚封装)和其他表面贴装技术其实也在持续发展,不过我想介绍一下随后的封装技术——这些封装设计也成为后续技术发展的开端。首先是 BGA 封装(Ball Grid Array packaging,球柵阵列封装)。

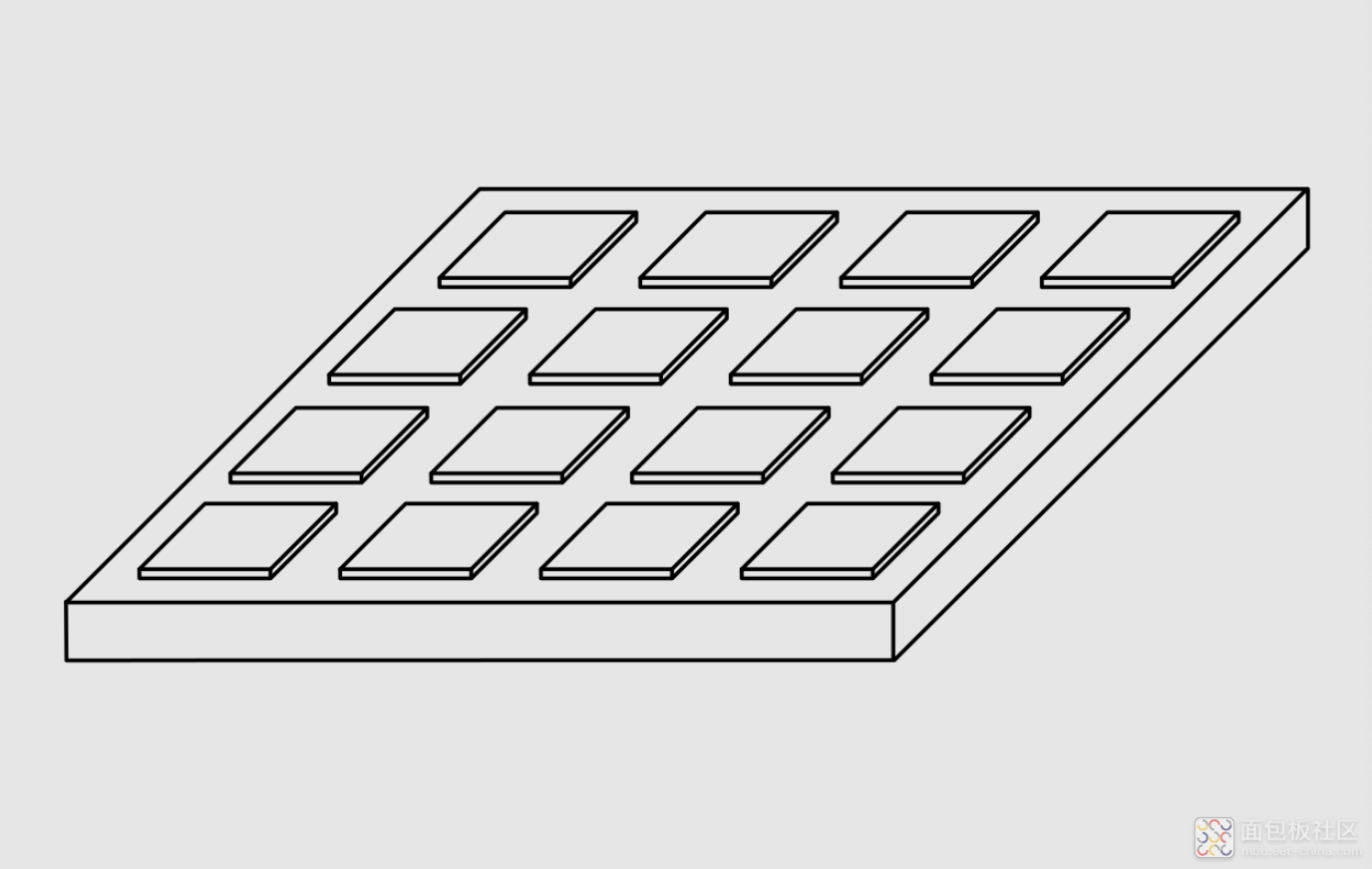

这些球或者说凸起,名为焊接凸点/焊球

这就是 BGA 球柵阵列的样子,可以直接把一片硅和 PCB 连起来,或者是连接到 PCB 板更下层的基板上,而不像之前的表面贴装技术那样只能局限在四边。

所以 BGA 封装本质上也属于封装技术发展的必然,即占据更小的空间、达成更多的连接点。BGA 封装是把一个封装模块直接连接到另一个模块(译者注:也就是 PCB)上,而不再是通过精细的连线。这样一来能够达成更高的密度、更好的 I/O 表现,与此同时也增加了复杂度——BGA 封装是否正常工作是需要仔细检查的。此前 BGA 封装需要从视觉上去观察和测试。现在我们已经看不到封装的样子了,需要藉由 X 光等更复杂的技术来进行检查。

像焊接凸点这样的方案,目前仍然是键合的一个主要技术,是模块之间互连最常见的类型。

现代封装(2000s-2010s)

接下来就该谈谈当代的封装技术了。其实前文谈到的不少方案今天依然在应用,只不过当代涌现出了更多的封装类型——其中的一些技术将来也会变得更普及。接下来我就谈谈这些技术。需要指出的是,其中的一些技术其实在很多年以前就已经发明出来了,但受限于成本,此前一直没有广泛应用。

倒装芯片(Flip Chip)

这应该是现在你们经常看到或者听到的一种常见的封装技术。很高兴我能在这儿给倒装芯片下个定义,因为我还从来没有在别的地方看到对这项技术满意的解释。芯片倒装是由 IBM 发明的,经常被简写成 C4。实际上芯片倒装并不是一种独立的封装形式,它描述的是某一种封装形态。它也需要搭配 die 上的焊接凸点。互连不是通过引线键合达成的,而且在封装的时候,芯片是翻转过来,面朝其他芯片;两者中间当然需要连接介质;所以被称作“倒装”芯片。

这句话可能还是很费解,所以我打算举个例子——来自维基百科,我觉得是比较好理解的。我们来谈谈这其中的步骤。

1.首先 IC 从晶圆上造出来;

2.芯片表面形成金属层的 pad;(译者注:原句为 Pads are metalized on the surface of the chip)

3.Pad 上沉积出焊接点;

4.把芯片从晶圆上切下来;

5.把芯片倒过来,如此一来这些焊接球就面向了电路;

6.焊接球再度融化;

7.然后再填充绝缘的胶粘剂

(译者注:个人感觉这个解释仍然不够完备,尤其是没有解释为什么要这么做,以及到底什么样的芯片用了倒装方案。实际上我们现在所见的很多基于尖端工艺的芯片,比如 Intel 酷睿处理器基本都是芯片倒装。另外,某些企业也将芯片倒装称作“先进封装工艺”...这部分将在未来翻译的文章里做更详细的解释...)

引线键合

注意倒装芯片和引线键合(wirebond)是不同的。还记得上面的 DIP 封装吗?那就是基于引线键合,die 藉由引线连接到另一片金属上,最终焊接到 PCB 板。引线键合已经不是某一种特定的技术方案了,而是一类技术的统称,可以衍生出各种不同形态的封装方案。我认为,这是描述倒装芯片最好的方法。引线键合相对于倒装芯片而言,是某种前置技术(译者注:原句为 Wirebond is a precursor to filp-chip to be clear;这句话可能也是着重在表达这两个词是不同层级的描述方式)。

这部分了解到这个程度也就可以了。实际上每种形式的封装方案都有不同的变体。顺带一提,KLIC(库力索法半导体)是这一领域的市场领导者,谈到旧封装技术,就应该想到这家公司。

先进封装(2010s 至今)

进入“先进封装”半导体时代还是相当漫长,我期望谈谈某些高层级的概念。这里面其实有多个层级的“封装”要谈。前面我们在谈的绝大部分封装,是专注在芯片到 PCB 的封装;而先进封装要从手机开始说。

从各个层面来看,手机都可以说是先进封装诞生的巨大前提。这其实也很合理,毕竟手机是以那么小的体积装下那么多的晶体管和硅相关技术,比笔记本和电脑密集多了。而且一切都需要被动散热,还必须尽可能地薄。每年苹果和三星都会发布性能更强、但外形更薄的手机,这也就驱动了封装技术的发展。我下面要谈的很多概念都是从智能手机封装开始的,并且最终将这样的技术在半导体行业的更多应用上普及开。

芯片级封装(Chip Scale Packaging,CSP)

芯片级封装描述的范围其实比较广,原本的意思是达到芯片尺寸的封装。其确切定义应该是描绘某一个封装模块,其尺寸不大于内部 die 尺寸的 1.2 倍,必须为单 die 且可连接。前面其实已经引入过 CSP 的概念了,就是在倒装芯片的部分。不过 CSP 还是藉由智能手机,将技术带到了新的高度。

本世纪 10 年代,CSP 几乎成为一种标准;上面这张图的一切封装尺寸,都大约是芯片 die 尺寸的 1.2 倍左右,极尽所能地节约占板面积。CSP 也有多种不同类型,包括倒装芯片、right substrate(?这是啥,欢迎评论补充)等其他技术。不过其实知道其中细节对你们应该也不会有多大帮助。

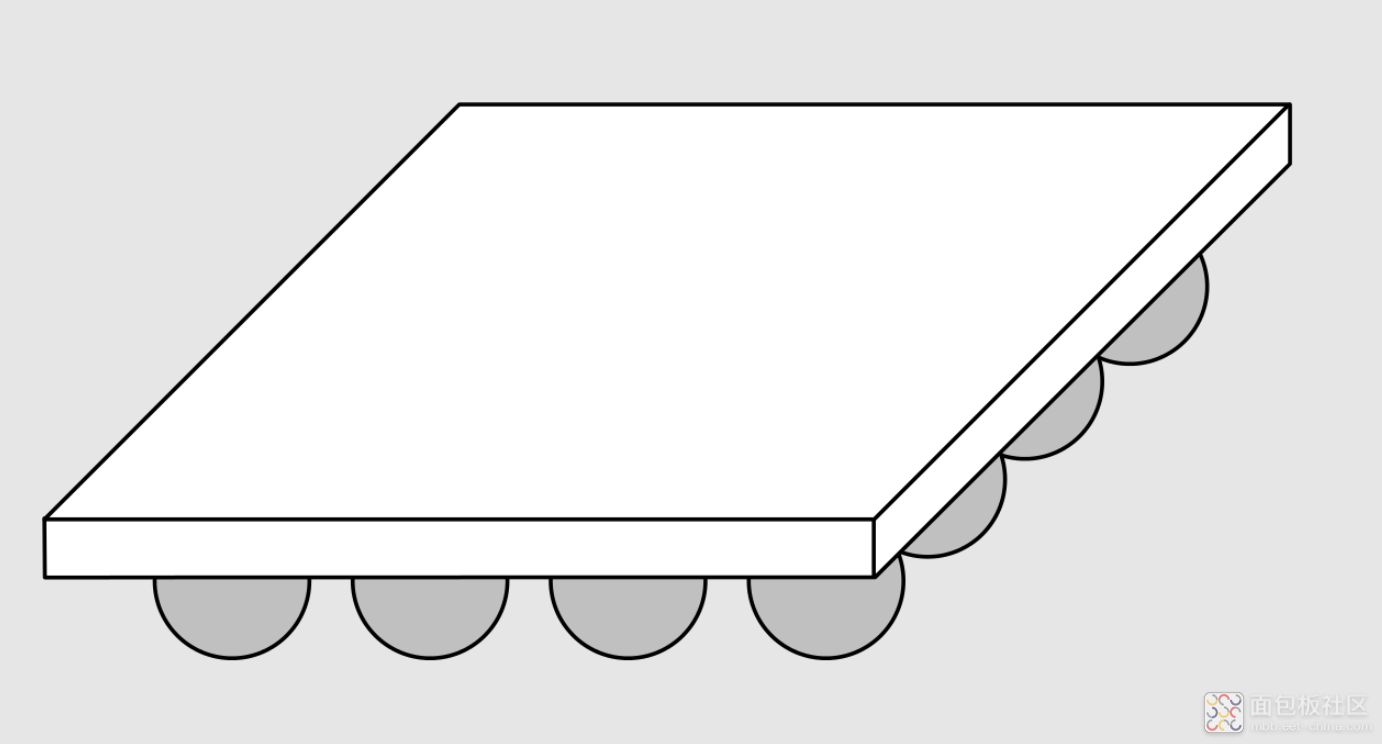

晶圆级封装(Wafer-level packaging,WLP)

这里其实还有一种更小的方案,属于“终极版”芯片级封装尺寸,或者可以叫晶圆级封装。基本上就是将封装直接放到 die 身上;在此,封装就是 die 本身。它比最高层级的 I/O 还要薄,显然也非常难于制造。先进封装解决方案当前仍在 CSP 级别,但未来将完全转向晶圆级。

这样的进化方向很有趣,封装某种程度上是被硅包含在内了。芯片即为封装,封装即为芯片。这样的方案比在芯片上焊个锡球就贵多了,那为什么还要用这样的方案呢?为什么我们还在追求高级封装呢?(译者注:个人感觉,这番解释还是有点问题)

先进封装:未来

这也是我之前一直在说的一个趋势。异构计算并不仅是架构专用化,还在于怎么将这些专用芯片放到一起。先进封装就是其中非常关键的技术。

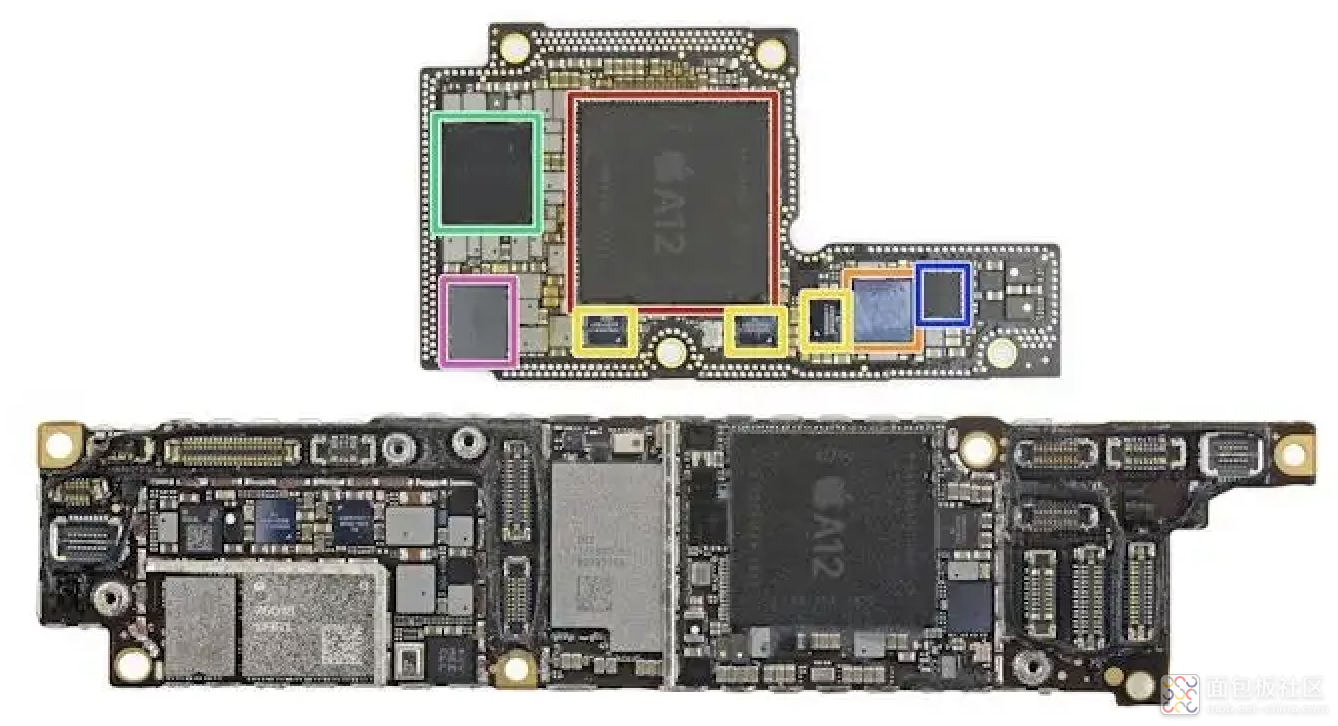

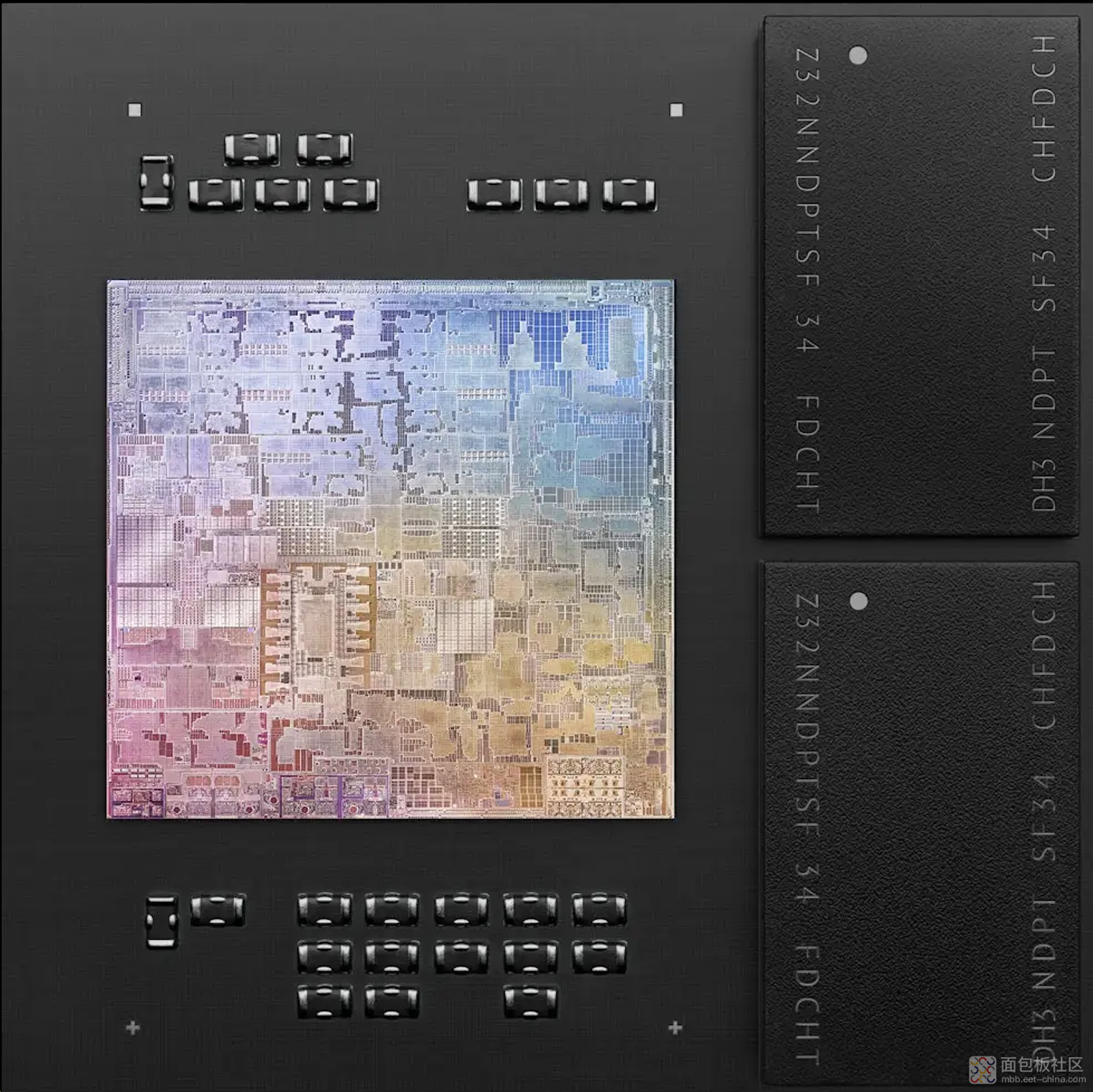

我们来看看苹果 M1 芯片,典型的异构计算芯片,而且还配了统一内存架构。M1 出来的时候,我并没有感觉到多惊讶,它只是异构计算的典型代表。M1 的确表明了未来的方向,很多芯片设计也将很快追随苹果的方案。SoC(System on Chip)本身并不能说是异构,但采用定制化的封装方案,把内存放到 SoC 旁边就是异构了。(译者注:对这个说法深表不赞同)

这张图虽然是宣传图,但注意 PCB 上没有出现引线,应该是因为 2.5D 集成的关系(译者注:个人认为,这个说法应该也不对;苹果的这种统一内存充其量就是从基板走线的 2D 封装)

先进封装方案中比较具有代表性的另一个产品是英伟达 A100,注意 PCB 板上同样没有出现引线。

下面这段话来自英伟达的白皮书:

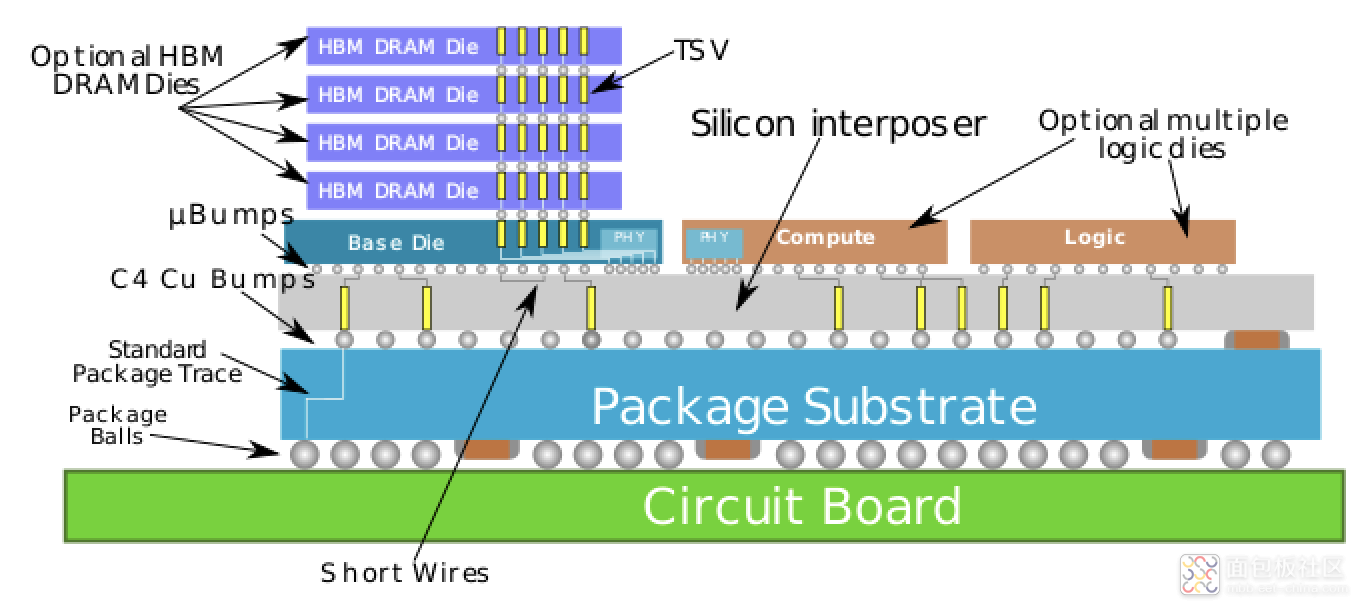

A100 并没有像传统方案那样,在 GPU 芯片周围放上好几个独立的内存芯片(如 GDDR5 GPU 显卡设计),而是采用 HBM2 内存——这种内存本身在垂直方向就叠了多个内存 die。这些存储 die 通过一些很微小的“线”连接起来(基于 TSV 硅通孔和 microbump 微凸点)。1 个 8Gb HBM2 die 包含超过 5000 个 TSV 孔。然后再用一层有源(passive)硅中介(silicon interposer),把内存堆栈和 GPU die 连起来。HBM2 堆栈、GPU die、硅中介一起,装到一个 55mm x 55mm BGA 封装中。图 9 展示了 GP100 加上两个 HBM2 堆栈;图 10 则展示了 P100 的 GPU 和内存微观图片。

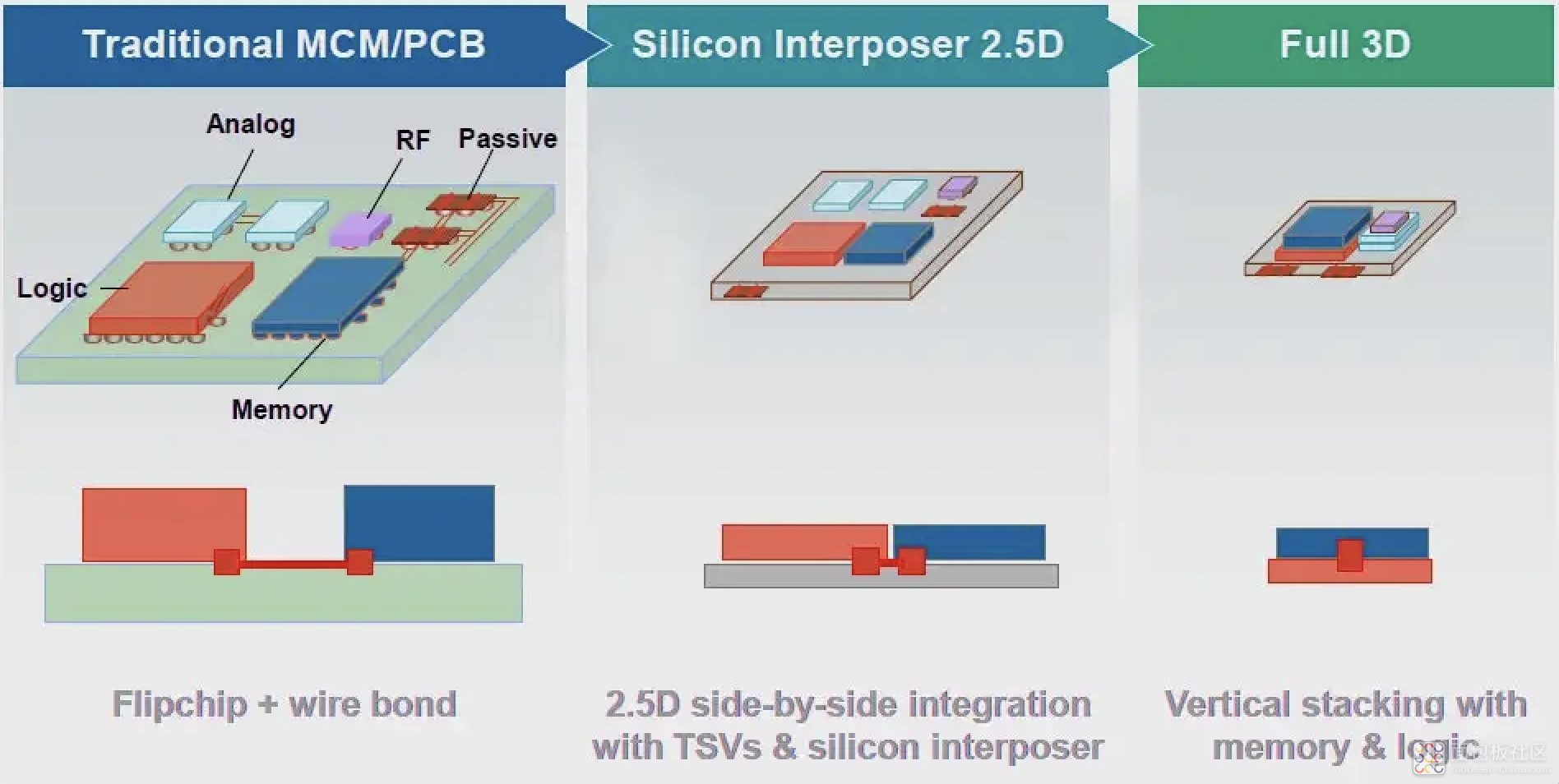

我们把这段话变成人话,首先要谈谈“高级封装”的两个类别:“2.5D 封装”和“3D 封装”。

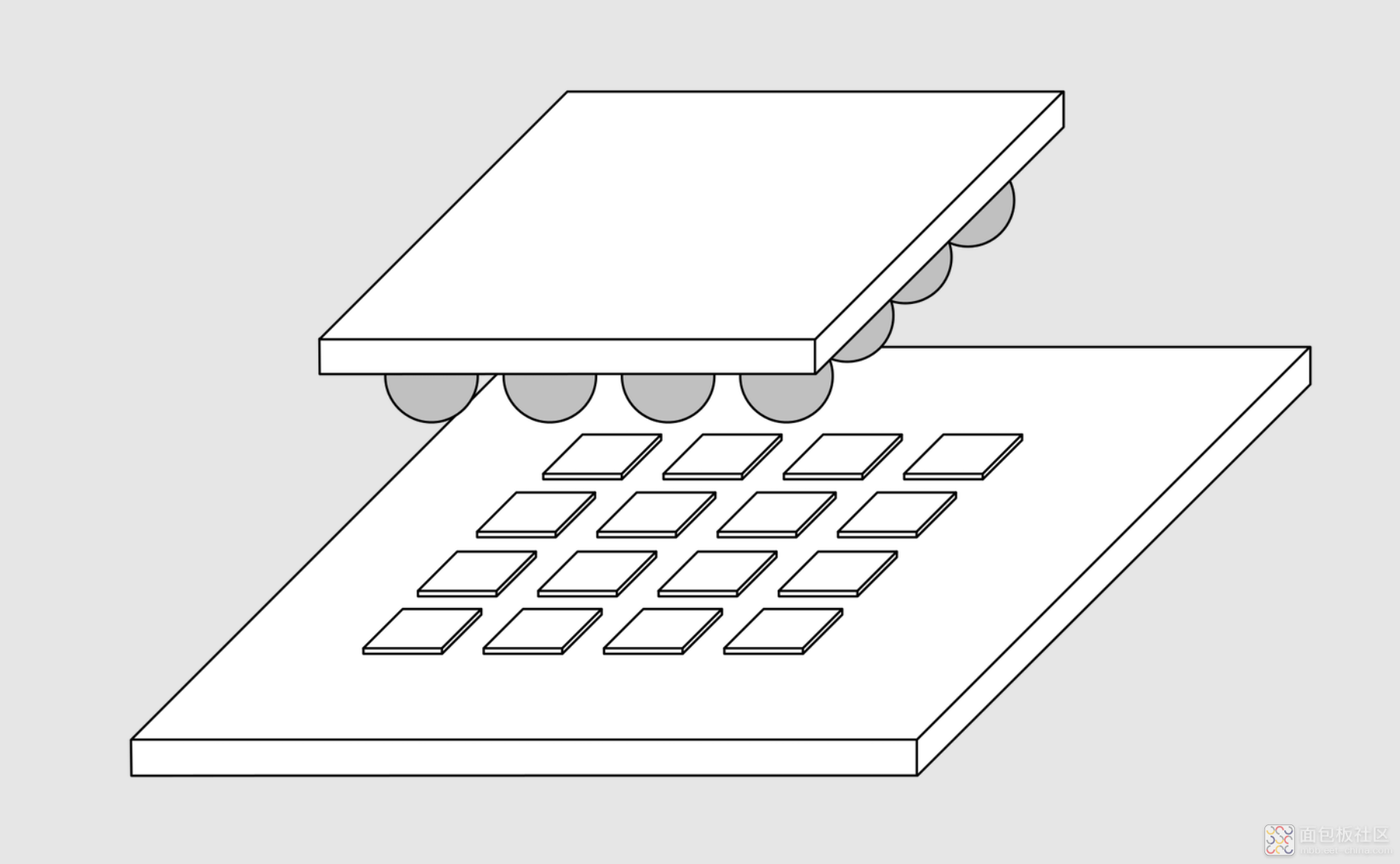

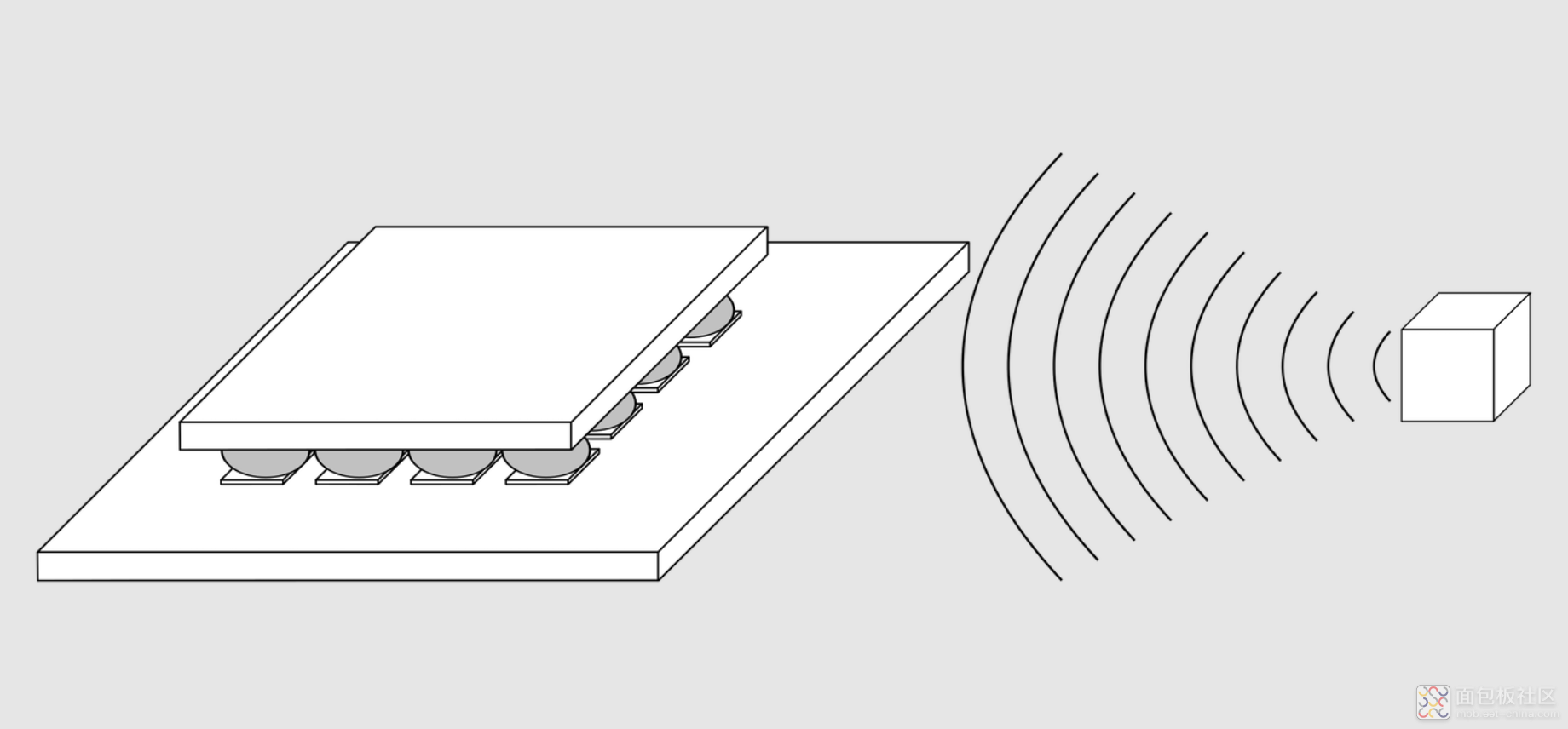

2.5D 封装

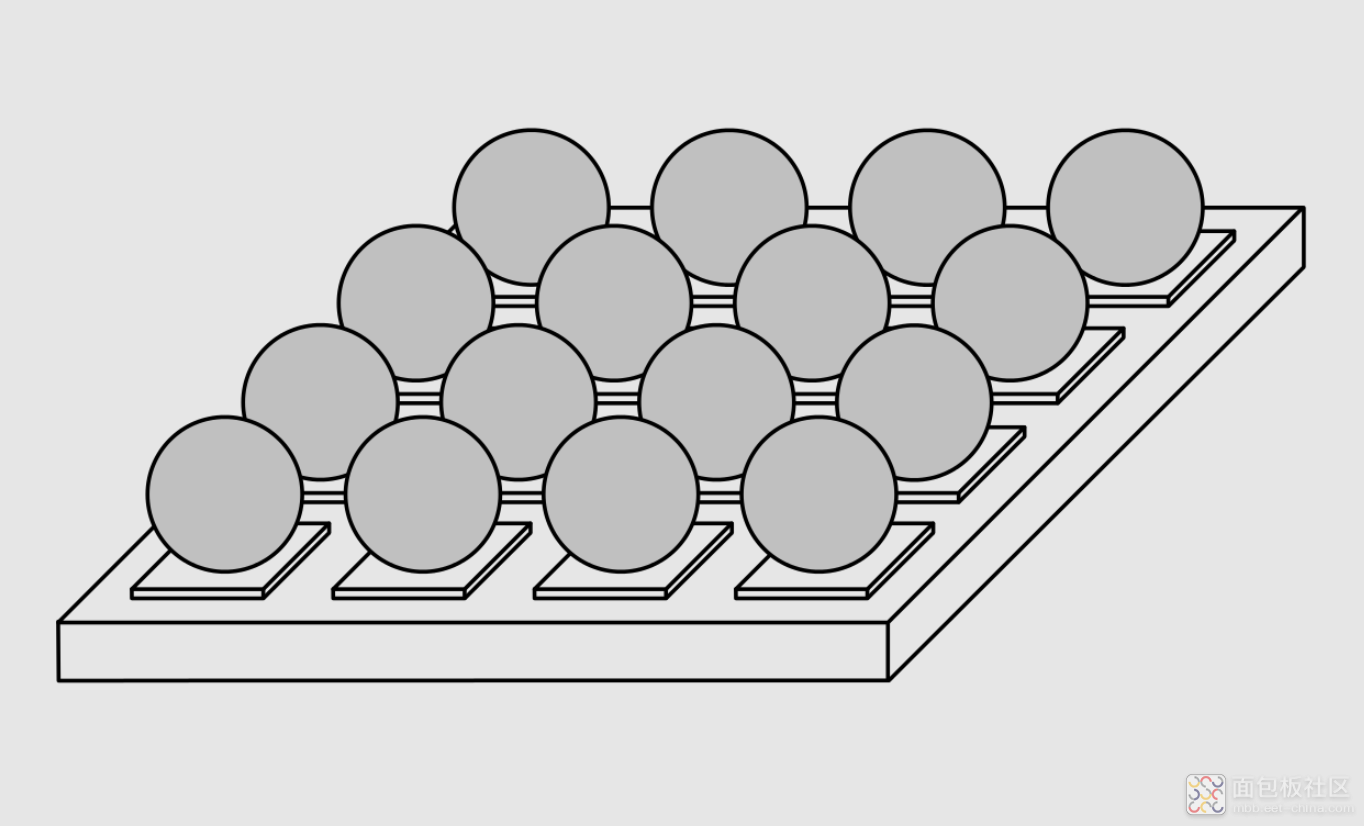

2.5D 本质上属于倒装芯片的升级版本,不过不是将 die 堆在 PCB 板上,而是把多个 die 放在一层叫做“硅中介(silicon interposer)”的东西上面。下面这张图应当很好地解释了这个方案。

2.5D 就类似于开了个地下通道,通到邻居家里;实际上这个“通道”是藉由凸点(bump)或者 TSV 硅通孔深入到硅中介,然后通过硅中介把你和你的邻居连起来。这种方案在速度上当然不会比直接在芯片内部通信更快,但其输出表现取决于封装性能,两颗 die 之间的距离缩短、连接点增多。其价值还是比较大的。其中一个好处在于可以用“known good die”,或者说把更小片的 die 封装到一起,形成一个更大的封装。之所以这么做会比 1 整片 die 的方案要更优,是因为它让制造变得更容易了,毕竟只需要造小尺寸的 die。

这些小片的 die,常被称为 chiplet(译者注:国内有译作“芯粒”的),你们应该也常听到。如此一来,把较小功能模块的 chiplet 组合到一起,在一块硅基板上对这些 chiplet 进行连接,就构成了 2.5D 封装的芯片。

Chiplet 和 2.5D 封装可能还会应用较长的一段时间。它在各方面都有优势,比如质量、相比 3D 封装工艺更简单,而且成本也更低。另外,这种技术也具备了弹性,比如复用新的 chiplet,通过替换 chiplet 的方式把全新的芯片带到相同的封装之上。AMD Zen 3 就是一个例子,封装本身是类似的,chiplet 可做扩展。但还有个终极版本,3D 封装。

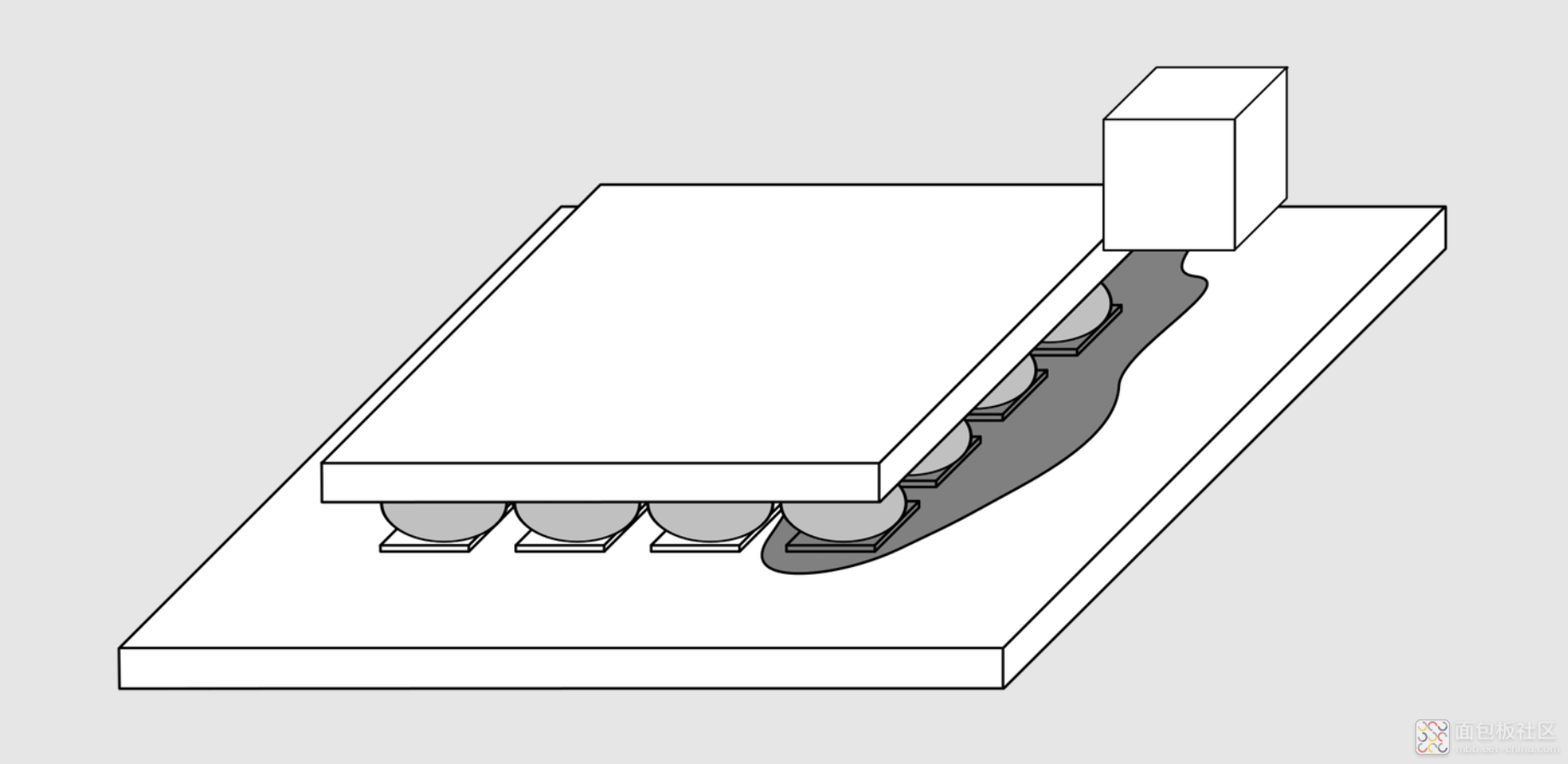

3D 封装

3D 封装乃是封装的超级形态(ultimate ending)。前面谈到的那些封装,其实都是把房子建在地上、一层楼高,然后通过地下室相连;而 3D 封装则是建高楼,按照功能需要做定制化。这就是 3D 封装,封装都建基于 die 本身。这是最快,且具备了能效比的方法;而且用这种方法能够打造规模更大、更复杂的结构,大幅“扩展”摩尔定律。未来或许要实现器件尺寸微缩会有很大的难度,但有了 3D 封装,就能延续摩尔定律。

其实整个半导体市场,已经有了 3D 堆叠的示范:存储器。3D 结构的存储就属于未来的写照。NAND 发展为 3D 结构的原因就是器件尺寸微缩难度变得很大。把存储介质想象成大型的 3D 高楼,每一层都通过电梯相连——也就是 TSV 硅通孔。

这就是未来的样子,甚至有可能把 CPU、GPU 相互叠起来,或者把存储堆栈放到 CPU 上面。这是最终的发展方向,而且我们很快应当就能达成这个目标。我们应该在未来 5 年内就会看到各种 3D 封装芯片的涌现。

2.5D/3D 封装解决方案一览

我不打算深入去谈 3D/2.5D 封装,还是展示一些已经在用的封装工艺会比较好。我想专注在 fab 厂的工艺上,这些也是驱动 3D/2.5D 集成往前发展的一些技术。

台积电 CoWoS

这应该是 2.5D 集成工艺的主力技术,赛灵思是采用该技术的先驱。

这项工艺主要是把所有的逻辑 die 放到一片硅中介上,然后再放到封装基板(package substrate)上。其上所有组成部分都通过 microbump(微凸点)或者焊球来连接。这是比较典型的 2.5D 结构。

(译者注:这里其实如果能够列举硅桥方案会更好。因为并非所有的 2.5D 封装都需要藉由硅中介来实现。不过未来高级封装技术的系列文章还是会仔细去谈这个部分的)

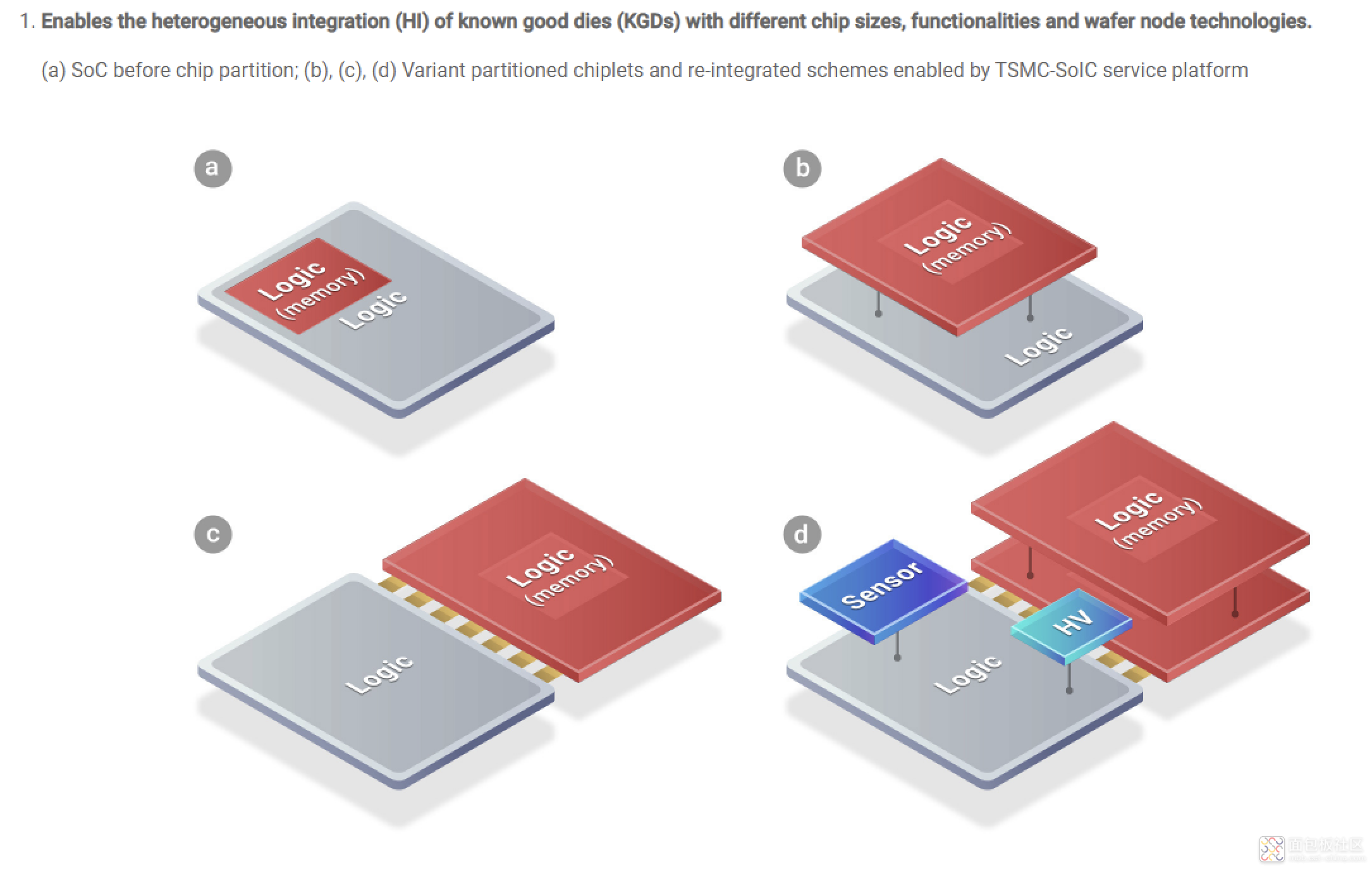

台积电 SoIC

这是台积电的 3D 封装平台,属于比较新的技术。

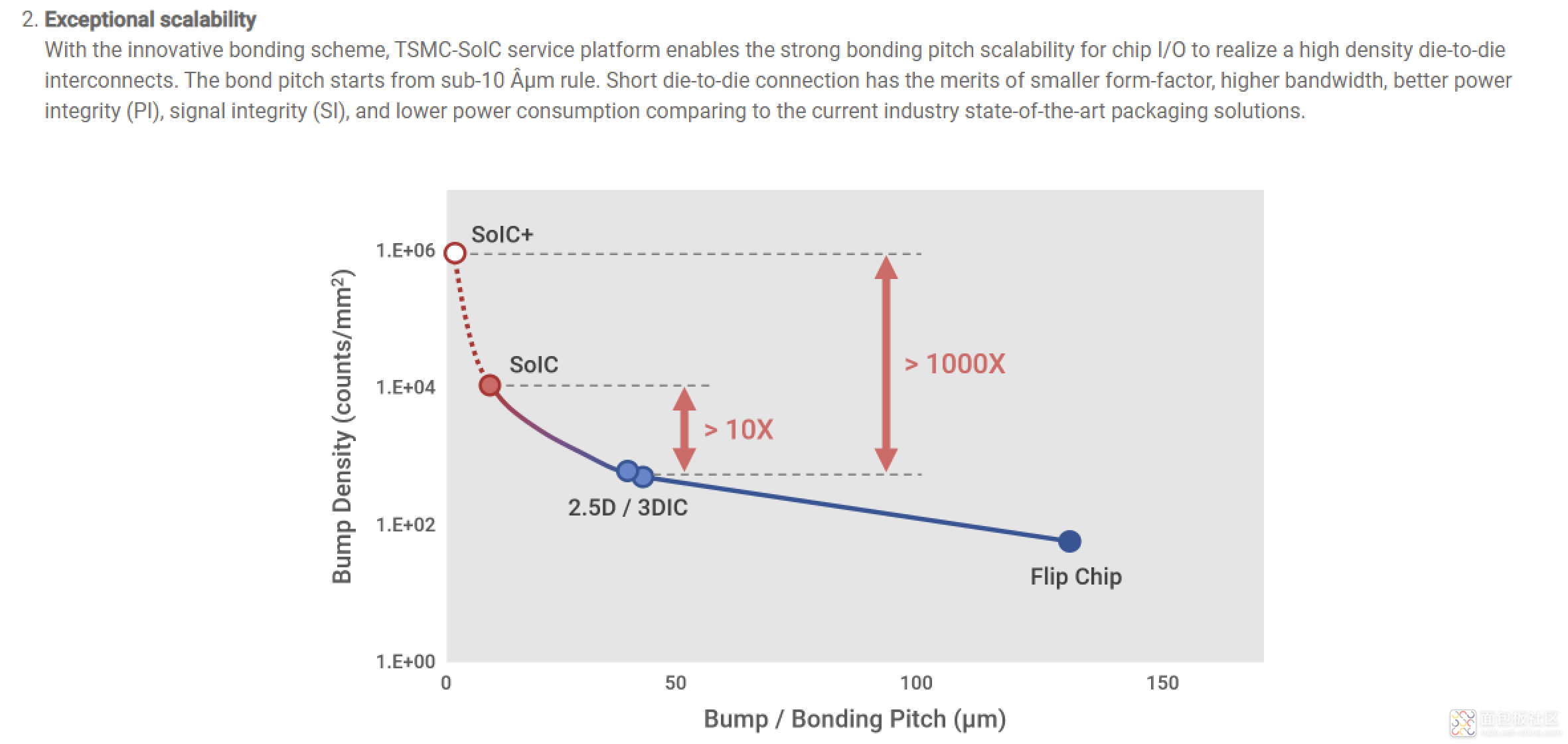

注意下图中的 bump 密度和键合间距(bonding pitch),SoIC 的这两个参数与倒装芯片/2.5D 封装相去甚远,基于密度和尺寸都属于前道工艺。

下面这张图则对其技术做了对比,SoIC 的确实现了芯片之间的堆叠,而不单是通过硅中介来实现 2.5D 集成。

三星 XCube

三星这些年也成为很重要的 foundry 厂,

这则视频是其 XCube 技术的展示。

这则视频呈现的信息其实不多,不过要指出的是英伟达 A100 就是基于三星的这项工艺,这应该也是英伟达最近的一些芯片采用的技术方案。另外值得一提的是,三星可能是在 TSV 硅通孔技术上经验最多的企业,毕竟他们在 3D 存储平台上积累颇多。

Intel Foveros

最后要谈的是 Intel 的

Foveros 3D 封装。未来我们应该还会看到更多这项技术的身影,尤其是 Intel 未来的 7nm(译者注:已更名为 Intel 4)及其 CPU 混合架构。Intel 也在 Architecture Day 上谈到了这会是他们未来发展的重点。

(译者注:这里之所以提到混合架构,也就是一般人所说的大小核设计,是因为 Intel 最早的大小核芯片 Lakefield 其实就用到了 3D 堆叠,具体可

参见这篇文章;不过目前混合架构的 Alder Lake 并没有采用这项封装技术)

比较有趣的是,其实三星、台积电、Intel 在 3D 工艺方面的差别并不是特别大。(译者注:对这一说法持严重怀疑态度)

先进封装的赢家

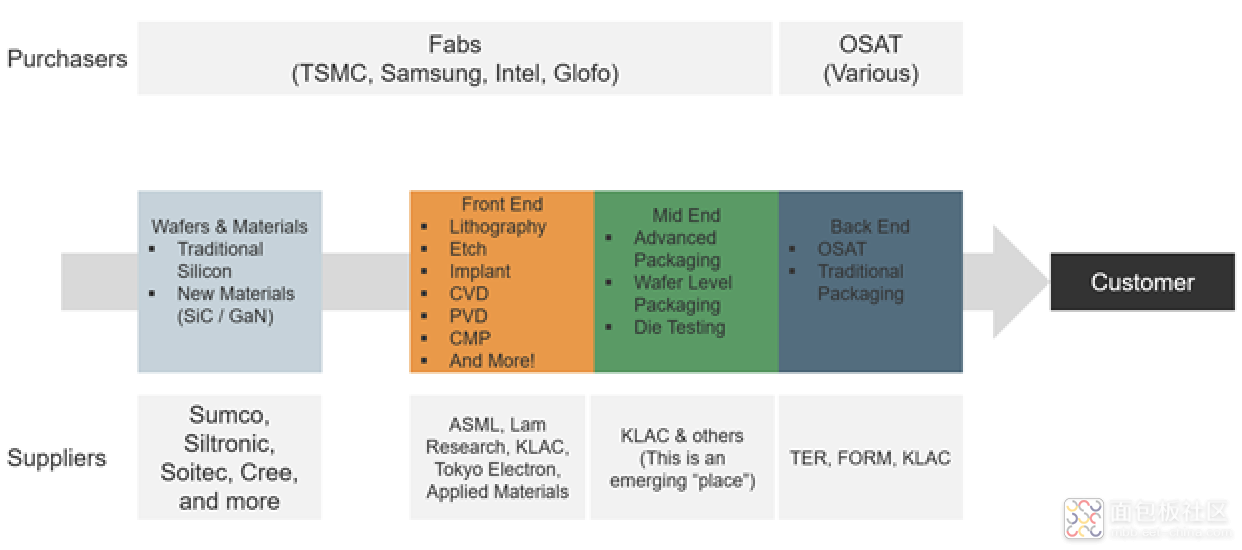

先进封装,在流程中实际上属于“中道(mid-end)”技术(译者注:mid-end 是相对于 frond-end 和 back-end 而言的,如下图所示)。技术本身是在发展中的。

以前,封装预算是被排除在 WFE(Wafer Fab Equipment)预算之外的;但从 2020 年开始,也开始把晶圆级封装包含在内。这本身就是风向变化的一个信号,以及中道工艺变得重要的原因。中道的另一个定义是 BOEL(Back End of Line)。要了解封装相关企业信息,可以

参见这篇文章。

/2

/2

乖乖兔爸爸 2022-5-6 10:09