磨蹭了好久,终于把这个信号分析的教学仪表做好了。

系统功能

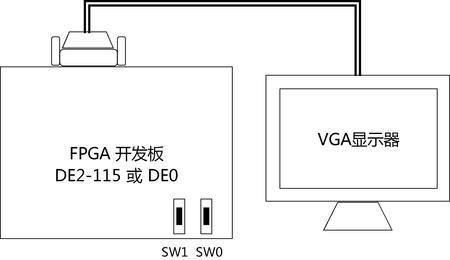

- 如下图所示, 本系统由一块型号为DE0或DE2-115的FPGA开发板、 一个VGA接口的显示器组成。

- FPGA开发板内部自行产生数字信号波形, 再由其内部的软硬件协同进行处理与分析, 最后在VGA显示器上绘制信号分析结果。

- 该系统通过两个拨码开关对电路进行控制。

- SW0,拨到“上方”, 电路进入复位状态

- SW0,拨到“下方”, 电路进入工作状态

- SW1,拨到“上方”, 信号触发捕获被使能

- SW1,拨到“下方”, 信号触发捕获被禁止

FPGA内部电路结构

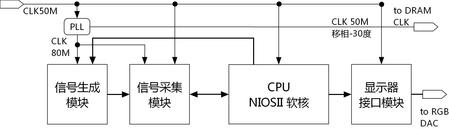

如下图所示,FPGA内部电路由以下模块构成

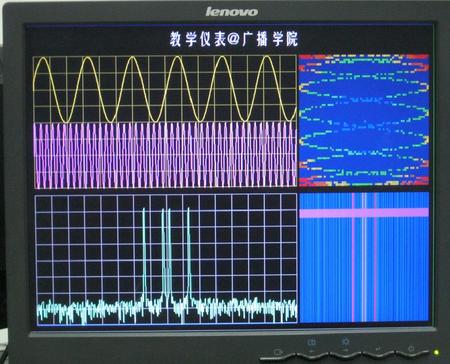

- 信号生成模块: 根据处理器的配置, 生成2通道频率、 相位可独立调节的正弦信号。

- 信号采集模块: 外部拨码开关使能开启时,根据处理器的配置, 根据触发条件对输入信号进行采集, 缓冲区采满后, 置位标志寄存器, 通知处理器读取数据。

- 处理器软核: 配置各个外部模块, 读取采集的信号数据, 对数据进行分析和显示适配处理, 然后将显示数据写入显示器适配模块。

- 显示器接口模块: 将处理器写入的波形和显示数据, 根据VGA时序绘制在显示器上。

- 时钟方案: 外部输入晶振50MHz,作为CPU和显示器接口模块的时钟,信号生成模块工作在80MHz的时钟下,信号采集模块为双时钟,用于跨域时钟域。FPGA外部的SDRAM时钟由PLL移相生成。

软件结构

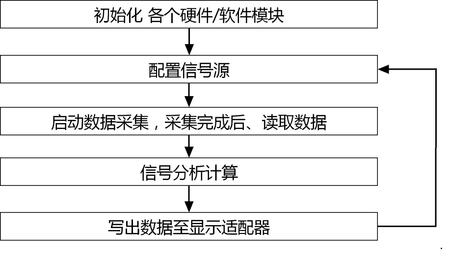

- 本设计的软件工作流程如下图所示。

- 系统上电复位之后, 处理器对各个软件、 硬件模块进行初始化, 然后进入工作循环。

- 工作循环任务如下:

- 首先对信号产生电路的参数进行配置, 然后启动信号采集模块, 并且监测信号采集模块的状态位信息

- 一旦数据缓冲区采满, 则读取所采集的信号数据, 进行后续的时域、频域信号分析运算

- 由于信号的采集长度, 分析长度, 以及显示器绘图区域的像素尺寸可能存在差别

- 所以为了适合显示环境, 还需再对信号分析的结果数据进行显示适配计算, 最后将数据写出至显示器接口电路。

用户325709 2014-3-10 12:01

用户1104806 2013-11-1 10:05

用户178636 2013-8-30 23:06

用户308762 2013-1-21 16:15

用户235364 2012-10-30 20:25

用户1666663 2012-10-30 19:39