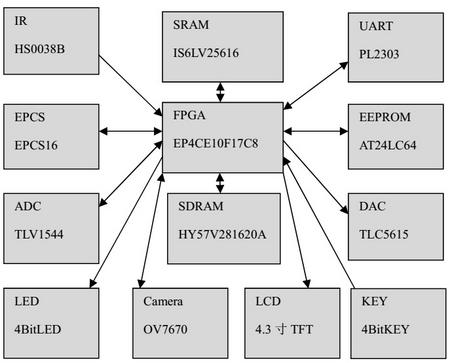

由于没有合适的FPGA开发板,小梅哥的实验一直做的很艰难,同时看到很多同学在咨询什么样的开发板适合学习和使用的问题,我们计划推出一套低成本的FPGA开发套件,该套件初步架构设计如下。

功能介绍:

IR:红外遥控接收头,进行红外遥控的解码,做键盘扩展用,另外将该脚引出,可做扩展键盘接口;

EPCS:FPGA配置芯片,可能会考虑采用串行FLASH芯片;

ADC:10位ADC芯片,4通道,做数据采集用;

LED:状态指示用;

SRAM:高速缓存,做高速数据采集、处理、或液晶显存用;

FPGA:;

SDRAM:大容量缓存,做NIOS II存储器,或高速数据缓存用;

Camera:摄像头;

LCD:4.3寸TFT屏,作为界面现实用;该接口和正点原子的TFT接口兼容,可适配其各类尺寸液晶。

Key:按键输入;

DAC:数模转换芯片;

EEPROM:IIC接口存储器;

UART:usb串口芯片,负责和上位机进行通信。

引脚预测:

|

|

in |

out |

|

IR |

1 |

|

|

EPCS |

|

|

|

ADC |

2 |

4 |

|

LED |

|

4 |

|

SRAM |

39 |

|

|

SDRAM |

39 |

|

|

Camera |

14 |

|

|

LCD |

28 |

|

|

KEY |

4 |

|

|

DAC |

|

3 |

|

EEPROM |

2 |

|

|

UART |

2 |

|

共计消耗引脚142个,EP4CE10F17C8N可用用户IO最多为180个。

EP4CE10F17C8各Bank可用引脚统计:

|

|

in |

out |

IO |

|

Bank1 |

0 |

0 |

12 |

|

Bank2 |

|

|

17 |

|

Bank3 |

|

|

26 |

|

Bank4 |

|

|

27 |

|

Bank5 |

|

|

23 |

|

Bank6 |

|

|

12 |

|

Bank7 |

|

|

26 |

|

Bank8 |

|

|

26 |

|

时钟 |

7 |

|

|

|

共计 |

7 |

0 |

169 |

因此,实际用户可用IO有176个,另外四个IO被用作配置功能,用户不可直接使用。

因此,还余下34个空闲IO,此部分IO将全部引出,以作扩展IO使用。同时,SRAM占用的39个IO中,除CS外,其它IO也将全部引出,当系统不使用SRAM时可做扩展IO使用。Camera的14个引脚也将全部引出,以作扩展功能使用。扩展接口会充分考虑到正点原子STM32开发板及其配套模块的设计,力争做到兼容,为希望学习的各位节约大量开支。

此板预计做成体积大小为4.3寸TFT大小的核心板,通过此板,可完成EDA实验和SOPC实验。

目前规划的实验主要有以下几个:

后期将会考虑推出推出基于AD9288的高速ADC板卡,和基于AD9708的DAC板卡,实现较高速的示波器和数控信号发生器实验。同时推出USB接口板,实现与PC机的高速通信。

另外,为了方便初学者学习FPGA技术,我们将会根据大家的意见,设计对应的扩展底板,以方便大家的学习。

以上为我们团队考虑要实现的方案。如果大家感兴趣,有更好的建议,欢迎回复留言,我们将充分考虑每一位读者的意见,权衡后推出该板卡。

莫问奴家名 2015-1-8 19:35

用户1779744 2014-12-8 16:13

用户417079 2014-12-8 10:00

小梅哥 2014-11-23 15:15

用户1635984 2014-11-23 13:24

小梅哥 2014-11-11 17:13

小梅哥 2014-11-11 17:11

用户413003 2014-11-11 14:20

用户377235 2014-11-6 08:22

小梅哥 2014-11-1 15:09