基于FPGA的TDC设计中使用PLL来模拟HIT

概述

在进行基于FPGA的TDC设计时,为了测试方便,一般通过PLL来模拟外部“HIT”,这是进行码密度测试基本操作。通常的做法是需要FPGA片外提供两个非同源的时钟,一个用于系统时钟以及TDC的高速锁存时钟,另外一个用于产生模拟HIT。假如使用片内的PLL,那么就没必要这么麻烦了。

读本文之前,还可以参考之前博客:https://mbb.eet-china.com/blog/1010859-213148.html,https://mbb.eet-china.com/blog/1010859-213159.html

乘除因子的真相

图1:PLL框图

如图1所示为PLL的内部结构框图,那么所谓的PLL的乘除因子与内部的这些counter的关系如下所示:

其实我们在讲乘除因子的时候必须搞清楚PLL的几个counter,即M、N以及C计数器。首先我们可以确定的是Megawizard里“Clock multiplication factor”就等于M计数器的值,而“Clock division factor”等于N计数器的值乘以C计数器的值,这些可以从上述公式里找到答案。

在进行PLL输出时钟设置的时候,Megawizard一般不提供,且ALTERA也不建议客户直接去设置M、N以及C计数器,而是通过设置乘除因子来设置PLL,编译器会自动设置这些计数器的值。只有高级应用,即高级用户可以通过特殊方式来设置M、N以及C计数器来配置PLL。另外,应用ECO工具手动修改FPGA设计的时候也可以修改这些计数器以及其他参数。

一个TDC模拟HIT设计实例

有篇参考论文上提到过一个利用FPGA的PLL产生HITs的例子,其中有两个问题一直没弄明白。最近几天通过不断的做实验终于搞清楚了问题,特总结一篇记录与此以备后查。

整个例子如图2所示,外部给FPGA一个100MHz的时钟,第一个PLL由100MHz产生一个387.5MHz的TDC时钟。第二个PLL产生一个33.68MHz的HIT时钟。我所说的问题,第一是为什么20MHz时钟要从FPGA外面兜一圈;第二是作者给出两个PLL的输出时钟之间的相位关系有256种组合,而没有直接给出原因。

图2:关联校准脉冲发生器

首先谈第一个问题,由于作者没有给出其具体使用的器件型号,所以这里我猜测这个20MHz在FPGA外部兜一圈的原因也许是因为作者使用的器件的PLL不支持逻辑时钟作为其输入,而必须是从FPGA引脚来的时钟才能作为PLL的输入,而ALTERA早期的Cyclone系列就有此限制。另外,早期的ALTERA器件也不支持PLL级联,所以也没有从第一个PLL产生一个20MHz来驱动第二个PLL。还有就是《PLL那些事之乘除因子》一文中有提到PLL的输出受限于PLL的FVCO,所以第一个PLL输出一个387.5MHz时钟后,无法再输出33.68MHz或者20MHz。否则,图2完全可以只用一个PLL产生387.5MHz和33.68MHz这两个时钟。

接着谈第二个问题,即387.5MHz和33.68MHz这两个时钟之间为何相位关系就有256种组合呢?分别用CLKH和CLKL来代替387.5MHz和33.68MHz这两个时钟。根据图2,可以得到CLKH=100*,而CLKL=100**。因此将第二个等式代入第一个等式我们得到CLKH=CLKL*5**=CLKL*,反过来也就是2945*TH=256*TL,也即是说低速时钟和高速时钟有256种不同的相位关系组合,因为每256个时钟周期低速时钟和高速时钟关系重复一次。所以,图2所示的使用PLL在FPGA内部产生TDC的模拟HIT输入是可行的。图2所示的这些256种可能的脉冲平均分布在2580ps范围内,那么每两个相邻脉冲的时间间隔就是10.08ps,这个值可以通过求n*29687.5和2580的模来得到(29687.5ps是33.68MHz时钟的周期)。图2还显示了一种增加HIT和TDC时钟之间的时间关系可能性的办法,即通过相移90度得到另外一个33.68MHz时钟,这样模拟的HIT多出一倍,同理,通过改变相移可以继续增加HIT的种类。

改进型模拟HIT

图2所示的模拟HIT产生电路相对比较复杂,原因前面提到了,是由于器件本身限制造成的。笔者自己使用的ArriaGX系列FPGA,该系列FPGA的PLL支持片内级联。也可以通过一个PLL同时产生TDC时钟和模拟HIT时钟。实际应用的时候还是用到了PLL级联,这是因为产生TDC时钟的PLL在产生TDC时钟的时候其FVCO频率已经被确定下来,所以在现有FVCO频率下是否能产生合适的用以模拟HIT的时钟还需认真考虑。

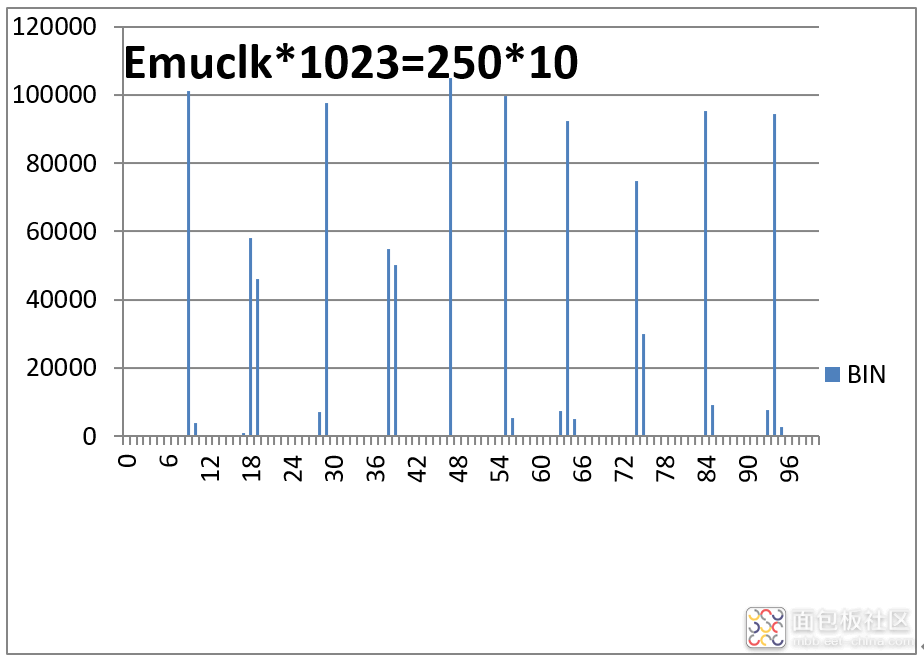

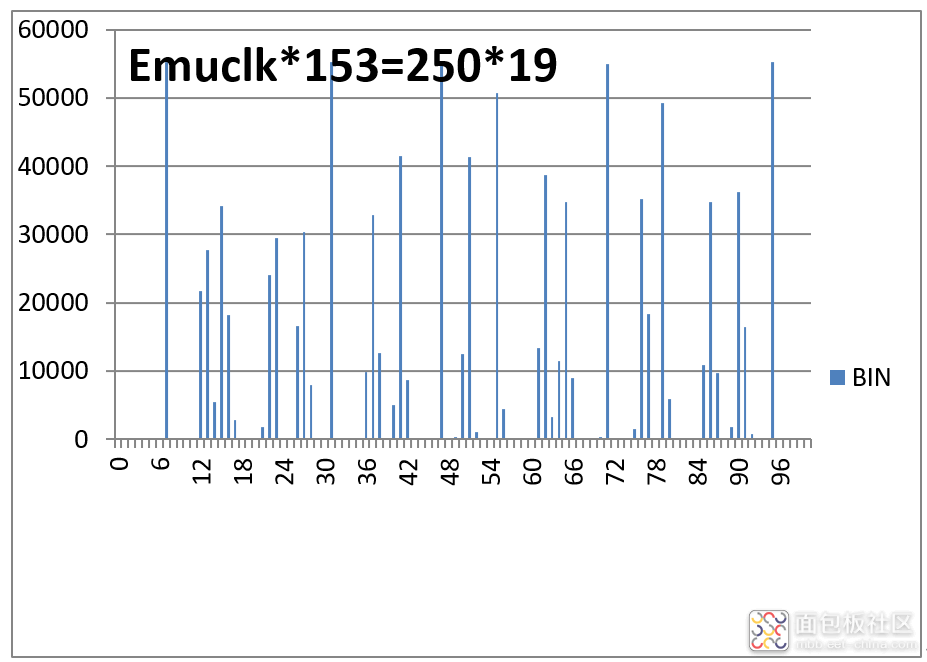

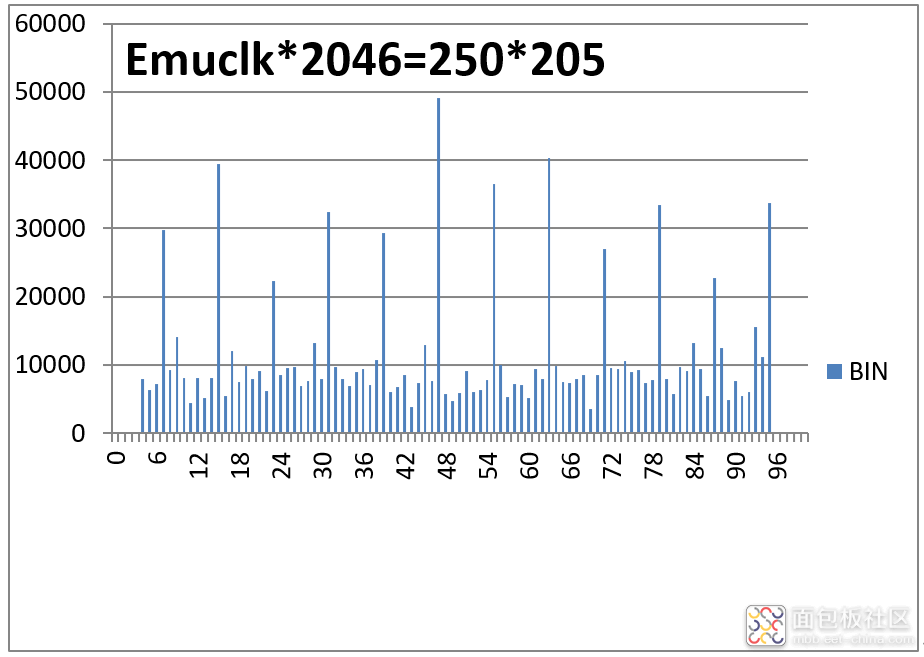

笔者实际使用的TDC时钟是250MHz,那么就需要另外一个PLL产生一个低速时钟,并且相位关系越复杂越好(即相关性越差越好)。为了验证上述分析,笔者作了三个实验,这三个实验分别用PLL产生了三个与250MHz时钟不同相位关系的模拟HIT时钟,实验的结果分别如图3、图4和图5所示。

图3:模拟HIT时钟和TDC时钟有10种相位关系

图4:模拟HIT时钟和TDC时钟有19种相位关系

图5:模拟HIT时钟和TDC时钟有205种相位关系

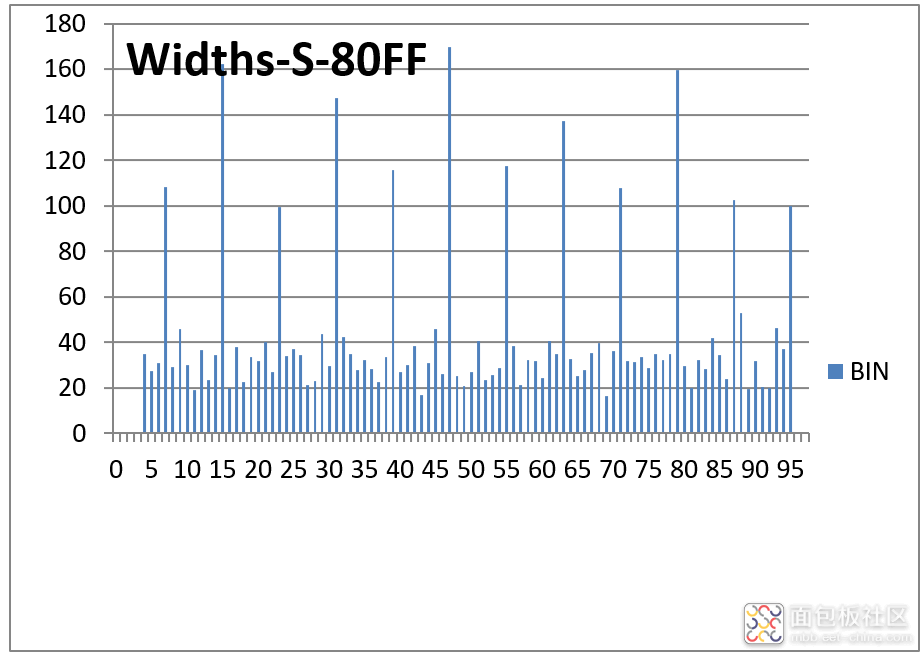

图3可以明显看出实际测量的结果模拟的HIT和TDC时钟确实只有10种相位关系(不考虑时钟的skew和jitter),而图4虽然看不出19种相位关系,但是时钟的skew,jitter以及延时链的非线性特性,某些相位的HIT很有可能已经重合而连在了一起,但是从数据上还是可以明显分辨出13组独立的数据,那些长连续的数据可以被高度怀疑为两个相邻相位拼接在一起了。图5的测试结果和实际使用随机(random)HIT所得到的测试结果基本相同,如图6所示。

图6:随机HIT测试结果

作者: coyoo, 来源:面包板社区

链接: https://mbb.eet-china.com/blog/uid-me-1010859.html

版权声明:本文为博主原创,未经本人允许,禁止转载!

/4

/4

默西赛德老男孩 2024-7-3 22:52