翻看之前博客发现很多年前发布过与JTAG有关的博文,具体如下:

这里要记录的也是与ALTERA器件的JTAG相关,具体器件是Cyclone 10 GX系列与MAX10系列同挂一个JTAG链路上面。问题是通过USB Blaster访问JTAG接口,并进行自动探测的时候,竟然出错,根本无法访问。

这个问题就比较讨厌,JTAG无法访问,意味着整个板子都可能要报废的,问题很严重。这到底是硬件设计问题还是硬件配置问题,还是其它什么问题等。详细检查硬件电路设计,还有板子的供电,大家一时都毫无头绪。作为有点FPGA设计经验的我们来说,当时还真点“阴沟里翻了船”的意味。

简单的JTAG问题,也经过了几天的排查,虽然没有将问题解决,但是可以确认的是硬件设计以及CPLD和FPGA的配置模式选择均未有任何问题,那么问题出现的原因到底是什么呢?这个板子的硬件设计参考是ALTERA(现在应该叫Intel)C10 GX系列的PCIE开发板,该开发板也是M10和C10GX同挂一个JTAG链,唯一的区别是开发板是2个M10器件+1个C10GX器件,我们的板子是一个M10+1个C10GX器件。开发多出的一个M10是用来实现UBS Blaster下载器功能,对应用户来说没有必要,使用外部下载电缆即可,而且一般用户也不了解USB Blaster的完整实现逻辑。

排查不是硬件设计问题,那么唯一还有一个问题就是Cyclone 10 GX系列对应上电有一个与以前系列器件不一样的要求(我不知道其他10代产品是否也有这样的要求),即FPGA的各个供电电压有上电电压顺序的要求,多出的M10器件就是用发来控制供电电压上电先后的。根据C10GX器件手册以及相关资料介绍,C10GX的所有供电电压可以划分为4个组合(group),即group1先上电,接着是group2、group3和group4,上电先后优先级不同。(对于这个供电电压先后顺序要求,后面另外专门讨论)。

由于板子上M10与C10GX的JTAG挂一个链,都无法成功访问,所以M10的程序没法下载进去,所以也无法完成对于C10GX上电顺序的控制,所以此时C10GX根本就是无法成功上电。故我们分析是不是就是因为这个原因导致C10GX影响了JTAG链路的不稳定,从而造成了JTAG无法访问。

比较幸运的是,当初讨论这个上电顺序的时候,追加了一个额外的控制器,即通过板子上的ARM程序参与控制,当然这个控制只是作为一个备选的方案。现在既然M10 CPLD无法完成控制,那么正好将这个备胎转正。

ARM加入控制后,板子上所有电源芯片都进入“ENABLE”状态。需要注意的是,之前上电控制器失效时,并非M10的供电失效,只是C10GX的供电失效。我们的初衷是在C10GX供电失效情况下,完成对M10的程序配置,然后M10完成对C10GX供电顺序的控制。现在这个控制由ARM完成,板子上电后,所有供电即参与工作。遗憾的是,即便如此,JTAG还是无法访问。

此时,将近一个礼拜过去,问题依旧。某天当同事在AUTO Detect瞬间测量JTAG供电时发现了异常,JTGA的供电我们选择的是1.8V,即VCCPGM=1.8V。该异常表现为VCCPGM在此AUTO Detect后拉升到1.9V以上,其实,该问题之前一直存在,但是我们忽略了,当时以为是LDO供电异常,尝试了更换调压电阻,甚至更换了LDO芯片。现在看来这个问题根源在外部USB Blaster下载电缆。

我们也是在瞬间想到,我们手上的所有USB Blaster电缆都是十多年前采购的,当时的这类电缆都只是支持3.3V或者2.5V电压,所以接入这类电缆,自动探测的时候将VCCPGM从1.8V拉升。

我们在开始这块板子硬件设计之前是在C10GX的pcie开发板进行过验证的,并使用过我们的“老旧”下载电缆成功访问过Cylone10GX器件的,为什么我们的板子无法访问呢?至此,我们返回去对比查找开发板原理和相关资料,才发现原因。

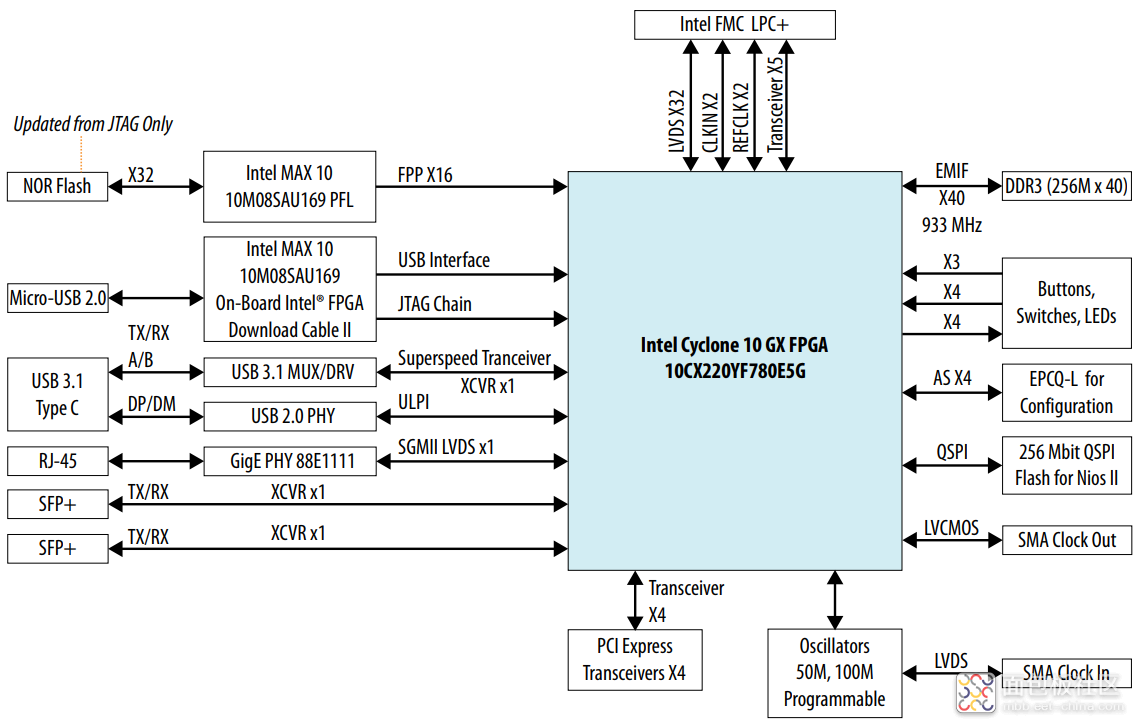

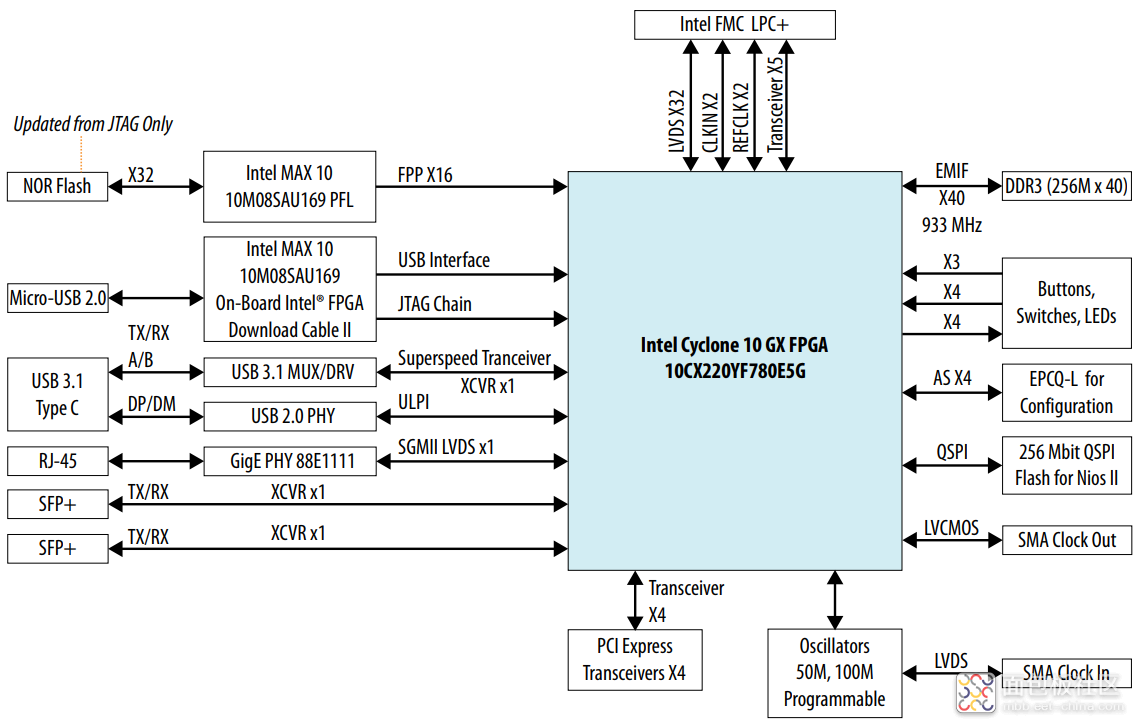

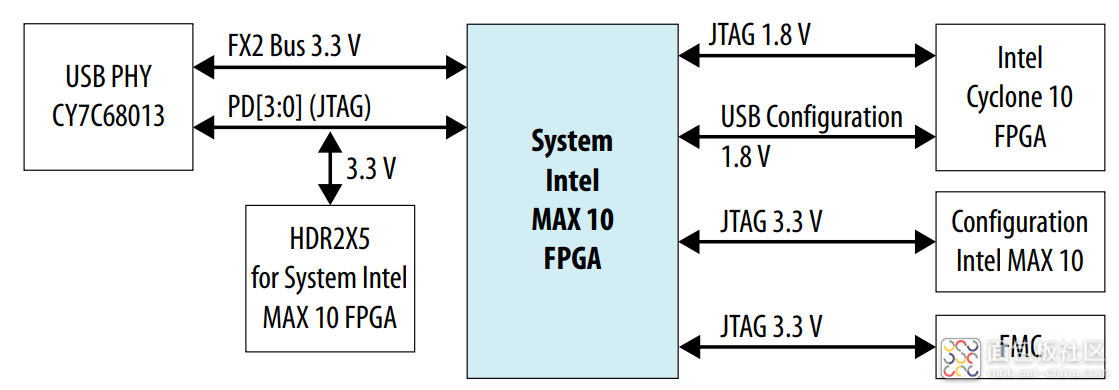

图1:Cyclone10GX系列PCIe开发板硬件框图

如图1所示为C10GX的pcie开发板硬件框图,左上角有2片M10系列CPLD,一片作为系统M10实现板载二代下载电缆功能,一片作为FPGA配置器件,FPGA和配置CPLD的JTAG信号引脚都独立接入到系统M10 cpld之中。系统M10使用逻辑将2片器件完成JTAG菊花链级联,所以这与我们的板子有些微差别。再看图2和图3.

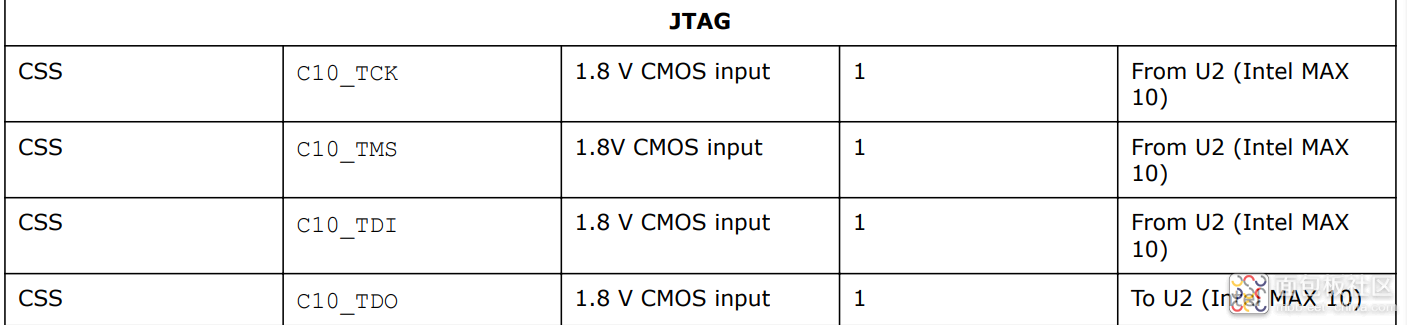

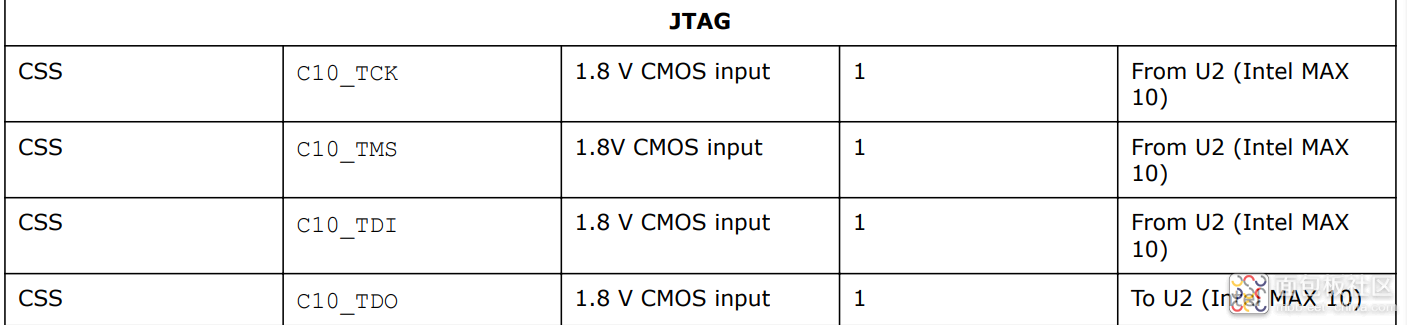

图2:C10的JTAG信号引脚供电和连接关系

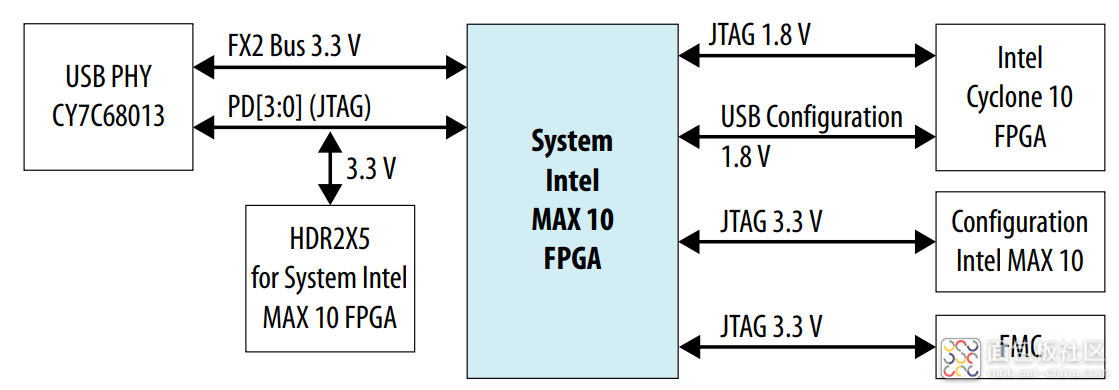

图3:C10GX pcie开发板JTAG拓扑结构框图

从图2看出,C10的JTAG引脚所处I/Obank供电电压是1.8V,即VCCPGM为1.8V,这些引脚单独接入U2,即SYS-M10。图3的JTAG拓扑结构框图也有明显展示,只是有2个疑问,第一,根据我对原理图检查发现,配置M10的JTAG应该也是1.8V接入系统M10;第二就是这个JTAG拓扑框图缺少了另外一个HDR2x5插座,通过该插座可以使用USB Blaster外部下载电缆直接访问C10和配置M10。我们就是使用手上老旧USB Blaster下载线通过这个插座访问了C10GX。为何开发板可以使用老旧下载线,原因就在于System M10将C10的1.8V的JTAG引脚接入后,再通过3.3V的I/Obank连接到外部JTAG插座上的。

所以,我们遇到的问题归根结底,就是手上老旧下载电缆与板子的1.8V JTAG接口的不兼容造成的。为了验证这个问题,通过网上搜索,发现某宝上有各种下载电缆都标称说支持ALTERA全系列器件,遗憾的是并未发现一家列出了对于CYCLONE 10 GX器件进行过类似验证,唯一一家只是标称有客户使用并成功访问过C10系列器件,所以列出的已经验证过的器件中ARRIA 10和Cyclone 10都是特意以红色标注。

为了成功解决问题,我们从网上随机采购了3种不同的下载电缆。三种电缆最后只有一种能够成功访问该1.8V JTAG,另外两种电缆虽然无法访问1.8Vjtag但都可以访问我们的老板子。能够成功访问1.8V低压JTAG接口是如图4所示的下载电缆。

图4:能够成功访问我们的1.8V低压JTAG接口的下载电缆

如图4所示,这个电缆标称I/O兼容1.5V~5V,我们买的另外两种标称兼容I/O电压是1.8V~5V。理论上应该是可以访问我们的1.8V低压JTAG接口的,无法访问的原因,我们的分析是因为板载JTAG的1.8V供电电压实际值应该稍微低于1.8V,比如只有1.78V左右,是否这个1.78V超出了后两种电缆标称的1.8V下限呢?

/5

/5

开发工匠 2024-5-7 10:02

tom2068_897375514 2024-4-30 08:43

开发工匠 2024-4-29 10:29