锁相环由鉴相器、环路滤波器和压控振荡器组成。通常鉴相器与辅助电路分频器一般集成在一起。想要改变VCO的输出频率,则是通过改变分频器的分频比实现。现已MC145146 PLL芯片为例,对各寄存器参数配置与输出频率之间的关系做一点总结:

1.一般结构

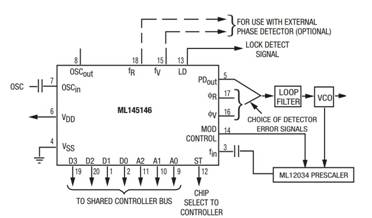

如下图所示,PLL内有三个分频寄存器分别是R寄存器(对参考时钟进行分频),N和A寄存器(对输出端VCO的频率进行分频),两路分频后的频率进鉴相器进行鉴相。锁定时,两路频率应该相等。

通常,在VCO频率在进PLL芯片之前会先经过一个双模预分频器,有的也集成在PLL芯片内。如下图的ML12034,一般可实现8/9,16/17,32/33,64/65,128/129等分频,控制分频系数改变的是PLL引脚的控制电平,如下图14脚MC。

2.频率改变原理

假设两个鉴相频率分别为参考源![]() 经过

经过![]() 分频后的

分频后的![]() 和输出VCO频率

和输出VCO频率![]() 经过

经过![]() 分频后的

分频后的![]() ,则有

,则有

![]()

![]()

其中,![]() 比较好理解,就是寄存器R,而

比较好理解,就是寄存器R,而![]() 由下式确定:

由下式确定:

![]()

其中,N,A为对应寄存器,P为预分频器P/P+1的分频比。

注意:此处分频可以按照下面的理解:

其工作过程是:首先预分频器工作在P+1分频模式下,预分频器输出后同时输入给计数分频器N与A分频,当A计数满后控制预分频器工作在P分频模式下,N继续计数直到满后N与A同时重置,重新开始。

在图1中,可以看出,计数分频器N输出鉴相频率![]() 。假设

。假设![]() 的周期为t,而鉴相

的周期为t,而鉴相![]() 的周期为T,可以得到:

的周期为T,可以得到:

![]()

因此,分频比![]() 。

。

总结:1.通过R、N、A、P控制VCO输出频率;

2.由上式还可以看出,鉴相频率VCO决定了VCO输出的步进频率。

3.PLL配置举例

下面以MC145146为例,用TI的430MCU为控制器,对其寄存器进行配置。由于MC145146与MSP430工作电平不同,中间用的TI的4054进行TTL到CMOS的电平转换。

根据MC145146的工作时序以及寄存器的对应关系可以看出,由A2-A0三位地址将A、N、R寄存器分7次写入数据,数据的写入方式为在数据与地址稳定后,由ST引脚的脉冲控制写入。

通过实验验证,下列程序可以对其其寄存器进行正确配置,函数还可以优化,基本原理相同。

/******************************************************

程序功能:UpFreq

引脚定义:D3-D0:P2.3-P2.0,A2-A0:P2.7-P2.5,ST:P2.4

使用:

*******************************************************/

#define CLR_ST P2OUT&=~BIT4 //ST

#define SET_ST P2OUT|= BIT4

unsigned char A=0x22; //

unsigned char N1=0xB2; //

unsigned char N2=0x01; //

unsigned char R1=0x2C; //

unsigned char R2=0x01; //

/*****************************************************************

函数名称: WriteReg

返回值 :无

*****************************************************************/

void WriteReg()

{

unsigned char temp;

CLR_ST;

temp = A & 0x0f; //A取低4位

temp = temp + 0xe0;

P2OUT = 0x0f & temp; //地址000

SET_ST;

CLR_ST; //写入

temp = A & 0x70; //A取高3位

temp = temp>>4;

temp = temp + 0xe0;

P2OUT = 0x2f & temp;//地址001

SET_ST;

CLR_ST; //写入

temp = N1 & 0x0f; //N1取低4位

temp = temp + 0xe0;

P2OUT = 0x4f & temp; //地址002

SET_ST;

CLR_ST; //写入

temp = N1 & 0xf0;

temp = temp>>4;

temp = temp + 0xe0;

P2OUT = 0x6f & temp;//地址003

SET_ST;

CLR_ST; //写入

temp = N2 & 0x03; //N2取低2位

temp = temp + 0xe0;

P2OUT = 0x8f & temp; //地址004

SET_ST;

CLR_ST; //写入

temp = R1 & 0x0f; //R1取低4位

temp = temp + 0xe0;

P2OUT = 0xaf & temp; //地址005

SET_ST;

CLR_ST; //写入

temp = R1 & 0xf0;

temp = temp>>4;

temp = temp + 0xe0;

P2OUT = 0xcf & temp; //地址006

SET_ST;

CLR_ST; //写入

temp = R2 & 0x0f; //R2取低2位

temp = temp + 0xe0;

P2OUT = 0xef & temp; //地址007

SET_ST;

CLR_ST; //写入

}

/4

/4

用户289521 2015-1-16 10:09

用户289521 2015-1-16 10:06

xyd20405 2015-1-16 07:38

风来 2015-1-9 19:05