数字滤波设计—系统需求

1.1系统架构

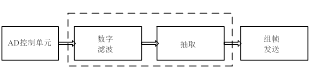

三片ADS8320控制72路AD通道,每片AD器件通过模拟开关采集24路模拟通道。采样频率为1K,数字滤波也按照1K的数据流进行,后级根据不同的采样需求,抽取出128、256、512序列。在FPGA内部设计的基本结构如下。

1.2滤波器的性能指标

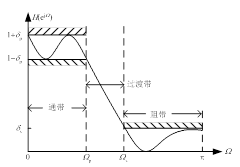

我们在进行滤波器设计时,需要确定其性能指标。一般来说,滤波器的性能要求往往用频率响应来表征。以低通滤波器特性为例,频率响应有通带、过渡带及阻带三个范围。常见的指标主要有:幅度特性的允许误差(纹波);过渡带斜率(滚降是否达到要求);带外衰减。

通带: 1- AP≤| H(ejω)| ≤1 |ω|≤ωc(纹波尽了小)

过渡带:要求过渡带滚降要快,迅速达到衰减要求

阻带: |H(ejω)| ≤ Astωst ≤|ω|≤ωc (阻带衰减要大)

其中ωc为通带截止频率,ωst为阻带截止频率,Ap为通带误差,Ast为阻带误差。

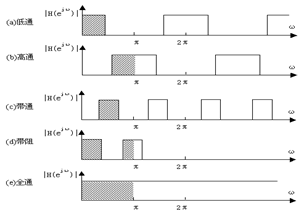

与模拟滤波器类似,数字滤波器按频率特性划分为低通、高通、带通、带阻、全通等类型,由于数字滤波器的频率响应是周期性的,周期为2π。各种理想数字滤波器的幅度频率响应如图1.3所示。

1.3本设计中的滤波需求

对每一个通道采集的数字量进行数字滤波,要求设计低通和带通两种滤波器。其中低通滤波器用来滤除带外噪声信号包括50Hz或60Hz工频信号,带通滤波器用于阻抗测试,主要滤除直流成分。

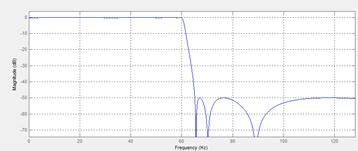

低通(lowpass)滤波器指标:

原采样率(AD采样频率) :Fs=1024Hz

通带 :Fpass=60Hz

截止频率 :Fc=64Hz

通带纹波 :Apass<0.2dB

阻带衰减 :Astop>50dB

例如按照指标设计出的IIR频率响应:

带通(bandpass)滤波器指标:

采样频率Fs=256

Fc1=18

Fc2=22

阻抗测试时,输入的是标准的正弦波信号,其噪声比较小,阻带衰减可以不做太苛刻的要求。数字滤波器阶数和结构按照低通指标来设计,而低通和带通滤波不同之处仅在系数上面。设计完成后,按照不同的需求,加载不同系数,完成低通和高通的功能。在设计这种共用滤波结构的不同类型的滤波时,按照指标要求比较苛刻的滤波器设计。在确定滤波器的阶数和结构后,再由其设计出指标比较低的另外一种滤波器。所以,以下设计都是按照低通滤波器参数来设计。

/2

/2

用户442508 2013-10-23 21:30

用户377235 2013-10-20 20:53

原采样率(AD采样频率) :Fs=1024Hz 通带 :Fpass=60Hz 截止频率 :Fc=64Hz 通带纹波 :Apass<0.2dB 阻带衰减 :Astop>50dB LZ,请问部分参数该如何得到?