基于FPGA的数字滤波设计—IIR设计4

4.4 利用FPGA实现IIR滤波器(32bits计算)

4.4.3控制单元(状态机)

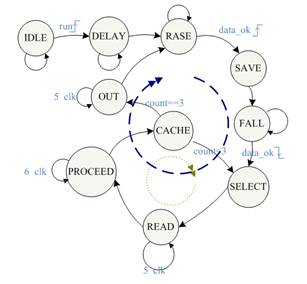

对数据路径单元进行控制的部分由状态机完成。状态说明在表格4.4中,状态转换图如图4.4所示。

在状态转换图中可以看出,此状态机中有两个循环,大的循环中(蓝色线标识)完成一次采样周期里对3路ADC数据进行IIR滤波计算。大循环内部有一个小循环(红线标识),蓝色循环每执行一次红色循环执行3次,红色循环一次完成对一路ADC的计算。

4.4.4 RAM中存储调度

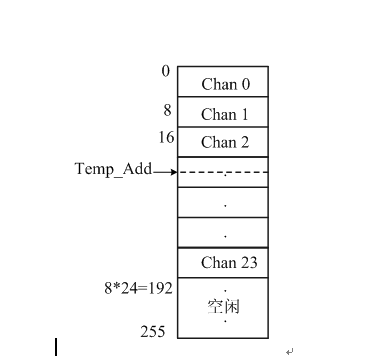

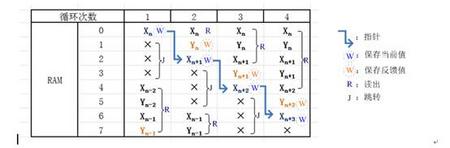

图4.3所示的数据路径图中的RAM对应的地址空间分配如图4.5所示。为每个模拟通道分配8个存储空间,存储调度如图4.6所示。

指针在每一帧(24个通道)开始前加2,完成Xn→Xn+1的保存。

1. 在SAVE状态时,保存当前的Xn;

2. 在READ状态时,按顺序读出Xn-2、Yn-2、Xn-1、Yn-1和Xn;

3. 在OUT状态时,保存Yn;

4. MAC计算乘累加时,连续读5个数据,读地址在指针的基础上加4;

5. 存入Yn值时,写入地址在指针基础上加1;

6. 指针每次按照2自增。

4.4.5时间余量计算

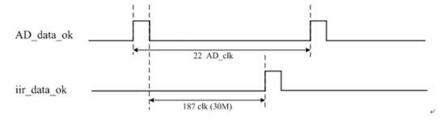

系统需求,在每个AD_data_ok有效时,采集3个通道值,并在下一个AD_data_ok有效之前完成IIR计算。

AD_clk=2.5MHz,采样间隔为(1/2.5M)*22=8.8us

IIR计算所需时间为(1/30M)*187=6.17us

IIR计算时间小于采样间隔,所以能够完成优化后32bits的IIR滤波功能。

1、64阶FIR并不能完成来时提出的指标要求;

2、18bits位宽IIR,容易产生溢出,增益需要调整;

3、结构优化后的32bits位宽IIR能够满足指标要求,同时硬件资源可以胜任。

/1

/1

用户1740684 2014-3-13 15:22