1、什么是x MII接口

MII (Media Independent Interface)接口,即介质无关接口或称为媒体独立接口,它是IEEE-802.3定义的以太网行业标准。“介质无关” 表明在不对MAC硬件重新设计或替换的情况下,任何类型的PHY设备都可以正常工作。

MII接口是MAC和PHY之间的通信接口,MAC产生要发送的以太网帧后,按照约定的xMII接口(这里的xMII指MII及各种衍生的MII接口,它可以是MII接口或者RGMII接口等),将数据发送给PHY,PHY进行编码等一系列处理后,把数据发送到传输介质上,就算把一帧数据传出去了;数据的接收同理。

MII接口的类型有很多,常用的有MII、RMII、GMII、RGMII、SMII、SSMII、SSSMII、SGMII等,下面对它们分别进行介绍。

2、百兆以太网接口

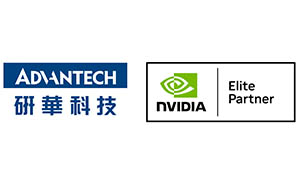

2.1、MII接口

MII接口(Media Independent Interface)即介质无关接口,它可能是最早出现的一种MII接口,支持10M/100M以太网。

MII接口信号包括三类,分别为:

发送端信号:

-

TX_CLK:发送参考时钟,100Mbps速率下,时钟频率为25MHz,10Mbps速率下,时钟频率为2.5MHz。注意,TX_CLK时钟的方向是从PHY侧指向MAC侧的,因此此时钟是由PHY提供的

-

TXD[3:0]:数据发送信号,共4根信号线

-

TX_EN: 发送使能信号(Transmit Enable),只有在TX_EN有效期内传的数据才有效

-

TX_ER:发送数据错误提示信号(Transmit Error),同步于TX_CLK,高电平有效,表示TX_ER有效期内传输的数据无效。对于10Mbps速率下,TX_ER不起作用

接收端信号:

-

RX_CLK:接收数据参考时钟,100Mbps速率下,时钟频率为25MHz,10Mbps速率下,时钟频率为2.5MHz。RX_CLK也是由PHY侧提供的。

-

RXD[3:0]:数据接收信号,共4根信号线

-

RX_DV:接收数据有效信号(Reveive Data Valid),作用类型同发送通道的TX_EN

-

RX_ER:接收数据错误提示信号(Receive Error),同步于RX_CLK,高电平有效,表示RX_ER有效期内传输的数据无效。对于10Mbps速率下,RX_ER不起作用;

载波侦听多路访问/冲突检测(csma/cd):

-

CRS:Carrier Sense,载波侦测信号,不需要同步于参考时钟,只要有数据传输,CRS就有效,只有PHY在半双工模式下有效

-

COL:Collision Detectd,冲突检测信号,不需要同步于参考时钟,只有PHY在半双工模式下有效

上面的内容有以下几点需要注意:

-

不管是发送端时钟还是接收端时钟,都是由PHY产生并传递给MAC

-

MII支持10M和100M两种模式,因为数据总线固定为4位,所以在10M模式下,时钟频率是10M/4即2.5MHz;同理,在在100M模式下,时钟频率是100M/4即25MHz

-

在10M模式下,指示数据是否错误的两个信号TX_ER和RX_ER都是不起作用的

-

CRS和COL只在半双工模式下有效,因为现在的以太网基本上都是交换式的星型结构,也就是说都运行在全双工模式,所以这两个信号其实基本上是用不到的

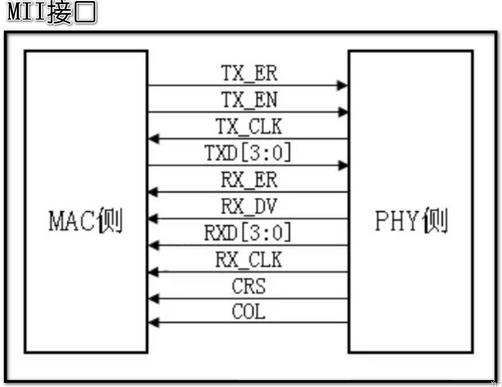

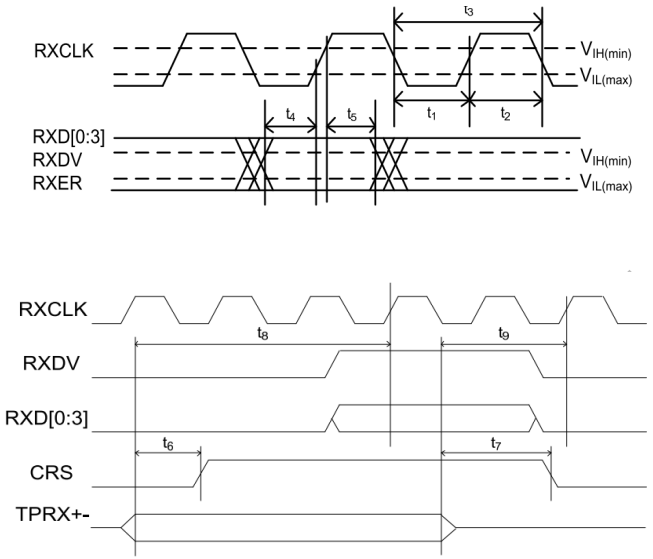

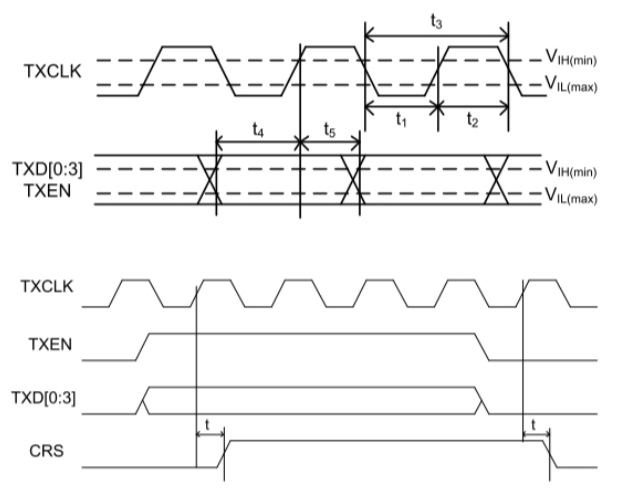

PHY芯片向MAC传输数据的接口时序如下图所示,PHY芯片在RX_CLK下降沿输出数据RXD,MAC在时钟上升沿采集数据。

MAC向PHY芯片传输数据的接口时序如下图所示,MAC芯片在TX_CLK下降沿输出数据TXD,PHY在时钟上升沿采集数据。

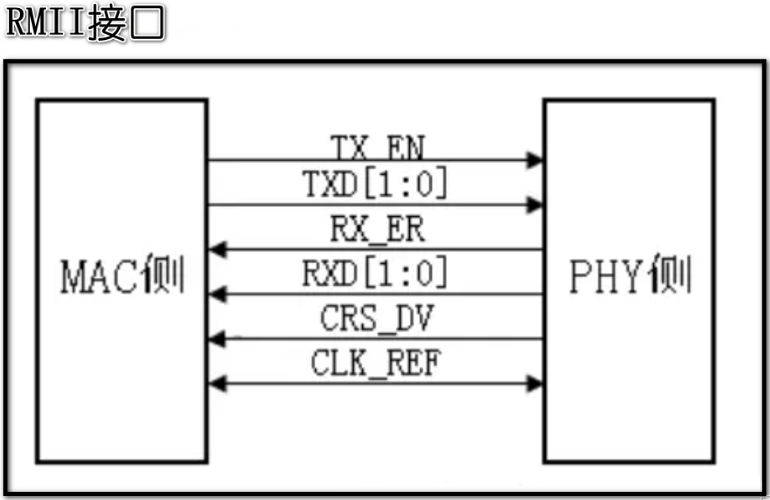

2.2、RMII接口

RMII(Reduced Media Independent Interface)接口即精简MII接口,其实就是MII接口的简化版本。

-

TXD[1:0]:数据发送信号线,数据位宽为2,是MII接口的一半

-

RXD[1:0]:数据接收信号线,数据位宽为2,是MII接口的一半

-

TX_EN(Transmit Enable):数据发送使能信号,与MII接口中的该信号线功能一样

-

RX_ER(Receive Error):数据接收错误提示信号,与MII接口中的该信号线功能一样

-

CLK_REF:是由外部时钟源提供参考时钟。MII接口中的接收时钟和发送时钟是分开的,而且都是由PHY芯片提供给MAC芯片的。这里需要注意的是,由于数据接收时钟是由外部晶振提供而不是由载波信号提取的,所以在PHY层芯片内的数据接收部分需要设计一个FIFO,用来协调两个不同的时钟,在发送接收的数据时提供缓冲。PHY层芯片的发送部分则不需要FIFO,它直接将接收到的数据发送到MAC就可以了。

-

CRS_DV:此信号是由MII接口中的RX_DV和CRS两个信号合并而成,高电平表示发送的数据有效

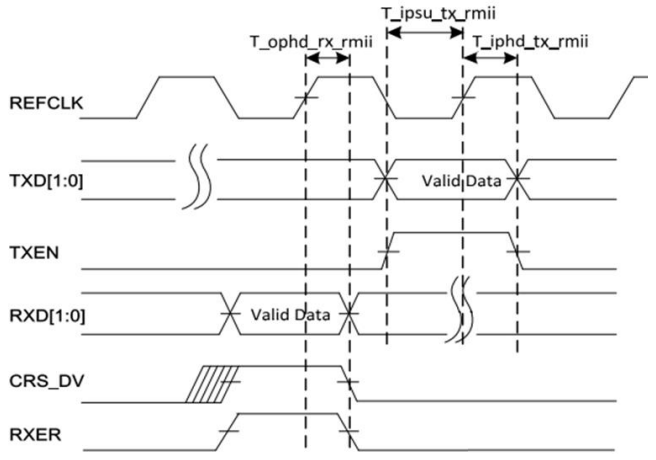

因为RMII接口的数据线数量只是MII接口的一般,所以为了能达到同等的通讯速率,就肯定要把时钟频率翻倍,所以在100Mbps模式时为时钟为50MHz,10Mbps时时钟为5MHz。RMII接口时序与MII是一致,时序图如下:

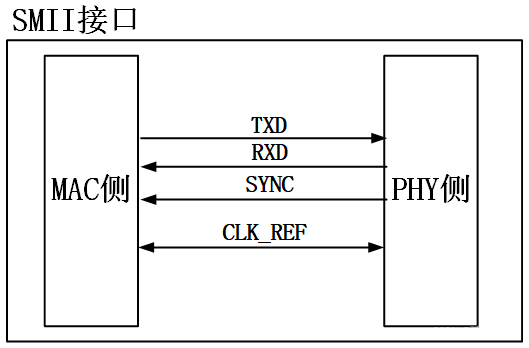

2.3、SMII接口

SMII(Serial MII)即串行MI接口,跟RMII相比,连线减少到4根。

-

TXD:发送数据信号,位宽为1

-

RXD:接收数据信号,位宽为1

-

SYNC:收发数据同步信号,每10个时钟周期置1次高电平,指示同步

-

CLK_REF:所有端口共用的一个参考时钟,频率为125MHz,为什么100Mbps速率要用125MHz时钟?因为在每8位数据中会插入2位控制信号

-

TXD/RXD以10比特为一组,以SYNC为高电平来指示一组数据的开始,在SYNC变高后的10个时钟周期内,TXD上依次输出的数据是:TXD[7:0]、TX_EN、TX_ER,控制信号的含义与MII接口中的相同;RXD上依次输出的数据是:RXD[7:0]、RX_DV、CRS,RXD[7:0]的含义与RX_DV有关,当RX_DV为有效时(高电平),RXD[7:0]上传输的是物理层接收的数据。当RX_DV为无效时(低电平),RXD[7:0]上传输的是物理层的状态信息数据。当速率为10Mbps时,每一组数据要重复10次,MAC/PHY芯片每10个周期采样一次。MAC/PHY芯片在接收到数据后会进行串/并转换。

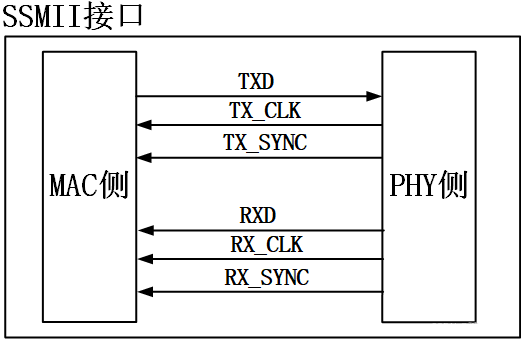

2.4、SSMII接口

SSMII(Serial Sync MII)即串行同步MII接口,跟SMII接口很类似,只是收发使用独立的参考时钟和同步时钟,不再像SMII那样收发共用参考时钟和同步时钟,传输距离比SMII更远。

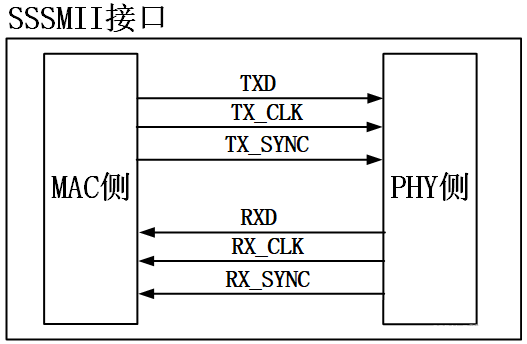

2.5、SSSMII接口

SSSMII(Source Sync Serial MII)即源同步串行MII接口,SSSMII与SSMII的区别在于参考时钟和同步时钟的方向,SSMII的TX/RX参考时钟和同步时钟都是由PHY芯片提供的,而SSSMII的TX参考时钟和同步时钟是由MAC芯片提供的,RX参考时钟和同步时钟是由PHY芯片提供的,所以顾名思义叫源同步串行。

3、千兆以太网接口

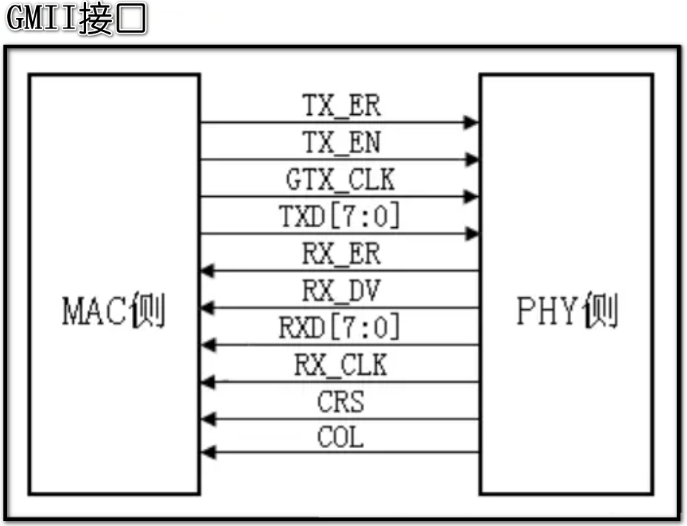

3.1、GMII接口

GMII(Gigabit Media Independent Interface)接口即吉比特MII接口,是比较常见的千兆网接口。

与MII接口相比,GMII的数据宽度由4位变为8位,GMII接口中的控制信号如TX_ER、TX_EN、RX_ER、RX_DV、CRS和COL的作用同MII接口中的一样,发送参考时钟GTX_CLK和接收参考时钟RX_CLK的频率均为125MHz(1000Mbps/8=125MHz)。

在这里有一点需要特别说明下,那就是发送参考时钟GTX_CLK,它和MII接口中的TX_CLK是不同的,MII接口中的TX_CLK是由PHY芯片提供给MAC芯片的,而GMII接口中的GTX_CLK是由MAC芯片提供给PHY芯片的。两者方向不一样。

在实际应用中,绝大多数GMII接口都是兼容MII接口的,所以,一般的GMII接口都有两个发送参考时钟:TX_CLK和GTX_CLK(两者的方向是不一样的,前面已经说过了),在用作MII模式时,使用TX_CLK和8根数据线中的4根。GMII的收发时序和MII差不多,只是时钟频率和数据位宽有点区别,此处就不赘述了。

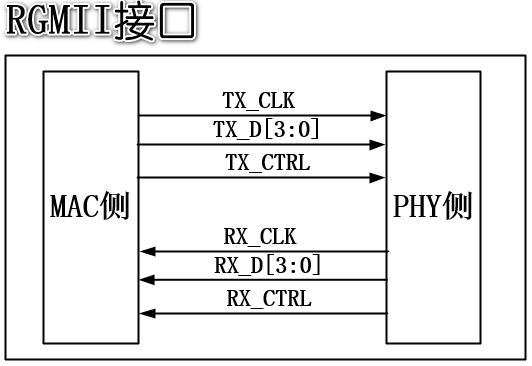

3.2、RGMII接口

RGMII(Reduced Gigabit Media Independent Interface),即精简GMII接口,是GMII接口的简化版本,接口信号线数量进一步减少。

TX/RX数据宽度从8为变为4位,但时钟频率仍旧为125MHz,为了保持1000Mbps的传输速率不变,所以RGMII接口在时钟的上升沿和下降沿都采样数据。RGMI同时也兼容100Mbps和10Mbps两种速率,此时参考时钟速率分别为25MHz和2.5MHz。

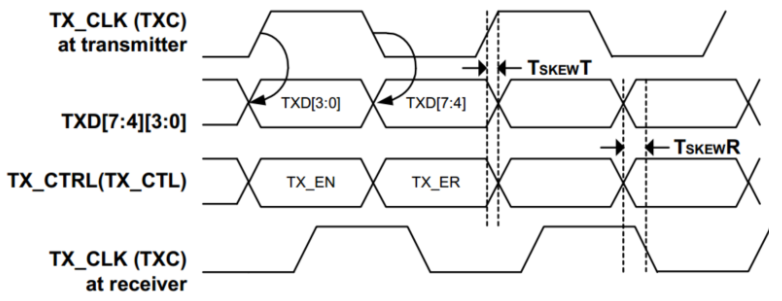

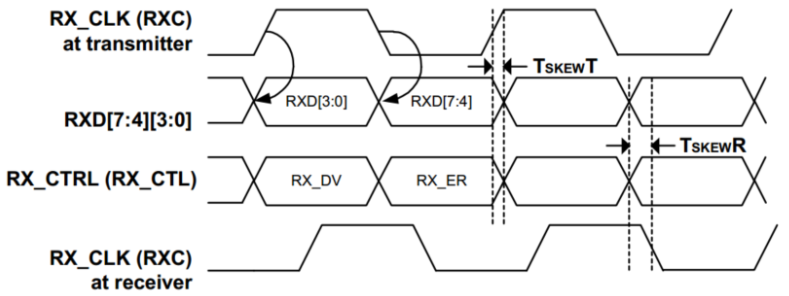

在参考时钟的上升沿发送GMII接口中的TXD[3:0]/RXD[3:0],在参考时钟的下降沿发送GMII接口中的TXD[7:4]/RXD[7:4]。TX_CTRL信号线上传送TX_EN和TX_ER两种信息,在TX_CLK的上升沿发送TX_EN,下降沿发送TX_ER;同样的,RX_CTRL信号线上也传送RX_DV和RX_ER两种信息,在RX_CLK的上升沿发送RX_DV,下降沿发送RX_ER。

发送端时序图如下所示:

接收端时序图如下所示:

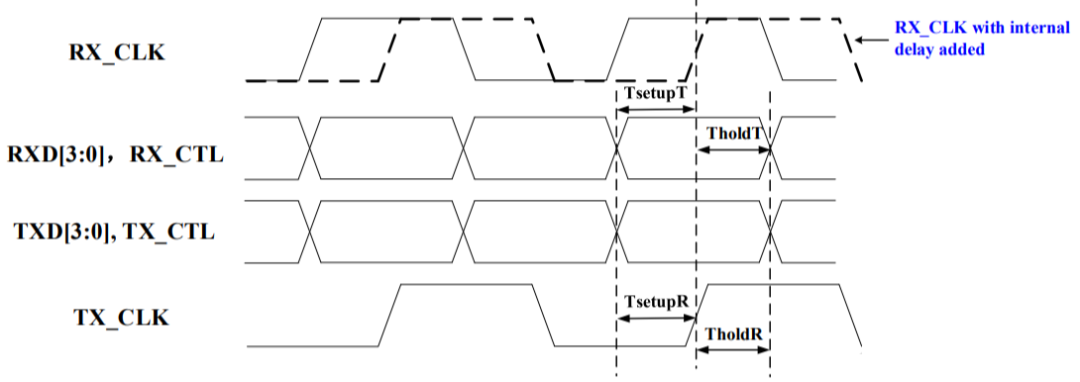

不管是对于发送端还是接收端来说,同时传输的都是数据加时钟,所以这是一种典型的源同步电路。为了保证发出去的数据能正确地被MAC和PHY接收到,必须让数据在时钟的边沿保持稳定,即满足建立时间和保持时间要求。如果数据和时钟同时发生变化,则容易产生亚稳态。

因为时钟频率为125M,所以周期为8ns,又因为是双沿传输,所以每个边沿的持续时间是4ns,如果数据和时钟之间有2ns的延迟,则在时钟边沿采样时,刚好处于数据的中心位置。大部分的PHY芯片都有给时钟延时的功能(可配置)。如果加上这个功能,那么输出的数据和时钟之间有2ns的延迟,时序图如下:

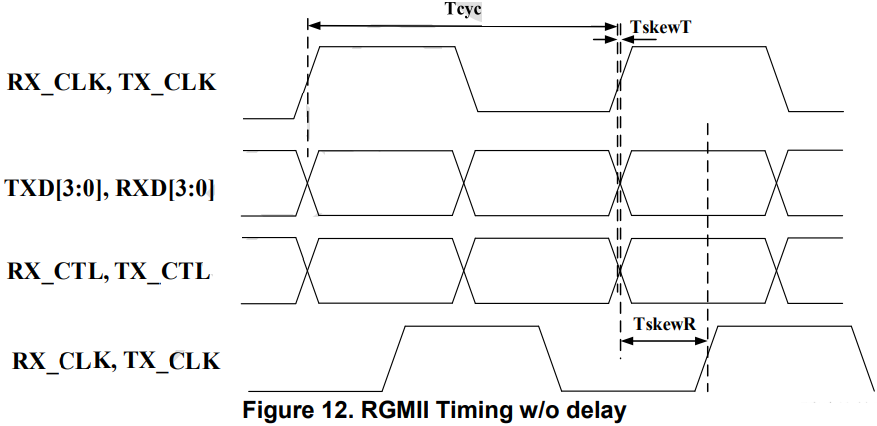

此时的采样边沿刚好处于数据最稳定的中心位置,可以满足建立时间和保持时间要求,不会发生亚稳态。如果不使用这个功能,那么传输出去的时钟和数据是同时变化的,如下:

为了不产生亚稳态,需要对时钟进行手动延迟。对于输入到FPGA的信号可以用IDELAYE2原语调节延迟;而对于从FPGA输出到PHY的芯片的信号则可以使用ODELAYE2原语调节延迟。需要注意的是Xilinx的A7系列芯片没有ODELAYE2原语。

除了使用原语,也可以使用PLL或者MMCM来对时钟的相位进行调节,只是可能精度会差一点。

3.3、SGMII接口

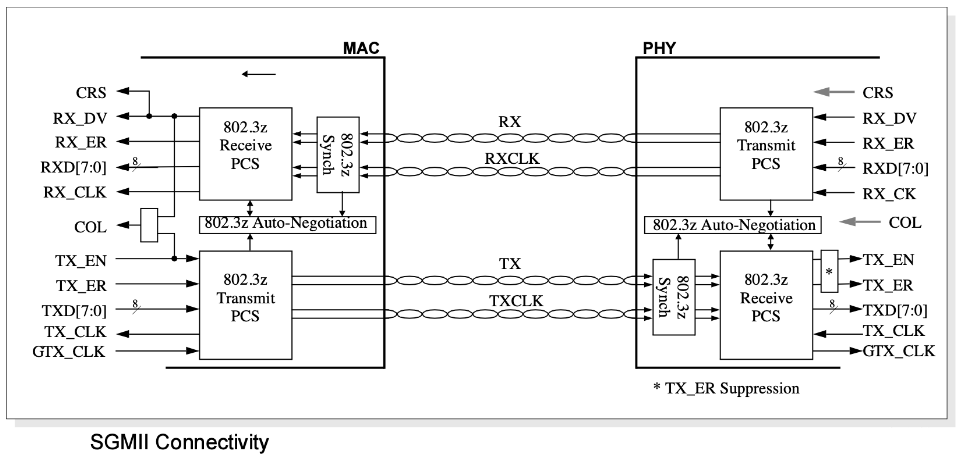

SGMII(Serial Gigabit Media Independent Interface),即串行古比特MII接口。SGMII发送、接收各1对差分对,在时钟信号的上升沿和下降沿均采样(DDR 模式), 发送和接收时钟频率均为 625MHz , 差分对为1.25Gbit/s速率。

采用8b/10b编码方式,在TXD发送的串行数据中,每8比特数据会插入TX_EN/TX_ER 两比特控制信息,同样,在RXD接收数据中,每8比特数据会插入RX_DV/RX_ER 两比特控制信息。

SGMII发送和接受数据各 1 对差分信号(LVDS),有 1 对差分时钟,共 6 根线。对于 MAC/PHY 中包括时钟恢复电路(CDR)系统,TXCLK 可以省略,SGMII接口只需要 4 根线。

625Mbps * 2 * 1 = 1.25Gbps,1.25Gbps * 80% = 1Gbps。

但是SGMII规范还设计有随路时钟, 这是因为早期为了节省成本,芯片内没有CDR。现在的芯片基本都可以通过接收端CDR做时钟恢复,进一步减少时钟引脚和时钟与数据之间的skew,也减少了信号pin数量。

SGMII很容易理解成将GMII的并行数据通过串并转换后发送出去,8-bit数据,2-bit控制,刚好满足1.25Gbit/s的实际速率。但是实际并不是这样理解,而是125MHz参考时钟通过PLL进行5倍倍频后,625MHz时钟嵌在数据里,采用DDR模式,故625Mbps * 2 = 1.25Gbps。

SGMII在跑100M速率时,并不是降速到125M,这种速率下无法避免长0或长1的问题,Serdes在这个速率跑不起来。所以实际SGMII跑100M时也是1.25Gbit/s速率,就是把1分数据重复发了10次。1000 BASE-X跑百兆光模块时实际也是这么运行的。

1000base-X为什么要做8b/10b编码,原因就是serdes码流中不能有长时间0或长时间1的情况,长0或长1时接收端不能正确地采样信号,另外还会由于单极性码含有直流分量,这种直流成分会随数据中1和0的随机变化也呈现随机性,这会引起接收端的基线漂移导致接收端误判。如果不做8B/10B编码,serdes传输是不能成立的,所以SGMII的1.25Gbit/s速率也是因为8B/10B编码。那么2-bit的控制信号是加扰二进制码,将8bit编码成10bit后,连续的1或者0不能超过5位。

4、万兆以太网接口

4.1、XGMII接口

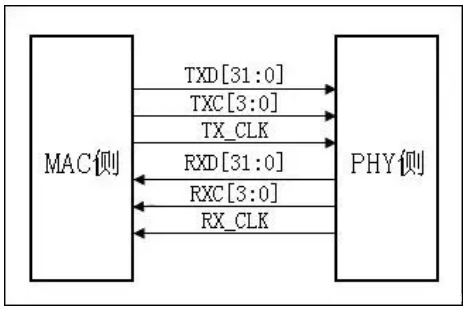

XGMII即10 Gigabit Media Independent Interface,其中的X对应罗马数字10。XGMII 是用于10G以太网的MAC与PHY设备间通信的接口标准,它包括 32 bits 的数据通道(RXD & TXD),两组 4 bits 的控制通道(RXC & TXC)和两组时钟(收/发),时钟频率 156.25 MHz ,工作在 DDR 模式。即10 Gbps = 156.25 MHz × 32 bits × 2

下图表示XGMII接口的连接示意图,注意 RXD/TXD 信号上的 36 表示 32bits 数据 + 4 bits 控制信号,其中每 8 bits 数据称为 1 个Lane,每个Lane共用1路控制信号。

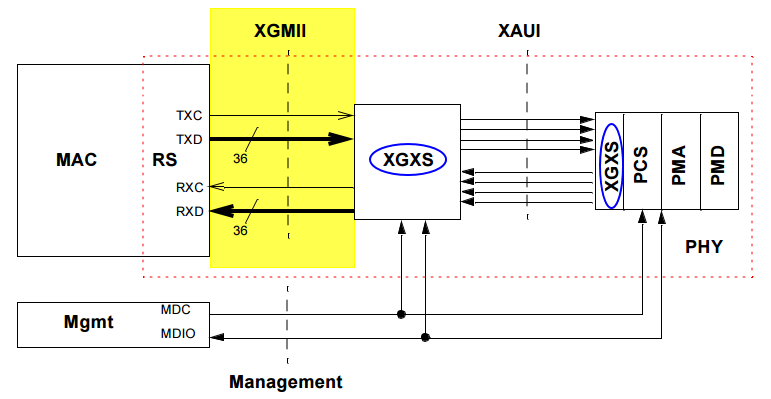

4.2、XAUI接口

XGMII信号数目(74 根)较多,通常用于芯片内的连接,不适合作为芯片间通信的接口,因此协议定义XGXS(XGMII eXtender Sublayer)子层以缩减信号数目,简化硬件设计。XGXS 子层主要完成 8b/10b 编码和不同Lane之间的去偏斜等功能。如下图所示,在信号链的两端,MAC和PHY 都包括XGXS子层,XAUI接口是 XGXS 之间通信的接口。

XAUI 接口包括4组发送差分对和4 组接收差分对,共 16 根信号。每组差分对(Lane)的数据速率为 3.125 Gbps,因此总的数据速率为 4 × 3.125 Gbps = 12.5 Gbps,考虑到8b/10b的效率为80%,因此实际数据速率为 12.5Gbps × 80% = 10 Gbps。

虽然XAUI有4serdes组信号,但它仍然是串行总线而不是并行总线,因为这4组sedes并不共用时钟,时钟都是从各自CDR中恢复的。这4组serdes也没有等长的要求,因为它们之间没有时序关系。这个结论可以推广到所有4组serdes组成的以太网接口。

1GSPS高速ADC采集模块-FMC-8164

新品推荐

FMC-8164 标准FMC卡,集成 4 通道 1Gsps 采样率,16 位 AD,4 通道1.25Gsps 16 位 DA。具有同步/触发功能,模拟信号采用 SSMC 射频连接器输入和输出,支持外时钟和板载时钟模式。

应用于通信多载波,雷达与智能天线,测试与测量系统, 软件无线等场合。

ADC性能指标

• ADC 型号:ADS54J60;

• 4 通道16 位分辨率,1GSPS 采样率;

• 噪底:-159dBFS/HZ;

• 模拟输入带宽(3dB):1.2GHZ;

• 100dBc 通道隔离度/串扰(@170MHz);

DAC性能指标

DAC 型号:DAC39J84;

• 分辨率:16bits;

• 最大采样率:2.8GSPS;

• 通道数:4;

• 耦合方式:支持直流和交流耦合。

0

0