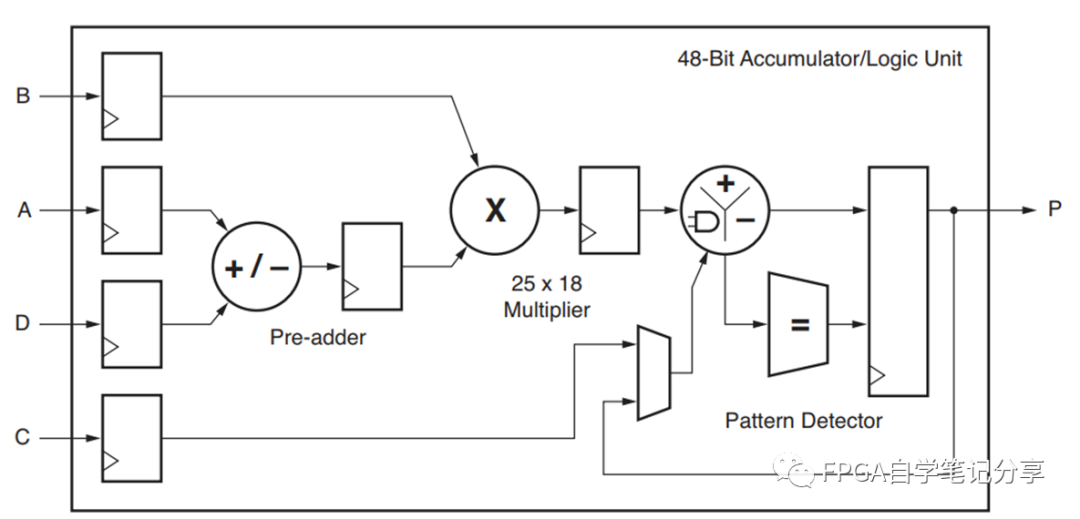

FPGA的乘法操作一般是由dsp硬核实现的,比如我们之前文章中曾将仔细讲解的xilinx k7系列的DSP48E1,Ultrascale+的dsp48E2。每个芯片都有各自的DSP硬核可供使用。

dsp48e1结构图如下

本次文章针对的是简单的乘法操作:简单的固定乘法可以使用移位加的方法进行实现,进一步简单的说就是将固定的乘法转换为若干个2**n的和的结果。

比如:a*9 = a*(8+1)=a*(2**3)+a*(2**0),对于任意a*9的操作,可以将其分为a*8+a,对应的代码为:

mult9assign S_data_in_mult8 = {i_data_in,3'b0}; always @(posedge i_sys_clk)= S_data_in_mult8 + i_data_in ;

同样的对于a*18=a*(16+2)=a*(2**4)+a*(2**1),对应的代码就是:

/// mult18= {i_data_in,4'b0};= {i_data_in,1'b0}; always @(posedge i_sys_clk) S_data_in_mult9 <= S_data_in_mult16 + S_data_in_mult2 ;

这样将将乘法转换为了加法,大大节约了对FPGA底层资源的浪费。

0

0