一、为何LUT能充当分布式RAM

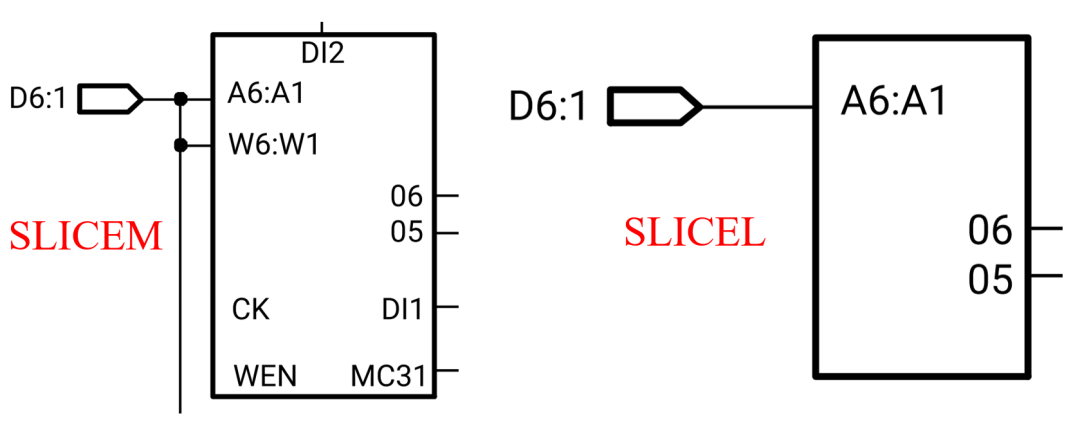

下图中左边为SLICEM中的LUT结构,右边为SLICEL中的LUT结构。

SLICEL只有查找表的功能,SLICEM除了能当查找表使用外,还能当移位寄存器、RAM、ROM使用,本文介绍RAM的使用,前文为什么xilinx FPGA中的LUT可以当作移位寄存器使用?90%的工程师都不知道已经介绍移位寄存器的使用。LUT各个管脚功能如下,作为存储器使用时不用MC31脚。

| 管脚 | 功能 |

|---|---|

| DI1、DI2 | 数据输入 |

| O5、O6 | 数据输出 |

| A6-A1 | 读地址 |

| W6-W1 | 写地址 |

| WEN | 写使能,高电平有效 |

| CK | 时钟 |

从上表不难看出这些引脚足够用来形成RAM了。RAM的工作原理为根据写地址在WEN为高电平时将数据同步写入,根据读地址将数据异步读出。

写操作是同步的。读操作是异步的,即A6-A1变化后,O5、O6的值立马变化(仅有器件延迟)。

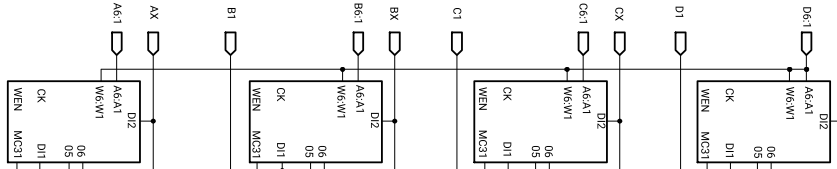

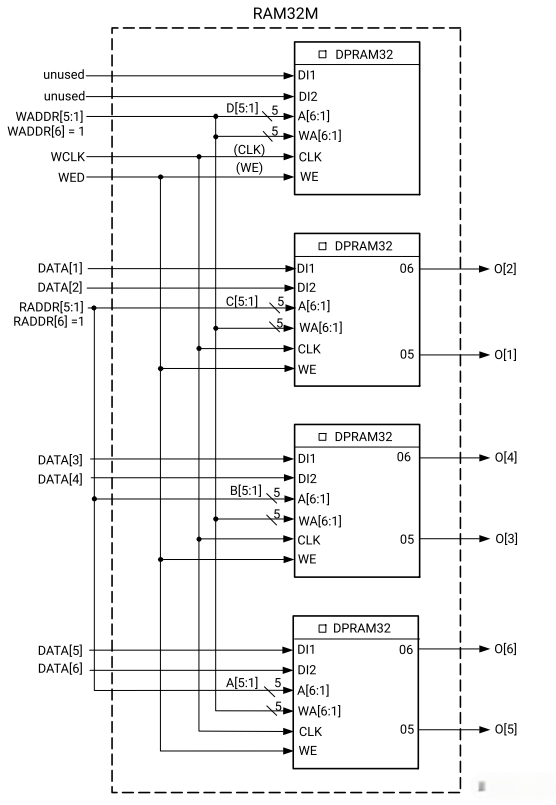

下图为四个LUT的布局,从图中可以知道,四个LUT的写地址相同,LUTD的读写地址相同,LUTA、LUTB、LUTC的读地址独立,这决定了LUT可配置为四种分布式RAM。

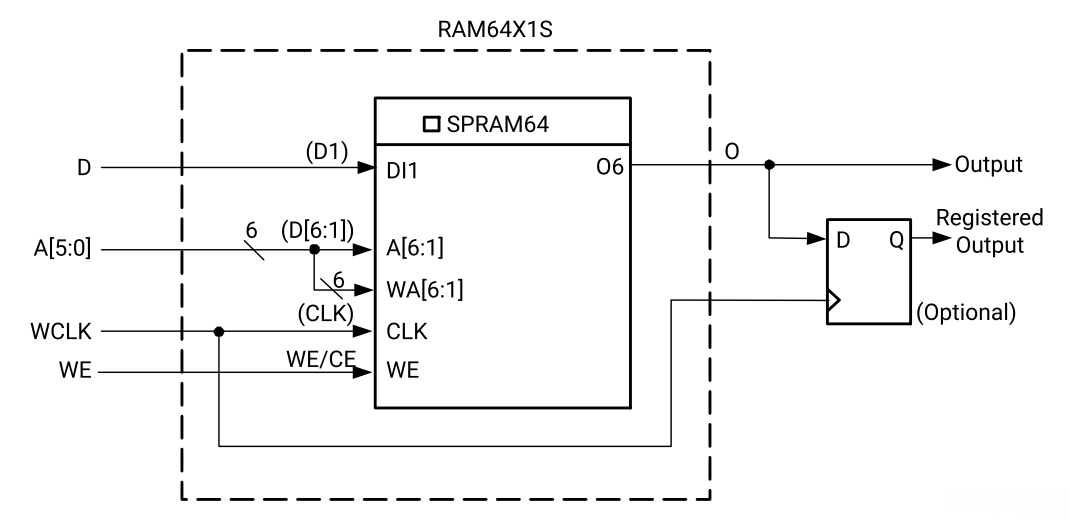

1、单端口模式

单端口用于同步写入和异步读取的公共地址端口,读取和写入地址共享同一地址总线。

64×1

64×1

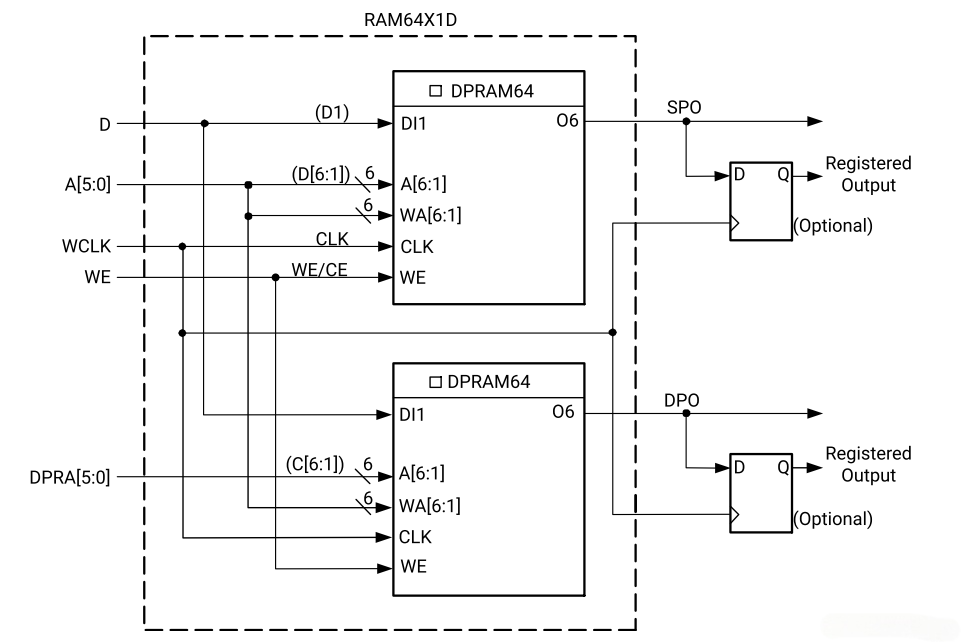

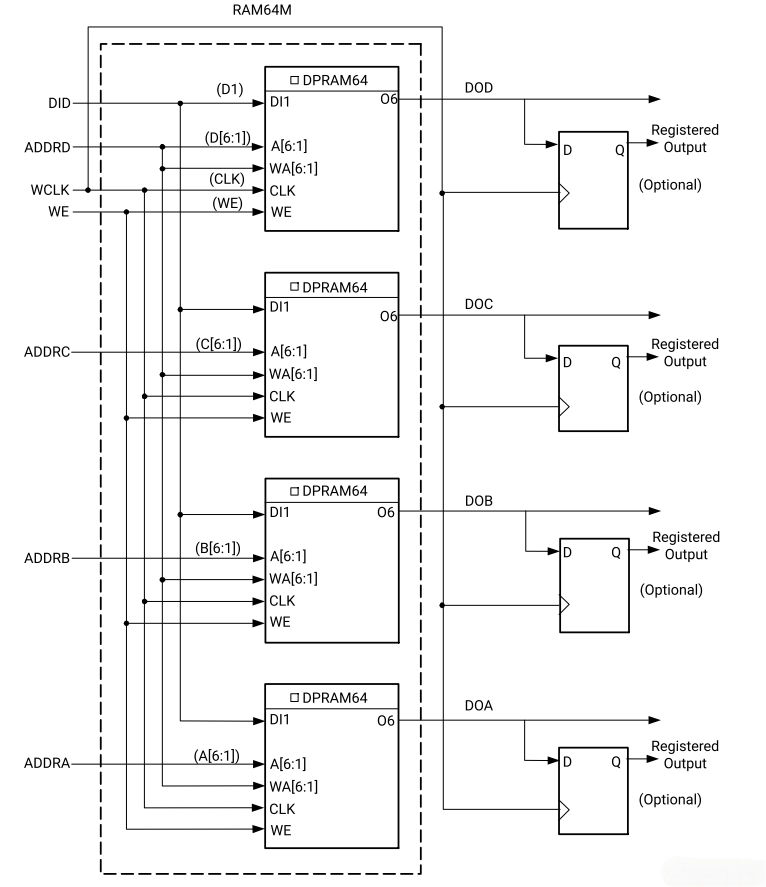

2、双端口模式

一个端口用于同步写入和异步读取,一个端口用于异步读取。

64×1

64×1

3、简单双端口

一个端口用于同步写入,一个端口用于异步读取。

32×6

32×6

4、四端口模式

一个端口用于同步写入和异步读取,三个端口用于异步读取。

64×1

64×1

最后,需要说明的是,除了以上介绍的RAM,LUT也可以当ROM使用,原理类似,此处不再赘述。要想LUT作为存储器使用,代码中不能使用复位。

二、FPGA编程仿真验证

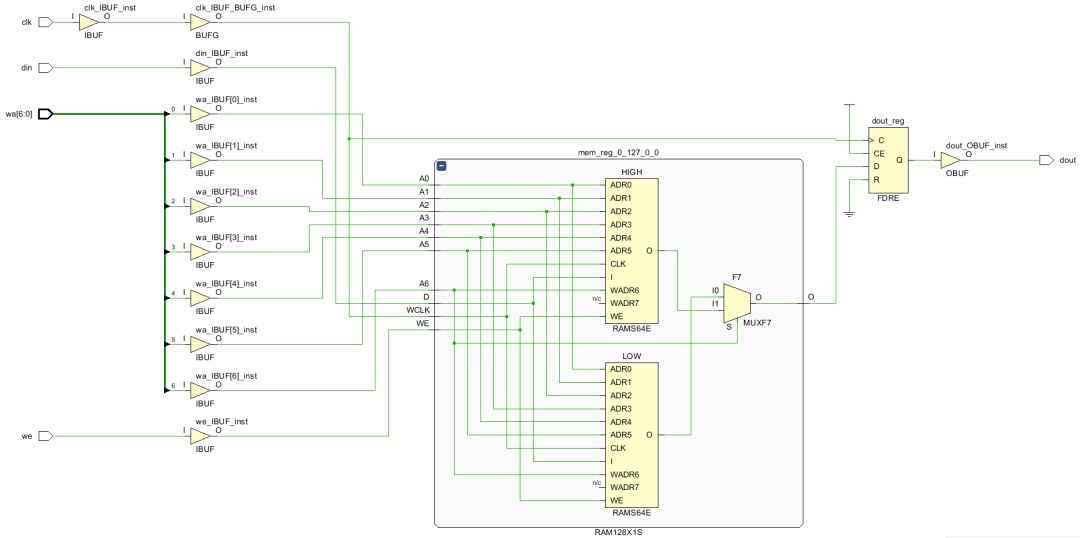

下面是一段128×1的单端口RAM的verilog代码。

module ram128x1 ( input wire clk, // 写时钟 input wire we, // 写使能 input wire [6:0] wa, // 地址 0..127 input wire din, // 写数据 1bit output reg dout // 读数据 1bit(异步读) ); reg mem [0:127]; always @(posedge clk) //写 begin if (we) mem[wa] <= din; end always @(posedge clk) //读 begin dout <= mem[wa]; end endmodule

实现后的电路如下图,可见128×1的RAM是由两个LUT加一个选择器组合形成的。由于代码是同步读出,所以输出端加了一级寄存器。

0

0