半导体先进制程工艺逐步趋于极限, 继续沿摩尔定律发展的脚步放缓, 而扇出型晶圆级封装( Fan-out Wafer Level Packaging, FOWLP)通过晶圆重构的方式突破了传统扇入封装的 I/ O 引出端的数量限制, 并利用多层再 布线(Redistribution Layer, RDL)等技术, 缩小引脚间距, 减薄封装厚度, 降低高频信号传输损耗, 从而进一步提升 芯片集成度。近年来已在消费电子、 高性能计算等领域逐渐发展成为具有代表性的先进封装技术, 是接续摩尔定律 的关键技术。但 FOWLP 的可靠性问题随着其结构精密和生产流程复杂而日益突出。结合 FOWLP 近期技术发展和 应用的现状, 总结了发展趋势; 从 FOWLP 结构的工艺缺陷和失效模式出发, 阐述了 FOWLP 的工艺流程和重点工 艺环节; 根据不同失效类型, 系统归纳了引发失效的物理效应和物理模型; 最后, 介绍了提升 FOWLP 结构可靠性 的工艺调整和优化设计方法。

随着先进纳米制程已逼近物理极限, 在日益增长 的性能需求与摩尔定律逐渐失效的矛盾影响下, Intel、 NVIDIA、 台积电、 AMD 等老牌半导体企业纷纷加大 了叠层封装(PoP)、 FOWLP、 硅通孔(TSV)等先进封 装领域的投入, 要借助先进的封装技术实现更高性能、 更低耗电量、 更小体积、 信号传输速度更快的产品。

作为先进性封装研究的重要成果之一, FOWLP 在 移动及可穿戴设备中大获成功, 在高性能及云计算、 自动驾驶和物联网( IoT)中也得到了应用。FOWLP 具 有异质集成、 3D 堆叠的潜力, 可以与多种先进封装技 术相互组合, 是未来先进封装技术演进的基石 。FOWLP 已在商用产品中有了扎实的使用基础, 助力可 编程逻辑阵列 FPGA、 中央管理器 CPU、 数字信号处 理模块 DSP 等关键元器件向高密度、 高性能和高可靠 性发展, 随着军事、 航空、 航天等领域逐渐向小体积、 轻质量、 高可靠性的方向发展, FOWLP 将在军用及航 空航天用器件的封装变革中起到关键作用 。

目前先进制程工艺的进步速度逐渐放缓, 且在当 前国际背景下, 受美、 日、 荷等国半导体相关行业的 出口限制, 国内先进制程工艺难以短时间内实现有效 突破。加强对以 FOWLP 为代表的先进封装技术的发 展和应用, 可以有效促进集成电路在一定行业应用范 围内向着更高集成度的方向继续发展, 满足相关应用需求。

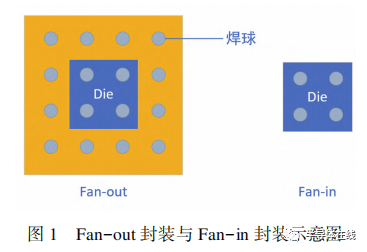

在 FOWLP 中存在两个重要概念, 即扇出型封装 和晶圆级封装。如图 1 所示, 扇出型封装(Fan-out)是 与扇入型封装(Fan-in)对立的概念, 传统扇入型封装 的 I/ O 接口均位于晶粒(Die)的下方, I/ O 接口的数量 受限于芯片尺寸的大小, 随着芯片技术的发展, I/ O 接口的数量已经成为制约芯片性能发展的短板之一, 而扇出型封装则可以利用重布线(RDL)技术和模塑化 合物提供的额外芯片面积, 将 I/ O 接口分布在晶粒之 外, 大大增加了芯片 I/ O 接口数量, 从而满足芯片日 益增长的吞吐需求 。传统封装往往是将晶粒从晶圆 (Wafer)上切割下来, 再分别对晶粒进行封装, 而晶 圆级封装则另辟蹊径, 先将晶圆进行整体封装, 再进 行切割, 更适合集成电路的大规模批量生产。

纵观集成电路封装技术的发展历程, 伴随着封装 结构的布线密度和 I/ O 接口数量的不断上升, 封装结 构和工艺流程日趋复杂, 引发的可靠性问题也逐渐增多 。本文第一章介绍了近几年国内外 FOWLP 技术发 展和应用的现状, 介绍了国内半导体厂商特色封装技 术和先进封装技术发展水平。第二章列举了 FOWLP 的关键工艺和常用的可靠性测试方法。第三章介绍了 学术界对晶圆翘曲、 芯片偏移两种工艺缺陷和重布线 层分层、 焊球开裂两类失效模式的失效分析成果。第 四章介 绍 了 基 于 失 效 分 析 形 成 的 失 效 物 理 模 型 对 FOWLP 的工艺和设计进行可靠性优化的部分典型案 例。最后展望了进一步提升 FOWLP 产品可靠性的研究方向。

1 行业发展及应用现状2016 年, 台积电(TSMC)经过在先进封装技术上 近十年的布局和技术沉淀, 在 FOWLP 领域开发了集 成扇出型(Integrated Fan-out, InFO)封装技术[ , 并 成功应用于苹果 iPhone7 系列手机的 A10 应用处理器 , 之后苹果每一代手机应用处理器都采用台积电 的集成扇出型封装技术, 帮助台积电拿下苹果处理器 芯片制造和封装订单。

在先进封装领域, AMD 公司将多项先进封装技术 投入商用。Chiplet, 中文译名芯粒或晶粒, 是近期集 成电路业界的热点话题, Chiplet 是指预先制造好、 具 有特定功能、 可组合集成的晶片, 该技术可以缩小单 颗芯片面积, 提高良品率, 有助于企业控制生产成本 和提高迭代速度。如何实现多芯粒之间的高速互联是 实现 Chiplet 的技术难点, 而 FOWLP 技术的高密度重 布线工艺满足多芯粒之间高速互联的需求。FOWLP 技 术的发展是 Chiplet 技术走向商用的先决条件。AMD 公司在扇出型封装技术上投入巨资, 并且在商业竞争 中率先使用先进的 FOWLP 技术, 该技术路线帮助 AMD 公司在 CPU 和 GPU 领域追赶行业先驱 Intel 和 NVIDIA。在 2019 年发布的 7 nm Zen2 架构锐龙处理器 中, AMD 公司将 CPU 芯片拆分成 CCD 和 cIOD 两部分, 其中仅有负责逻辑运算的 CCD 使用台积电 7 nm 工艺, 对性能要求较低的 cIOD 部分使用了 12 nm 工 艺。Zen2 架构意义重大, 实现了对同期 Intel 产品的性 能追赶, 为提升 AMD 在德国等多国 CPU 市场占有率 奠定了基础。

在 CPU 领域通过先进封装技术取得优势的 AMD 公司也试图将 FOWLP 技术引入到 GPU 领域, AMD 公司于 2022 年 12 月 13 日向市场推出了使用 RDNA 3 架构的 Radeon 7900XTX 显卡, AMD 将显卡核心 Big Navi 3x 拆分为一个 GCD 和六个 MCD, 与 AMD 在 Zen 架构的做法相同, 负责逻辑计算的 GCD 使用了台 积电 5 nm 工艺, 面积为 300 mm 2 , MCD 使用了台积 电 6 nm 工艺, 单颗面积为 37 mm2 。得益于更小的芯 片带来更高的良率, 以及 MCD 芯片成熟工艺, 使得 AMD 的 Big Navi 3x 核心在性能对标竞争厂家 NVIDIA 的 AD102 核心的同时实现了较好的成本控制。

Intel 公 司 结 合 自 身 在 基 板 领 域 的 积 累, 推 出 EMIB(Embedded Multi-Die Interconnect Bridge), 中文 译名为嵌入式多核心互联桥接。EMIB 工艺建立在标 准封装构造流程的基础上, 附加了创建 EMIB 腔的步 骤。连接桥位于空腔中, 并用粘合剂固定在适当的位 置。添加介电层和金属堆积层, 然后进行通孔钻孔和 电镀。作为 CPU 行业的巨头, Intel 公司正试图参与 GPU 市场竞争。在 2022 年 8 月的半导体行业会议 Hot Chips 34 上, Intel 公司公开了一套名为 Ponte Vecchio 的服务器 GPU 架构。Intel 公司作为 GPU 行业的后来 者, 在最新推出的 GPU 产品中使用了比 AMD 公司更 先进的封装技术。Intel 公司称 Ponte Vecchio 内部同时 混用 Intel 7 和台积电 N7 / N5 等多个工艺节点, 并使用 了多达 11 处的 EMIB 结构以实现内部高速互联。

在超算领域, 特斯拉于 2021 年公布了 Dojo 芯片 的概念图, Dojo 是神经网络训练优化超级计算机芯 片, 该芯片将首次使用台积电 InFO_ SoW (System-on -Wafer)技术 , Dojo 使用 6 层 RDL, 将整块 12 英寸 重构晶圆安装在散热盘上, 散热盘可以为芯片提供刚 度并将散热能力从 7000 W 提升至 15000 W。2022 年, FOWLP 技术在 GPU 领域得到了快速的 推广应用, 2021 年底到 2022 年初, 马斯克在推特上 发布多篇推文公布特斯拉自研超算 GPU 芯片, 以取代 特斯拉采购的 NVIDIA 芯片。

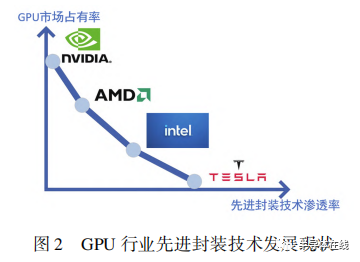

2022 年 8 月 Intel 公布全 新服 务 器 GPU 架 构, 12 月 AMD 发 售 消 费 级 GPU7900XTX, 这三家公司为了追赶行业先进水平, 使用的先 进 封 装 技 术 越 发 激 进, 但 市 占 率 最 高 的 NVIDIA 公司仍采用了较保守的封装方案。无论是 CPU、 GPU 还是其他集成电路产业, 均呈现出越是行 业后发者, 使用的封装技术越先进的趋势。如图 2 所 示, 这一趋势在市场规模最大、 竞争最激烈的 GPU 市 场表现尤为明显。并且, 各公司发展先进封装技术的 战略也取得了不错的效果, NVIDIA 公司各类 GPU 产 品线均受到巨大挑战。观察这种趋势对国内半导体行 业的发展很有参考价值, 促进 FOWLP 等先进封装技 术的发展和应用对于试图参与 GPU 市场竞争的集成电 路企业是很有意义的。

在宇航领域, NASA 在 2015 年公布的封装技术路 线图 中 将 2. 5D/ 3D - TSV 技 术 纳 入 封 装 技 术 路 线, 2018 年启动对 2. 5D 封装产品的考核方案和路线图。在美国国家航空航天局电子零件和包装计划(National Aeronautics and Space Administration Electronic Parts and Packaging, NEPP)的赞助下, 美国加州理工学院喷气 动 力 实 验 室 ( California Institute of Technology Jet Propulsion Laboratory, JPL) 的 Ghaffarian 通过一系列 的可靠性实验系统论证了 2. 5D 封装产品的可靠性, 他认为 FOWLP 产品拥有更小的体积重量、 更大的逻 辑运算和存储能力, 而且其可靠性鉴定结果足以满足 NASA 对空间飞行器电子元器件的可靠性要求, 并希 望他的研究成果可以促进 NASA 对 FOWLP 等先进封 装技术的使用。

我国半导体封装企业也在 FOWLP 领域取得了一 系列创新成果。硅基扇出型晶圆级封装 ( Embedded Silicon Fan-out, eSiFO) 是 2015 年由华天科技于大全 教授提出。硅基扇出型封装这一技术路线相比于树脂 扇出型封装, 具有成本低、 翘曲小、 布线密度高、 散 热良好和制程简单等优势, 更容易实现大芯片系统集 成。该工艺被使用于电源管理芯片、 射频收发器芯片、基带处理器和高端网络系统等多种应用领域,

厦门云天半导体开发了 eGFO 嵌入式玻璃封装技 术。玻璃绝缘性好, 高温下不易膨胀, 透光性强, 适 合高频的射频应用和光电应用。玻璃上可以直接做光 路, 满足光电共封装的需求, 光电射频领域也是云天 eGFO 技术的主要应用领域。但是玻璃具有易开裂的 特性, 在玻璃上开孔和挖出嵌埋区域工艺难度高、 效 率低。产品良率是目前制约厦门云天使用玻璃作为载 体的最大因素。

中电五十八所的晶圆级封装工艺平台是目前国内先进、 自主可控的高可靠 12 英寸(兼容 8 英寸) 晶圆级制造加工线, 同时也是国防科技工业认可的信息处 理微系统加工制造平台。自 2017 年通线以来, 平台已 经具备高可靠 12 英寸的晶圆级再布线制备、 晶圆级凸 点制备、 圆片重构等多项晶圆级扇出型集成技术。部 分工艺技术能力(晶圆级封装尺寸、 凸点直径等)达到国际领先水平。同时具备有铅低辐射凸点(Bump) 制 备、 单芯片批量化凸点生长以及可重构三维封装等特 色服务, 可满足军用及宇航长寿命使用要求, 已先后 为国内多家用户单位提供了 GNC 飞行控制、 AD/ DA 集成、 信号截取处理模块等数字信息处理微系统产品 的加工服务, 满足了相关微系统产品小型化、 高性能、 高可靠的应用需求。

航天 772 所通过近几年技术攻关和自主研发, 已 初步具备 小 尺 寸 多 芯 粒 硅 基 集 成 技 术 能 力。针 对 Chiplet 芯粒集成多级互连要求, 面向 40 μm 以下超微 凸点键合, 突破面阵列固态互连等关键技术, 实现了 低温焊接、 高温服役的全流程稳定工艺; 并采用耐湿 “内防护” 结构以及改性耐高温材料, 实现了节距小 于 100 μm, 凸点数大于 10000 个的均匀沉积和致密防 渗集成工艺。

通富微电 2021 年披露其在高性能计算领域建成了 国内顶级 2. 5D/ 3D 封装平台 ( VISions) 及超大尺寸 FCBGA 研发平台, 且完成了高层数再布线技术的开 发, 具备大规模生产 Chiplet 封装能力, 目前在 CPU、 GPU、 服务器领域 5 nm 即将量产。其 Fan-out 技术已 经达到世界先进水平, 高密度扇出型封装平台完成 6 层 RDL 开发。

XDFOI 是长电科技 2021 年推出全系列极高密度 扇出型封装解决方案, 并于 2022 年下半年量产。该封 装解决方案是新型无硅通孔晶圆级极高密度封装技术, 相较于 2. 5D 硅通孔(TSV) 封装技术, 具备更高性能、 更高可靠性以及更低成本等特性。该解决方案在线宽 或线距达到 2 μm 的同时, 可实现多层布线层, 另外, 采用了极窄节距凸块互联技术, 封装尺寸大可集成多 颗芯片、 高带宽内存和无源器件。XDFOI 主要集中于 对集成度和算力有较高要求的 FPGA、 CPU、 GPU、 AI 和 5G 网络芯片等应用产品提供小芯片 (Chiplet) 和异 质封装 (HiP) 的系统封装解决方案。 2022 年 7 月 22 日, 长电科技发文称, 公司在先进封测技术领域取得 新的突破, 实现 4 nm 工艺制程手机芯片的封装以及 CPU、 GPU 和射频芯片的集成封装。

我国 FOWLP 技术与国外先进水平相比差距较小, 且各企业均有自身的特色技术, 但在高密度重布线和 超大面积扇出型封装技术等领域尚有差距。

2 关键工艺和可靠性评价FOWLP 的工艺流程复杂, 包括晶圆重构、 塑封、 重布线等, 每一步关键工艺都会对封装可靠性造成严 重影响。

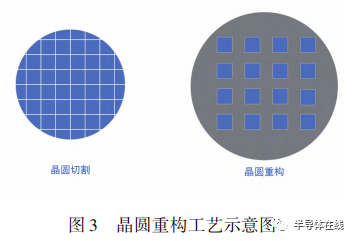

晶圆重构是指将从晶圆上分割下来的晶粒重新贴 装在临时载体上形成重构晶圆, 如图 3 所示。晶圆重 构技术要求较好的定位精度, 既需要良好的粘贴强度, 也需要易于剥离, 否则会导致芯片偏移 。

塑封工艺可以保护芯片并扩展芯片面积, 环氧塑 封料会在受热后液化, 包裹住晶粒, 并在冷却后固化。环氧塑封料的热膨胀系数与其他材料之间存在较大的 不匹配, 注塑时产生的液体流动也可能会改变晶粒位 置, 造成晶圆翘曲和芯片偏移。

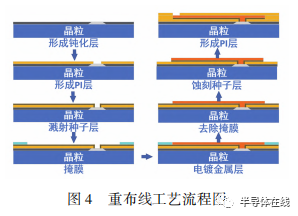

重布线技术是实现扇出效果的关键技术, 如图 4 所示, 该技术首先在晶粒表面覆上钝化层和 PI 层, 再 通过金属溅射、 掩膜曝光的方法制造金属层图案, 并 使用电镀法填充金属层, 反复多次, 在晶粒和塑封料 表面交替制作金属层和聚酰亚胺层, 最终形成多层重 布线层, 实现对 I/ O 接口的重新排布。由于金属和聚酰亚胺热膨胀系数不同, 在温度变化时若重布线层 强度不足会引发重布线层开裂。

FOWLP 在应用过程中常见的失效模式包括重布 线层分层和焊球开裂。菊花链测试链路可以实时监测 和定位 FOWLP 失效[9] , 便于后续对失效封装结构失 效分析。温度循环试验和冲击试验可以充分暴露潜在 失效。

菊花链(Daisy Chain)测试链路是表征先进封装结 构可靠性的常用方法, 它可以高效率地实时监测封装 结构是否在环境测试中发生失效, 并锁定发生失效的 大概位置。菊花链测试链路可以在 I/ O 接口中建立多 条链路, 一旦封装结构在某处发生失效, 就会改变该 处的横截面积、 长度和电气参数, 失效位置所在链路 的电流也会因为电阻值的改变而变化, 从而实现对封 装结构失效状态的监控和失效位置的估计。

在发现失效现象后可以使用超声波扫描电子显微 镜 (SAM)、 扫描电子显微镜 ( SEM) 、 能量色散 X 射线光谱仪(EDX)、 X 射线能谱仪 (EDS)等工具和手 段对失效点位进行定位和失效分析。超声波扫描电子 显微镜和能量色散 X 射线光谱仪可以精准定位失效位 置。扫描电子显微镜可以得到失效点位的清晰图像, 有助于了解断裂、 分层、 错位等现象的具体原因。通 过能谱分析对失效点位附近材料的成分进行分析, 可 以追溯因工艺流程中原材料纯度不足、 对上一工艺环 节残余物清洗和剥离不够充分或生产环境不够纯净等 原因导致的失效。

温度循环试验和冲击试验可以使潜在的布线层分 层和焊球开裂失效充分暴露。重布线层中的金属层和 聚酰亚胺层在温度循环测试时反复膨胀收缩, 二者热 膨胀系数不同, 若重布线层强度不足则会开裂。冲击 和温度循环导致焊球处发生热应力和机械应力集中, 若产品设计不合理或封装工艺不达标, 则会导致焊球开裂。根据联合电子器件工程委员会( Joint Electron Device Engineering Council, JEDEC) 发布的有关标准 JESD22-A104, 封装可靠性测试中温度循环试验的 热范围为-40~ 125 ℃, 循环测试的次数均为 1000 次, 冲击测试的强度为 1500 g / ms。在实际工作中, 可靠 性环境试验会根据集成电路产片生命周期中所经历的 环境进行调整, 比如航空航天电子产品会对冲击强度 测试进行加严, 汽车电子产品可能会扩大温度循环范 围或增加高温存储实验(HTS)等项目。有些集成电路 产品在生产流程中会使用一些特殊工艺, 产品可能会 经历极端环境变化, 这也需要调整测试环境。有针对 性的可靠性测试有助于精准的评价封装结构的可靠性, 从而合理地对结构和工艺或划定适应的产品贮存、 运 输和工作环境范围。

3 主要工艺缺陷和失效模式分析晶圆翘曲、 芯片偏移两种工艺缺陷和重布线 层分层、 焊球开裂两类失效模式的作用机理并建构物 理模型是进行工艺改进和可靠性优化改进的基础。

3. 1 晶圆翘曲

晶圆翘曲是指重构晶圆在加工过程因热机械应力 的累积而在宏观上产生翘曲。晶圆翘曲会降低后续掩 膜光刻的工艺精度, 限制再布线层密度的提升。翘 曲产生的应力易在中介层或焊点处集中, 造成焊球开 裂脱落和中介层分层。晶圆尺寸越大, 晶圆所受的热 和机械应力越强, 局部曲率越高, 翘曲现象越严重。随着大尺寸晶圆在晶圆级封装的应用, 晶圆翘曲问题 已经成为制约 FOWLP 发展的突出问题。

由于晶圆表面易被划伤, 业界通常采用光学手段 对晶圆翘曲进行测量, 依据原理可以大致划分为光学 干涉测量 和 激 光 扫 描 测 量, 前 者 包 括 影 子 云 纹 法 (Shadow Moire)、 投影云纹法( Projection Moire) 和泰 曼-格林干涉法(Twyman-Green)等, 通过光栅干涉 图像表征晶圆曲率, 后者则是通过激光对晶圆整体进 行扫描定位, 最后通过计算机拟合出晶圆翘曲的情况。

采用合适的方法对重构晶圆所含材料进行测量和 表征是分析引发晶圆翘曲多种应力的前提。Cheng 等使 用 差 示 扫 描 量 热 法 ( Differential Scanning Calorimetry, DSC ) 和 动 态 力 学 分 析 ( Dynamic Mechanical Analysis, DMA)评估固化状态, 使用热机 械分析仪( Thermomechanical Analyzer, TMA) 表征了 环氧塑封料的杨氏模量和热膨胀系数, 为分析各类应 力的强度和不同翘曲形态的成因提供了有力支持。

环氧塑封料固化引发的体积收缩和不同材料的热 膨胀系数不匹配被公认为是造成晶圆翘曲的最主要原因, 但随着研究的深入, 尤其是通过分析传统理论 模型和实际结果之间的偏差, 近年来发现了更多影响 晶圆翘曲的因素。Dijk 等和 Chiu 等发现硅的各 向异性和环氧塑封料的粘弹性松弛效应对翘曲也有一 定影响, 固化工艺之后的工艺环节, 尤其是再布线和 植球等存在剧烈温度变化的工艺会对晶圆翘曲产生影 响。Chiu 还通过实验和建模分析认为环氧塑封料的化 学收缩对翘曲的影响微不足道。Cheng 等通过分 析环氧塑封料的固化过程发现重力会对晶圆翘曲产生 影响。

张振越等基于双层圆形板弯曲理论与复合材料 等效方法, 提出 FOWLP 圆片翘曲理论解析表达式。实现对翘曲的快速预测。Chen 等使用频域动态力 学分析表征了 EMC 和 PI 的线性粘弹性, 将粘弹性模 型用于对固化结构的有限元分析, 实现了对晶圆翘曲 的精准预测。Li 等结合材料微观力学模型, 针对异 构集成结构建立物理模型, 通过建模调整参数使得 8 英寸晶圆翘曲控制在 2 mm 以内。

近几年来, 业界深入分析了晶圆翘曲的成因, 表 征了翘曲程度和引发翘曲的应力, 支撑了业界工艺流 程参数优化 。

3. 2 芯片偏移

芯片偏移是指晶粒偏离应有位置。芯片偏移现象 可以通过高倍显微镜观察发现, 这既可能是晶圆重构 精度不足造成的, 也有可能是后续工艺环节产生的应 力导致的。引发芯片偏移的应力主要包含两种。主要 的一种是由固化成型期间环氧塑封料的流动诱导阻力 引起的流体流动(Fluid Flow, FF)。另一个是由封装的 热膨胀/ 收缩、 环氧塑封料的固化收缩和晶圆翘曲引起 的热机械(Thermo-Mechanical, TM)应力 。与晶圆 翘曲类似, 芯片偏移也会降低再布线工艺中光刻的工 艺精度, 并导致芯片链路产生开路。

为了分析两种应力对芯片偏移的影响, 业界通过 建模和试验对两种应力的强度和作用机制进行了分析。Cheng 等基于某种环氧塑封料建立了流体动力学 模型用以研究液体流动对芯片偏移的影响, 发现重构 晶圆边缘处的晶粒芯片偏移最为严重, 分析认为热机 械效应和诱导阻力造成的应力具有相似的作用机制, 都是越靠近边缘应力越大。Wu 等通过建模比较了 热机械应力和流体流动的强度, 认为热机械效应对芯 片偏移产生更多影响。Ouyang 等根据目前已经发 现的影响芯片偏移的应力, 针对聚二甲基硅氧烷这一 特殊的塑封料建立流体动力学模型, 实现对塑封过程 中翘曲变化的预测。Shao 等[26]通过比对不同种类粘合 剂的粘附强度和使用不同粘合剂对芯片偏移产生的影 响, 发现晶圆重构工艺中临时载体的黏附力不足是造 成芯片偏移问题最直接的原因。

相较于晶圆翘曲, 引发芯片偏移的应力种类较少, 芯片偏移的失效机制较为清晰。

3. 3 焊点开裂

由于 FOWLP 的 I/ O 接口数量越来越多, FOWLP 的尺寸和焊点密度均有所提升。在焊点的体积变小的 同时单个焊点所受应力越来越高, 所以焊点的可靠性 问题日益突出。

对焊点进行建模有助于对焊点可靠性进行预计, 便于工艺改进和设计优化, Lau 等建立了非线性、 时间和温度相关的三维有限元模型, 采用线性加速因 子将测试条件下的焊点可靠性映射到操作条件下的焊 接点可靠性, 得到了置信度为 90%的封装特征寿命。Wang 等基于能量法描述和预测焊点形状, 当液体 达到静态平衡时, 其总能量趋于最低, 表面积趋于最 小。液体的能量主要包括表面张力能、 重力能和外能。根据总能量, 可以计算重力方向上的恢复力, 进而估 算焊球的形状和高度, 并基于 Coffin-Manson 应变的 经验模型估计焊点的疲劳寿命。Lee 等建立了一种 非线性模拟方法, 用于研究制造过程和热循环实验的 耦合效应。在有限元建模中分析了焊料凸台的塑性和 蠕变行为, 研究了 SnAg 焊料凸台中累积的非弹性应 变。还对相关几何尺寸和底部填充材料进行了参数化分析。

在不同环境压力下, 焊球的失效模式表现不同。Cho 等[通过可靠性试验发现在跌落试验中, 焊球界 面断裂和 PCB 焊盘出现凹坑是主要失效模式, 而在温 度循环试验中, 焊球界面断裂和重布线层出现裂纹是 主要失效模式。

除此之外, 在对焊球质量的批量化监测方面, Lu 等用扫描声学显微镜对样本进行测试, 并使用聚类 模糊 C 均值(FCM)算法对焊点进行识别。训练所得学 习模型可应用于高密度焊点可靠性的快速检测。业界对焊点可靠性的研究相对成熟, 对引发焊点 应力集中的作用机制已有充足的探索, 建立了可信度 较高的焊点物理模型。

3. 4 重布线层分层

重布线 层 中 最 常 用 的 有 机 材 料 包 括 聚 酰 亚 胺(Polyimide, PI)、 聚苯并恶唑(Polybenzoxazole, PBO) 和苯并环丁烯(Benzocyclobutene, BCB), 除此之外还 有酚醛树脂等材料, 其中 PBO 机械强度最高但是热膨 胀系数过高, BCB 胜在优良的电学性能, 但是机械强 度最差。Gao 等[32]将酚醛树脂等三种材料与 PI 进行比 较, 认为 PI 具有超过 30%的优异伸长率和 52×10 -6 / K 的热膨胀系数, 是目前性能最均衡的 RDL 有机材料。PI 是目前重布线层中最常用的有机材料。但是 PI 固化 温度过高, 普通的 PI 固化温度超过 300 ℃, 经过改良 的低温固化 PI 的固化温度也在 200 ℃以上, 对工艺设 计的优化要求较高。Okada 等[33] 通过试验比较了两种 PI、 PBO 和酚醛树脂在铜表面的临界能量释放率, 并 根据实验曲线建立了可以模拟任意温度下分层可能性 的仿真模型。

重布线层分层常发生在温度循环测试之后, 重布 线层不同材料层经历反复的热胀冷缩, 材料间界面的 疲劳应力导致开裂。冲击测试中也会发现重布线层分 层现象, Lau 等通过试验估算了重布线层的特征寿 命, 并发现封装最大应力出现在受到冲击后的 0. 0023 s, 位置在封装四角, 最下层的重布线层所受应力最 大, 易发生开裂现象。

重布线层分层是扇出型封装中常见的失效模式, 但是重布线层结构和重布线工艺流程复杂, 结构和材 料个性化强, 重布线层仿真难度高, 需要针对不同的 封装结构单独进行分析。

4 工艺改进和可靠性优化设计通过实验和仿真可以快速对工艺进行迭代, 优化 工艺参数, 从而提升产品良率。依靠成熟的失效物理 模型对封装结构进行优化是改善产品可靠性的有效方法。

4. 1 工艺改进

晶圆翘曲的曲率、 形状和方向在制造工艺中经历 了剧烈的变化, 其中最大翘曲并没有发生在其工艺流 程结束时, 而是发生在去载流子环节, 所以对于高产 率工艺操作, 应连续监测和有效控制每个工艺步骤的 翘曲, 而不是仅进行末端监控。Wu 等使用可调温 度热室模拟重构晶圆在后续工艺环节中经历的温度变 化, 并改进了一种干涉测量工具, 实现对晶圆翘曲的 全局热变形分析, 从而改进工艺参数。Cheng 等通过实验发现晶圆厚度与翘曲程度并非简单的线性关 系, 当晶圆厚度低于 0. 6 mm 时, 晶圆越厚, 材料热 失配导致的晶圆翘曲程度越高, 但是由于晶圆本身的 弯曲刚度与晶圆厚度的平方成正比, 所以当晶圆厚度 超过 0. 6 mm 时, 晶圆的弯曲刚度会随厚度快速上升, 从而抑制晶圆翘曲。通过对生产工艺的观察, Cheng 等还注意到重构晶圆上晶粒间距越大, 晶粒边长越长, 翘曲越小。

引发芯片偏移的两大要素分别是液体流动和热机 械效应。通过降低塑封工艺速度和模具固化温度、 缩 小晶粒间距和晶粒厚度以及增加环氧塑封料的厚度, 可以减少液体流动带来的阻力, 从而减少芯片偏移。通过缩小环氧塑封料厚度, 使用低热膨胀系数的临时 载体, 增加晶粒的间距和厚度, 可以减少热机械效应 引起的芯片偏移。可以看到减少液体流动阻力的措施 与减少热机械效应的措施之间存在冲突, 所以需要对 工艺参数进行权衡。针对不同的封装结构反复建模和 试验, 才能使芯片偏移最小化 。

Zhang 等通过大量的材料学试验寻找植球工艺 的最佳参数, 在低焊接温度和短焊接时间下, 焊点和 焊盘之间的冶金反应不足, 剪切力低。随着焊接温度 和时间的增加, 焊料球和焊盘之间的反应更完全, 机 械性能逐渐提高。然而, 随着峰值温度和持续时间的 增加, 焊料球的氧化程度增加, 导致焊点出现孔洞, 焊球下金属间化合物厚度增加, 导致脆性增加, 剪切 力降低。经过权衡, 在 260 ℃下, (Cu, Ni)6Sn5 晶体 呈现规则的分布, 金属间化合物达到一定的密度, 同 时也较少产生孔洞, 所以 260 ℃ 持续 10 s 是一个比较 优秀的焊接参数。

重布线工艺中生产环境洁净度不足或对前一工艺 环节残余物清洗不彻底, 导致重布线层内部出现沾污 是导致重布线层分层的原因之一。在工艺环节中应严 格监控生产环境, 及时使用能谱分析技术分析重布线 层分层的封装器件, 找出引发分层的有机化合物并追 溯来源, 并及时整改是十分有必要的。在重布线工艺 中选择热膨胀系数与金属层匹配度较高、 分界层粘性 大的有机材料是减少分层的关键。减材制造是制备重 布线层的传统方法, Roshanghias 等[38]尝试使用打印技 术实现重布线层的增材制造, 认为新的工艺方法在抵 抗重布线层分层问题上具有潜力, 并讨论了增材制造 技术面临的工艺难点。

4. 2 可靠性优化设计

除了进行工艺参数的改进, 通过对封装结构进行 可靠性优化设计也能有效提升 FOWLP 的可靠性。

Tsai 等发现, 在 FOWLP 上粘贴一个金属框架 可以降低封装翘曲和底部焊点所受应力。但是金属框架的热膨胀系数和金属框架粘结剂的弹性模量会对效 果产生影响, 所以应根据情况谨慎选择金属框架材料, 粘合剂弹性模量应控制在 50 MPa 以下。

晶圆翘曲和芯片偏移均与模塑化合物的性能相关, C an 等分析了使用液体模塑化合物 (Liquid Molding ompound, LMC)取代 EMC 的可能性, LMC 流动性 强有助于抑制晶圆翘曲且成本更低, 但是对模塑工艺 的工艺控制要求更高。Andriani 等[通过在 EMC 中添 加六方氮化硼来改善 EMC 的热力学性能, 并分析了 不同浓度的六方氮化硼对 EMC 热力学性能的影响。

Jung 等通过在环氧塑封料中嵌入不同形状的银 片有效降低翘曲, 改善芯片散热。环氧塑封料导热性 差, 在高温固化时固化速度不均匀, 加入银片可以使 固化速度更加均匀, 从而减轻翘曲。位于晶粒正上方 扇入区域的银片还可以显著改善散热, 但在扇入区域 嵌入银片也会增加封装整体厚度。

通常认为使用散热器可以降低芯片的实际工作温 度, 有助于缓解因热机械效应导致的封装失效。但是 Nayini 等将使用散热器和不使用散热器的封装结构 进行了对照, 发现加装散热器可能会导致焊点寿命下 降, 因为散热器会限制芯片变形, 将芯片内部因热失 配产生的应力传递给焊点。虽然高温会减少焊点寿命, 但是不合适的散热方法可能会进一步加剧可靠性问题。

Lee 等发现上、 下焊盘直径和缓冲层厚度显著 影响扇出型封装焊点的可靠性寿命。当上焊盘大于下 焊盘时, 焊点的可靠性更高, 推荐的上下焊盘大小比 例为 1 ∶ 0. 72, 较厚的缓冲层分担了焊点的应力集中, 从而对焊点的可靠性寿命产生了积极影响。较薄的芯 片厚度可以释放焊点的应变芯片, 减小焊料凸块的非 弹性应变增量, 低杨氏模量底部填充材料也可以起到 应力缓冲的作用。

Lee 等提出了三种无直角转弯的重布线层设计 方案, 并与含有直角转弯布线的原始方案进行对比, 发现合理的重布线层设计方案可以避免局部积热, 改 善重布线层的力学性能, 提升了在温度循环测试中的可靠性。

5 总结与展望FOWLP 已在消费级和工业级半导体制造领域大 规模应用, 也在高可靠领域得到了初步应用, 是未来 商业竞争的重点方向。学术界和工业界已经针对不同 失效 现 象 建 立 了 FOWLP 的 可 靠 性 物 理 模 型, 对 FOWLP 的失效机理有了较为清晰的认识, 针对性地进 行了工艺改进和可靠性设计优化。但是由于封装结构 复杂度的提升以及多种应力耦合关系过于复杂, 仅靠 失效机理的相关研究已经难以指导工艺和设计的深化 改进。通过机器学习和深度学习将工艺过程、 设计参 数与产品良率、 可靠性参数之间建立数学关系和数学 模型, 可能是指导工艺和设计改进、 进一步提升产品 可靠性的可行之路。

0

0