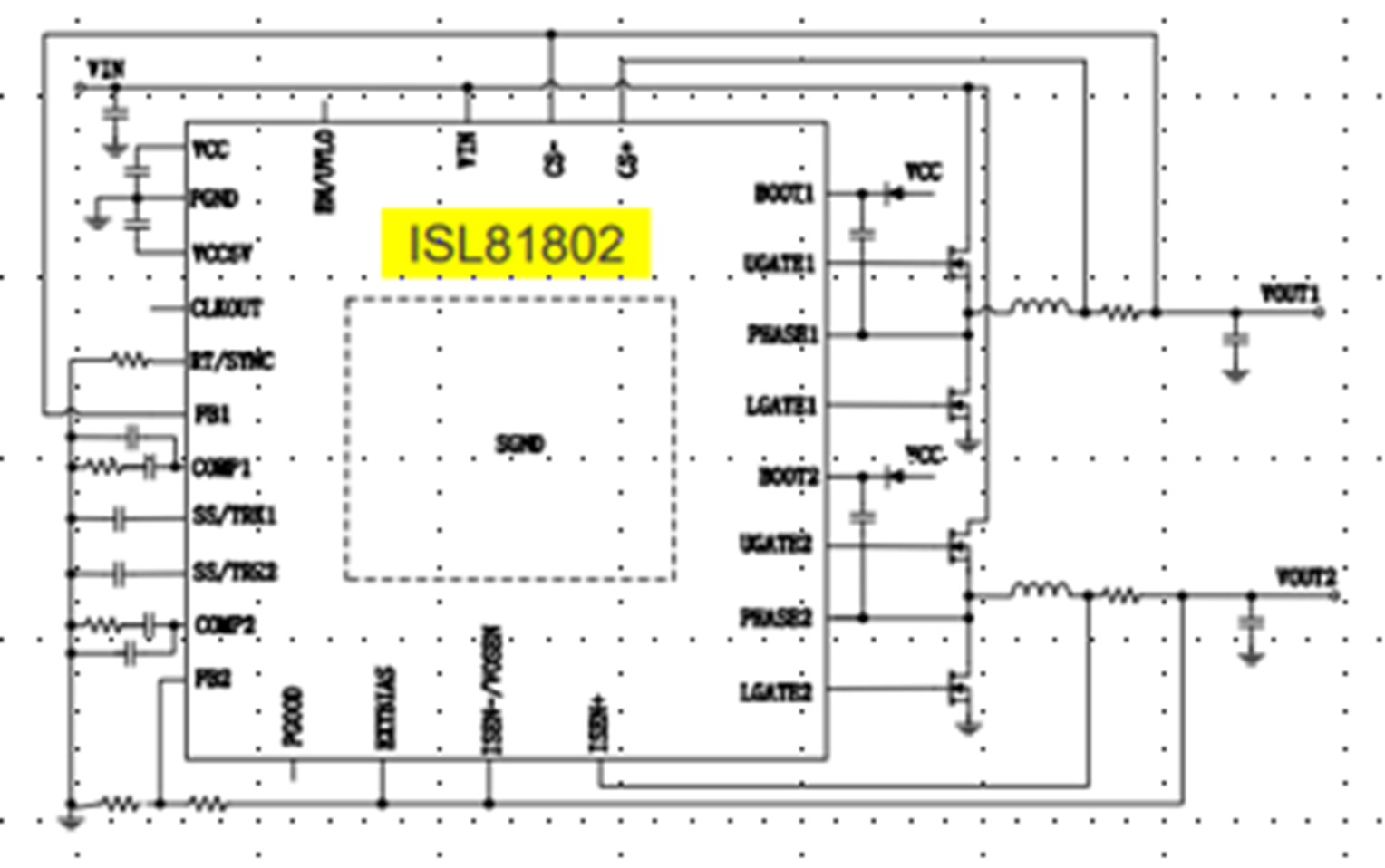

瑞萨 ISL81802 是一款双通道同步降压控制器,可产生两个独立输出或一个具有两个交错相位的输出,适用于工业和通用领域的各种应用。 该控制器具有较宽的输入和输出电压范围,适用于电信、数据中心和计算应用。

瑞萨 ISL81802 的基本性能参数及优势:

- 输入电压:4.5V ~ 80V

- 输出电压:0.8V ~ 60V

- 四个具有自适应穿透保护的 MOSFET 驱动器

- 输出电压恒定,输出电流反馈回路控制

- 低纹波二极管仿真突发模式操作

- 可编程软启动

- 开关频率:100kHz 至 2MHz

- 支持双路电流自动均衡

- 强制 PWM 模式

- 低关断电流:5uA

- 保护 (OVP OCP UPV OTP)

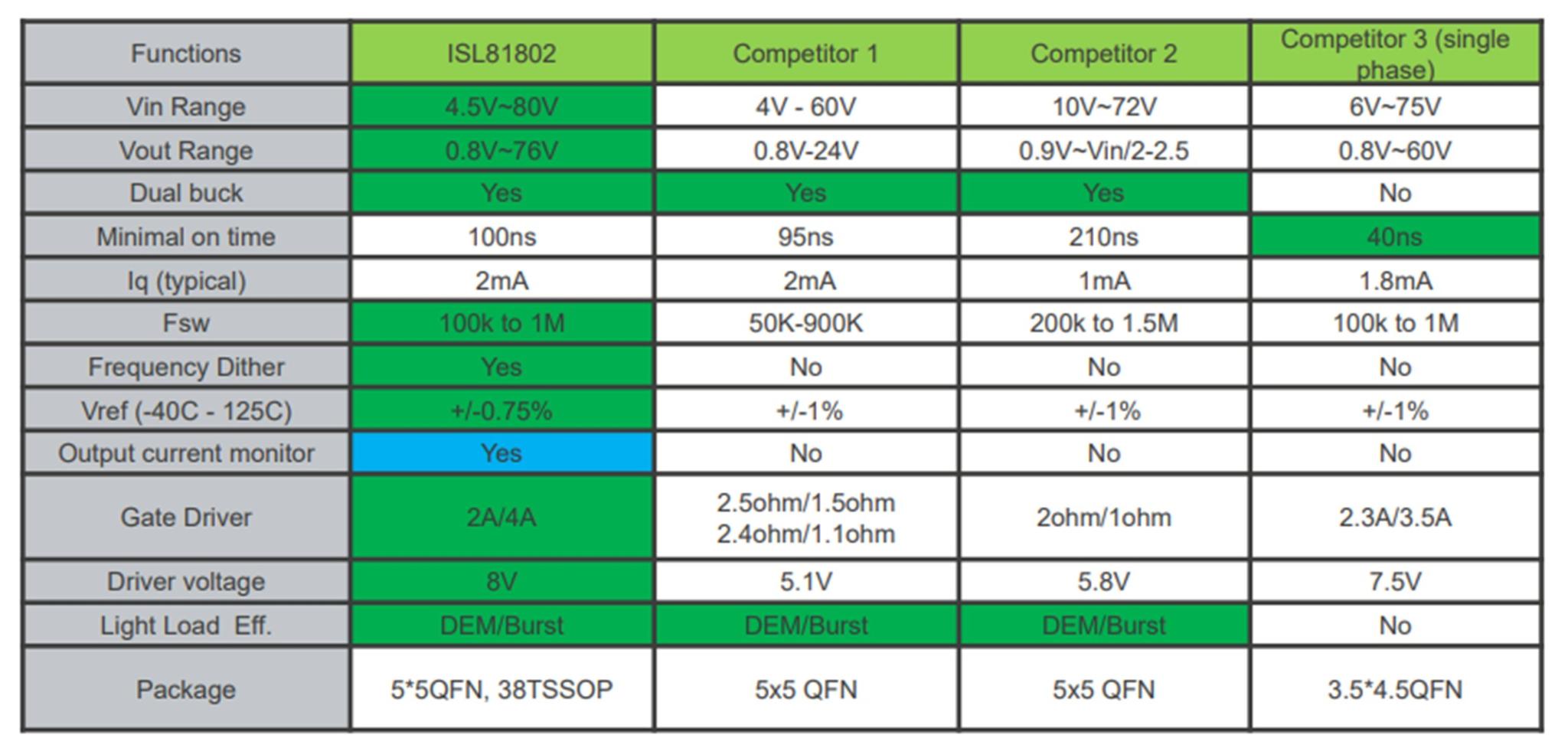

下图为瑞萨 ISL81802 同其他产品的性能对比:

与其他 48V 降压控制器相比,瑞萨 ISL81802 控制器有什么独特之处?

1. 它是一种非常独特的双相位/双输出 buck 控制器,支持高达 80V 输入和高达 76V 输出。它还支持恒压和恒流操作,这意味着它不仅适用于电信和计算,也适用于电池管理和大功率 LED 照明

2. 宽 Vin 量程:4.5V 至 80V

3. 宽电压范围:0.8V 至 76V

4. 具有交错输出的双相或两相 Buck 控制器

5. 集成 CC/CV 控制器+驱动

6. 支持多芯片并联和相位交错

7. 宽开关频率:100Khz 至 1MHz

8. 电流模式与二极管仿真和突发模式在轻负载或强制 PWM 模式

9. 穿保护,OCP,OVP,OTP,UVP

10. 每个输出独立的 EN 和软启动

从中可以看出,它覆盖了很宽的输入输出电压范围,可达 80V,输出可以是两独立输出也可以是两相交错单输出。控制回路可以是恒压或恒流 (两个独立的调节回路用于 CV 和 CC 用于任何输出)。多台 ISL81802 可并联多相配置,支持更高功率。频率可以低至 100kHz 以获得最高效率,或高至 1MHz 以获得最小尺寸。在轻负载时,芯片可以配置为强制 PWM、DEM 或 burst 模式。

瑞萨 ISL81802 参数及引脚设计分析

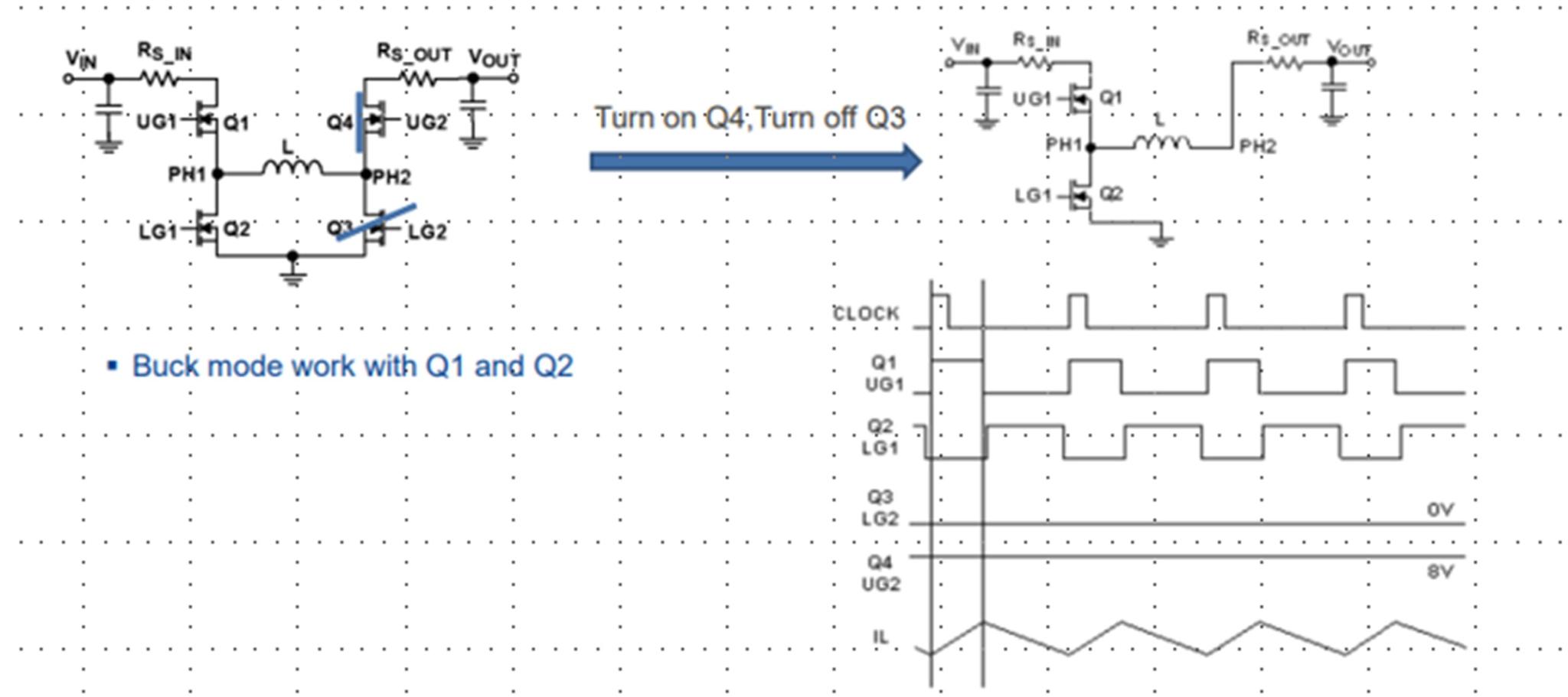

BUCK 模式下开关管的工作状态

如下图所示,在 Q1 开时 Q2 关,Q2 开时 Q1关。Q3 常关 Q4 常开。PWM 占空比可= 输出 / 输入。

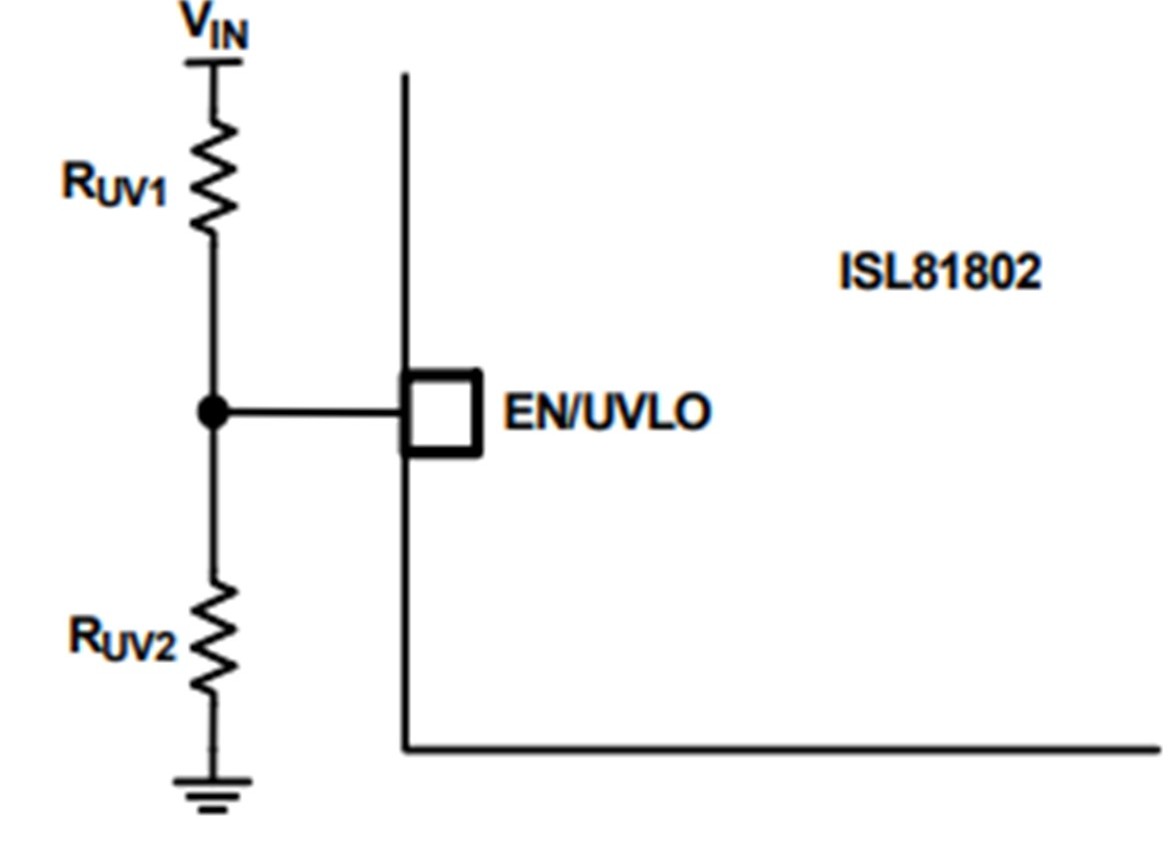

EN/UVLO 引脚作用

EN/UVLO 电压小于 0.9V LDO 及 VOUT disable

EN/UVLO 电压大于 1.3V VDD VCC enable

EN/UVLO 电压大于 1.8V 软起动 SS enable

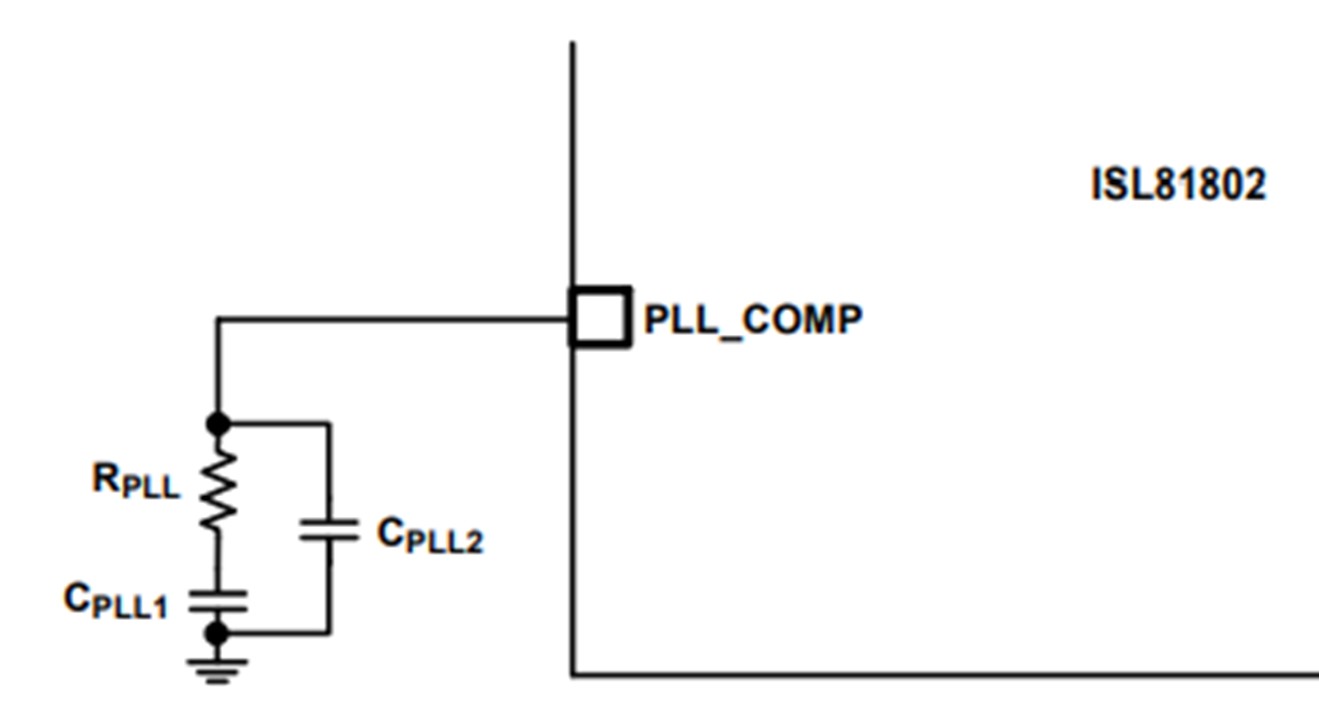

PLL_COMP 引脚作用

需要一个 RPLL、CPLL1 和 CPLL2 的外部补偿网络连接到 PLL_COMP 引脚,确保锁相环稳定运行。瑞萨推荐 RPLL 选择 2.7kΩ,CPLL1 选择 10nF 和 820pF 的 CPLL2。采用推荐的补偿网络保证了锁相环在全时钟下的稳定性。频率范围 100kHz ~ 600kHz。

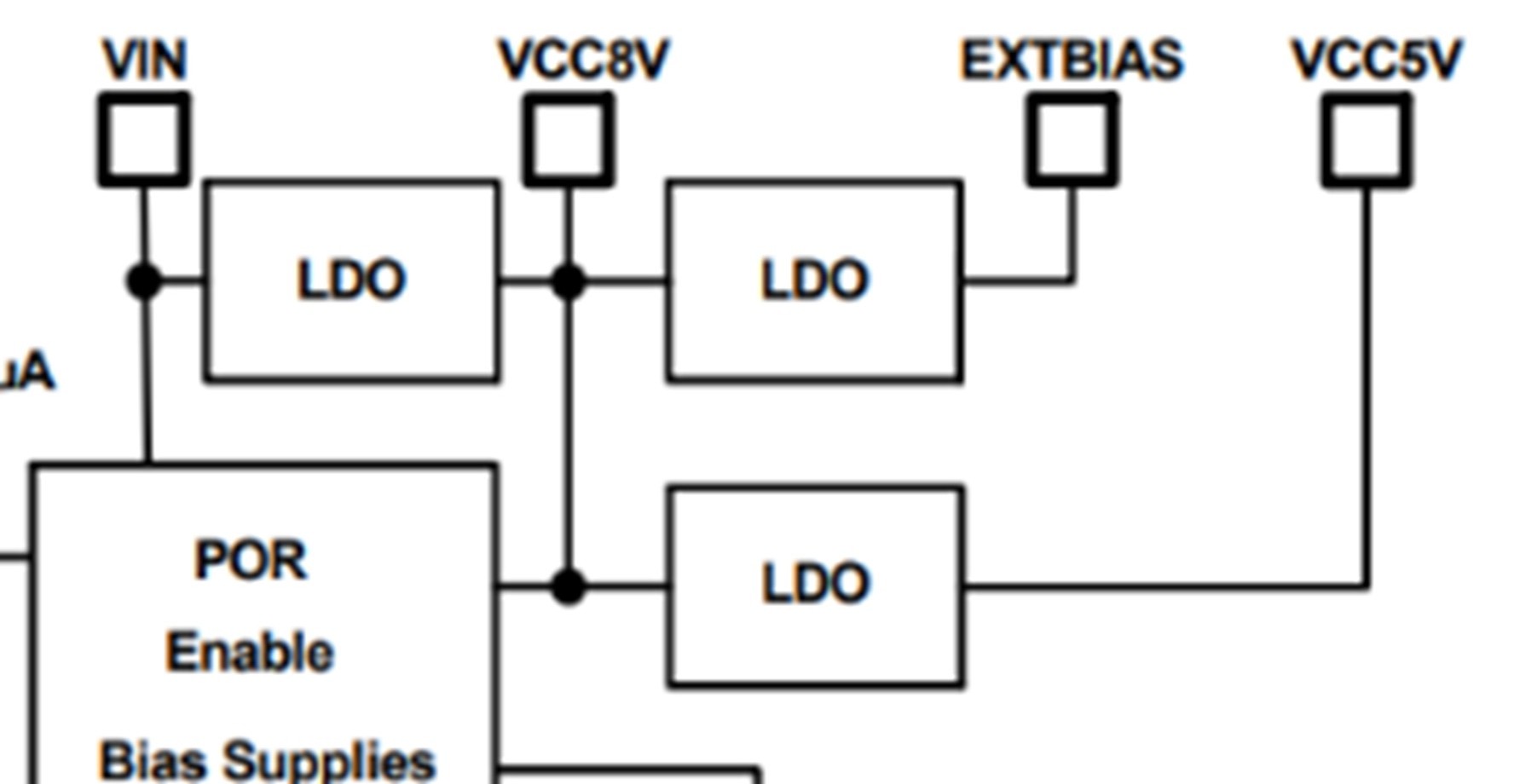

EXTBIAS 引脚作用

- 由 VOUT 及 VIN 供给,内置切换开关。供电 VCC,VDD 8V

- 注意最大值范围,否者需要外部电源供电

- 尽量降低电压值可工作效率及散热问题

-

最小有效值>7.3V

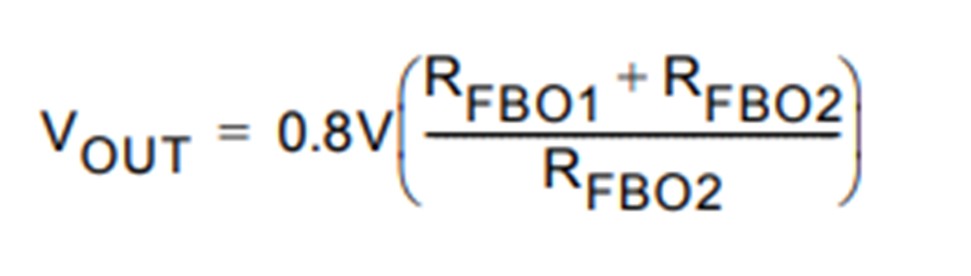

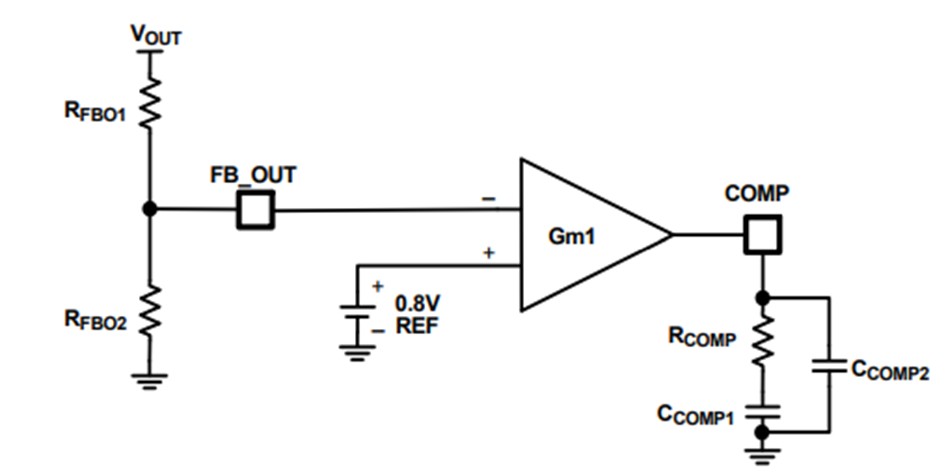

电压环的计算

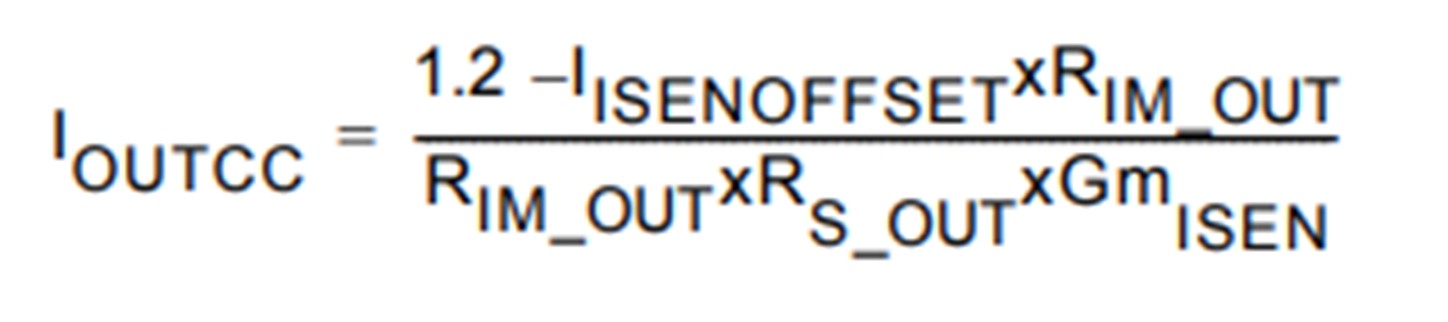

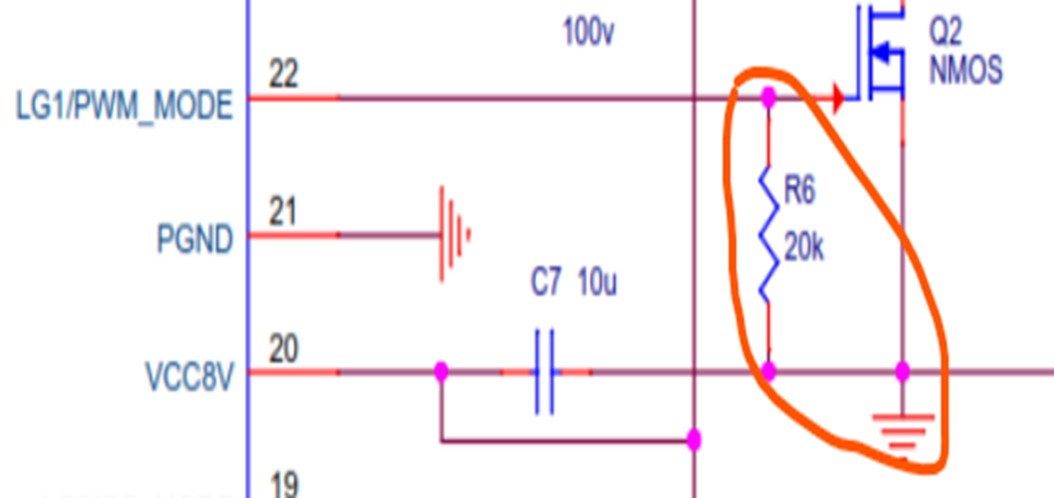

两个电流环的计算

Rs_out 建议 1-5mΩ 之间,有助于提高效率。

降压电路的基本⼯作原理 — CCM 与 DCM

- 降压电路工作在重载情况下,电源处于 PWM 工作模式来获得最佳性能,根据电感是否连续可以分为连续传导模式 CCM 和非连续传导模式 DCM。

- 负载变小时,输出电流平移往下。当负载电流下降到一定程度后,电感电流断续。

轻载高效模式 — DE 模式

设置 DE 模式时,LG1 驱动的降压同步 FET 和 UG2 驱动的 boost 同步 FET 都在运行的模式。电感电流不允许根据零点交叉反转 (断续运行)。

轻载高效模式 — Burst 模式

当负载电流进一步小,小于 VIMONOUTBSTEN 设置的电平典型的 0.85V 时在 IMON_OUT 引脚上,部件进入 Burst 模式。

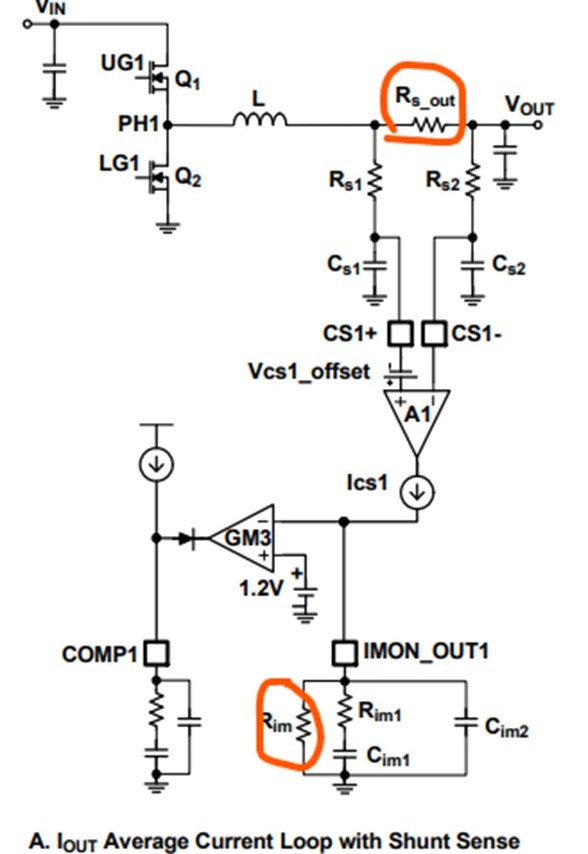

怎样选择轻载模式与 PWM 模式?

- LG1/PWM_MODE pin

- RLG1xIMODELG1 < 0.3V PWM mode

-

RLG1xIMODELG1> 0.34V DE mode

其中 (IMODELG1 = 10uA typical)

怎样选择 CC 模式与 CV 模式?

- 负载电流决定了输出电流

- 在输出电流上升阶段至 CC 模式限流点之前一直处于 CV 模式工作

- 当电流输出上升到最大横流点后,电压会一直掉直至 0.1V 进入 CC 模式

怎样选择 CC 模式与 hicup 模式?

- LG2/OC_MODE pin

- RLG2xIMODELG2 < 0.3V CC mode

-

RLG2xIMODELG2 > 0.3V hicup mode

其中 (IMODELG2 = 10uA typical)

如果需要对硬件的横流点进行改变需要怎样做?

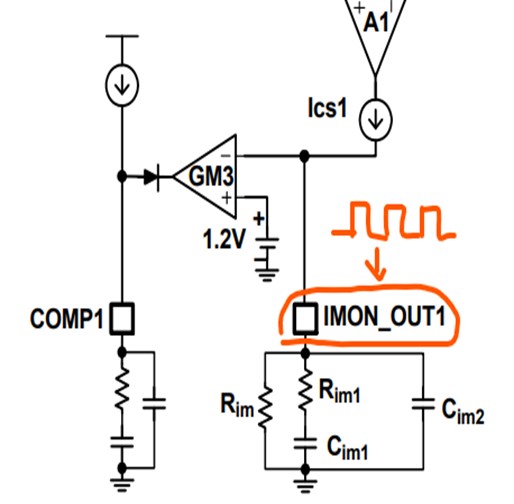

- 通过连接 IMON_OUT 引脚上的 RIM_OUT 电阻,将反馈电流环 ICS 电流信号通过运放在电阻上转换为电压信号。直至到达 1.2V 会进行限流。

- 所以通过在 IMON_OUT 引脚注入 PWM 信号,在 RC 上降低输出电流值,提前进入 CC 模式。

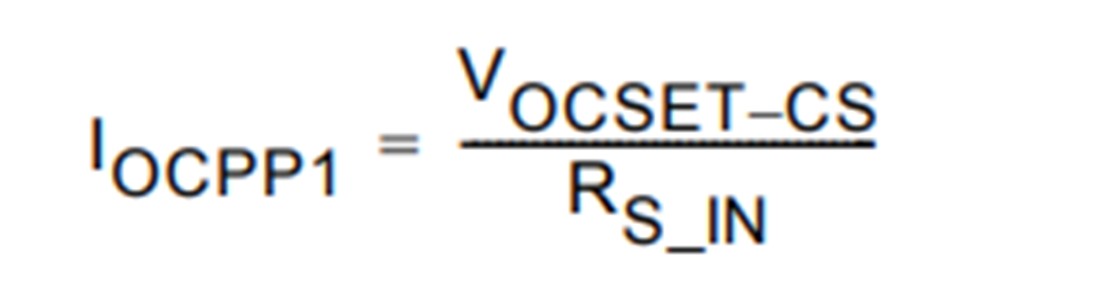

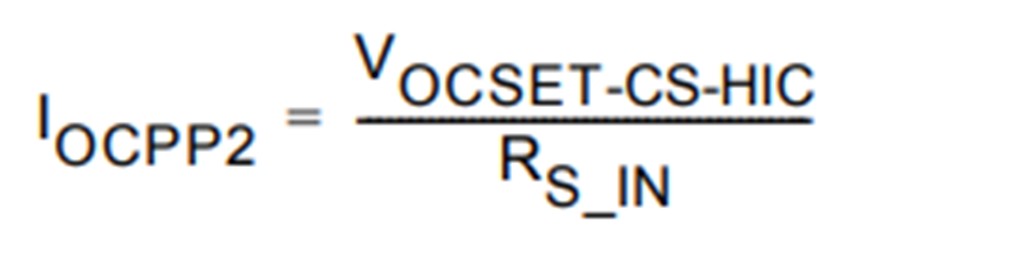

降压电路的相关问题:峰值过流保护

第一级脉冲逐脉冲峰值电流限制,电流由并联电阻 RS_IN 和运放 A1 感知,Q1 在 Buck 模式下关闭。

第二级为了避免在峰值电流模式操作的任何错误跳闸,第一电平脉冲逐脉冲限流电路不能将 PWM 占空比进一步降低到最小时。转换器通过关闭所有四个开关 50ms。

BOOT PIN 工作原理

- BOOT 引脚的引导电容到 PHASE 节点为高侧 MOSFET 驱动器提供电源。

- 在启动时,低侧 MOSFET 首先打开,并迫使相位接地充电 BOOT 电容器到 8V。

- 低侧 MOSFET 关闭后,高侧 MOSFET 被打开,关闭 BOOT 和 UGATE 之间的内部开关。

开关频率的选择

- 增加开关频率可以使降低输出电感和电容大小,可以降低整个电源的体积,同时降低电感和电容的成本。增加开关频率会降低电源效率,辐射能量会加大增加温升。

- 增加开关频率可以降低波纹大小,降低开关频率会加大纹波幅。

- 由 RT 引脚外部电阻到地阻值决定,当 RT/SYNC 引脚连接到外部时钟时,ISL81802 就会同步到外部时钟频率。

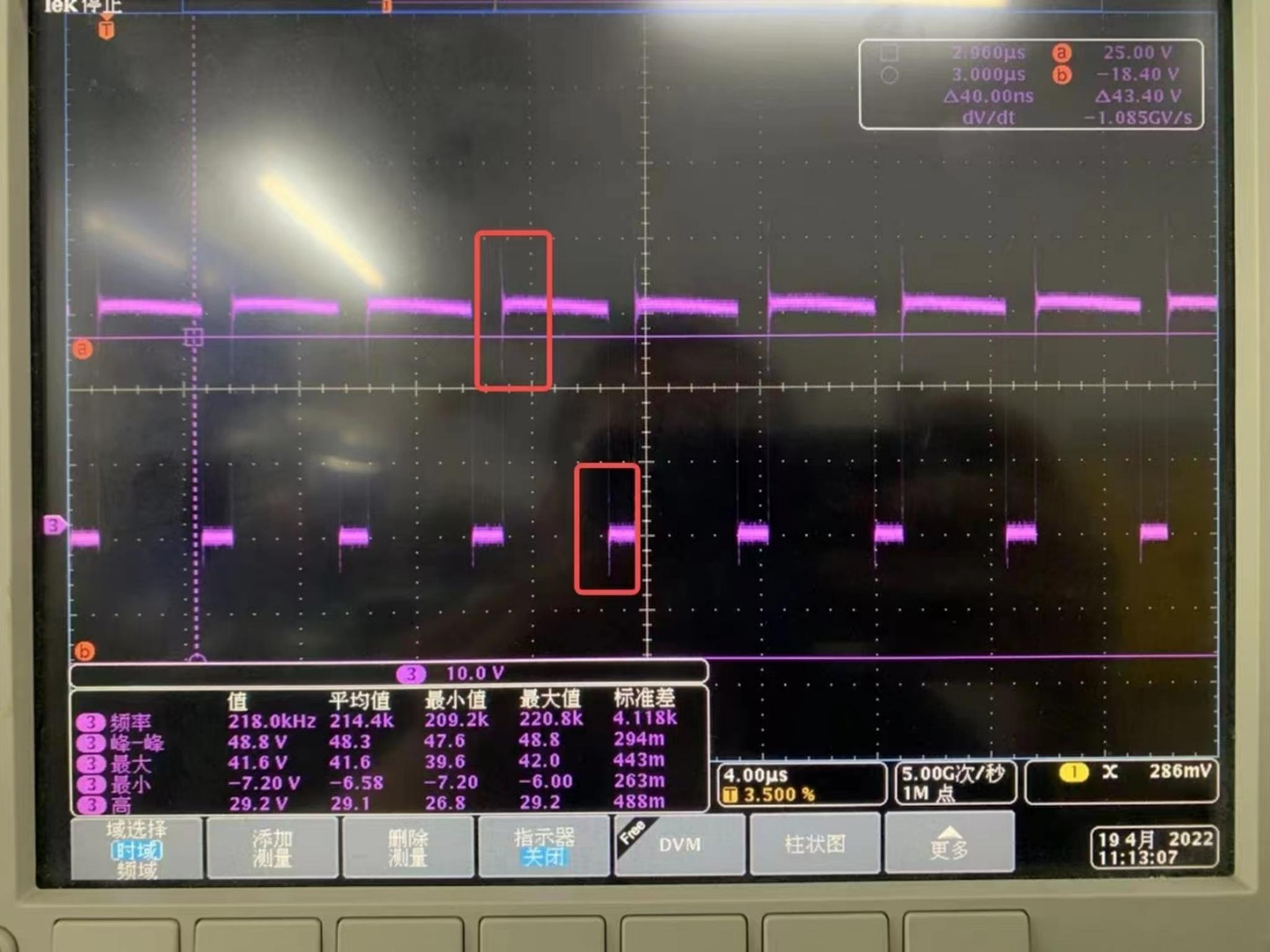

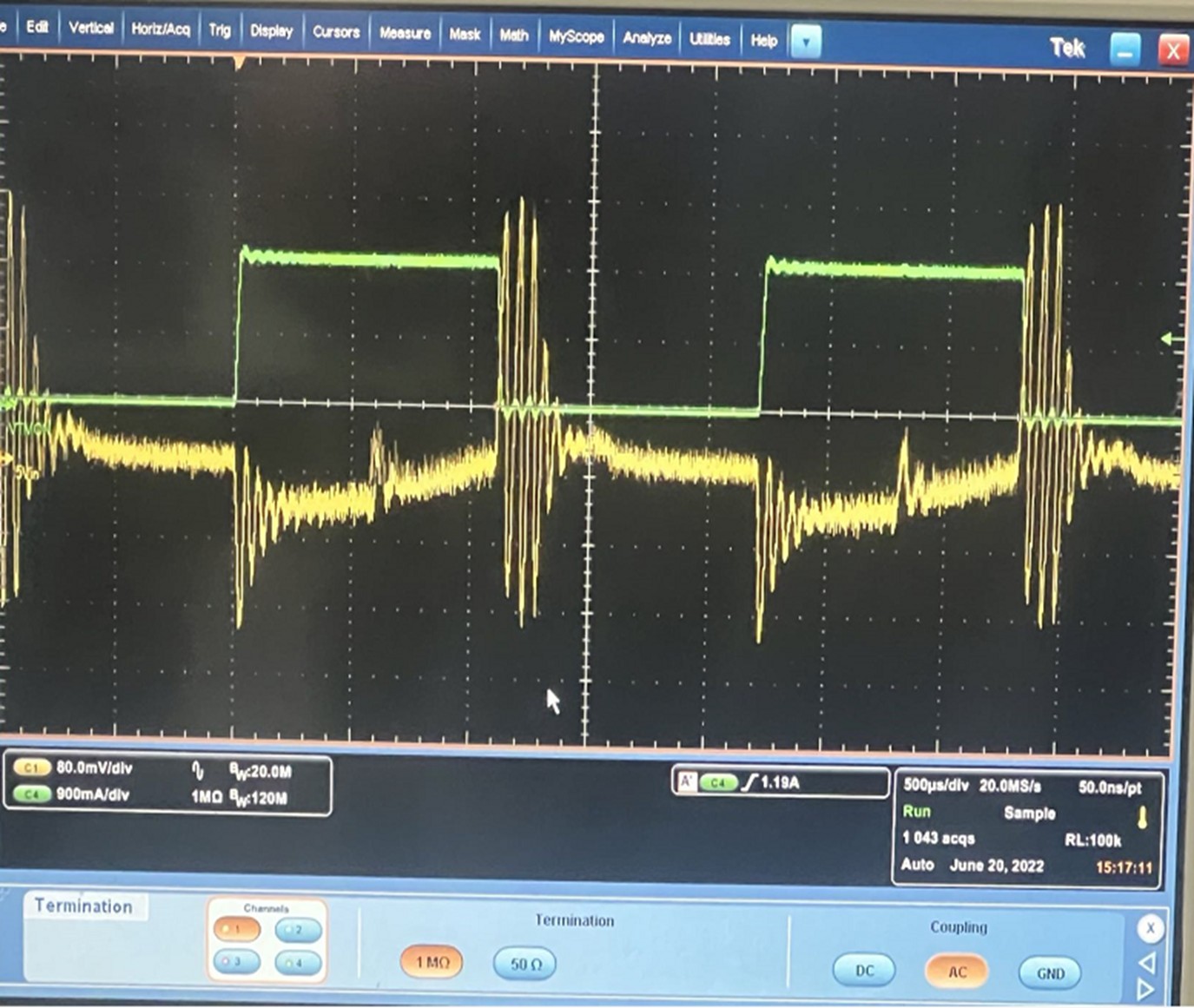

波形分析及优化改进

现象 1:电感前端的 phase 波形,有脉冲尖峰震荡比较大。

结果:在 BOOT 和 phase 间加 RC 吸收电路,调整电阻在 3.3 欧至 10 欧。

现象 2:8V VIN 芯片带载瞬间出现尖峰电流,芯片出现关闭无输出。

原因:这是输出电流在开机瞬间因负载容性值较大会吸收能量有个 20A 10ns 瞬间尖峰电流出现,导致 VIN 跌至工作电压 4.5V 以下再回弹芯片瞬间出现关闭。

结果:

- 输出端外接一个限流开关如 SGM2512,消除压制尖峰增加输入稳定性;

- 使用大容量的稳压电源测试动态效果好,及增加 VIN 电压值。

现象 3:负载测试,在 2A 输出动态测试中,输出电压不稳定。

原因:动态效果差,环路不稳定出现波动异常。

结果:调整环路参数主要是 COM,可使用环路分析仪加以辅助发现穿越频率太高需要优化。

综上,在进行 Layout 设计时,需要注意以下几点:

1. 将输入陶瓷电容尽可能靠近 IC VIN 引脚和 PGND 引脚。保持电源回路 (输入陶瓷电容器,IC VIN 和 PGND 引脚) 尽可能小,以减少相位电压环诱导的痕迹寄生在导通,以及更好的电磁干扰性能。

2. 将 0.1uF 陶瓷电容放置尽可能靠近 VIN 和 PGND 引脚的 IC 上。如果使用铝电解电容器,放置它尽可能接近 IC VIN 引脚。

3. 保持相节点铜面积小,以减少寄生电容,但大到足以处理负载电流。

4. 电源地应接在模拟地层。

5. 反馈电阻靠近 FB 和 GND 引脚,远离相节点。

6. Buck 上管低频打嗝没法一直维持能量,refresh 波形,正常的电流采样、UG1 和 phase1 差分走线。

7. 电流采样环 CS 差分总线。

8. Phase 与 UG 差分走线。

9. 上下管驱动线不能走一起,开关时大电流过会串扰担心直通。MOS Qg 值不能太大影响开关损耗 1500pf 左右可以。

10. 输入的钽电容一定要靠近输入 mos 减小环路干扰减小尖峰应力,比输出电容更重要。

0

0