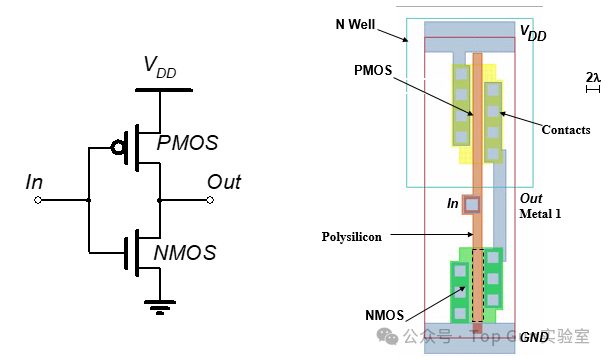

q反相器是所有数字设计的核心

一旦清楚了反相器的工作原理和性质,设计其它逻辑门和复杂逻辑(加法器、乘法器和微处理器等)就大大简化了。典型的CMOS反相器电路

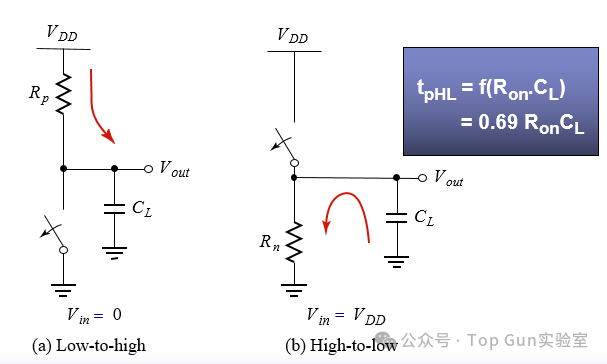

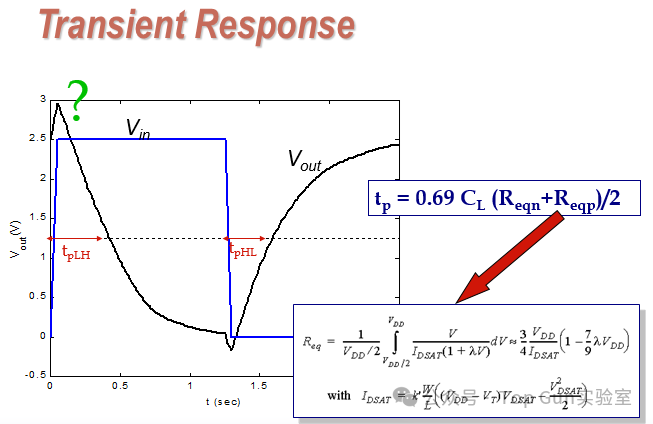

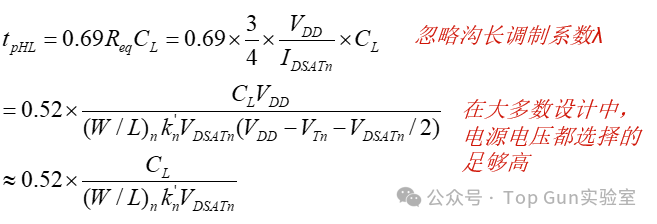

CMOS反相器传输延时

减小延时的方法

减小延时的方法

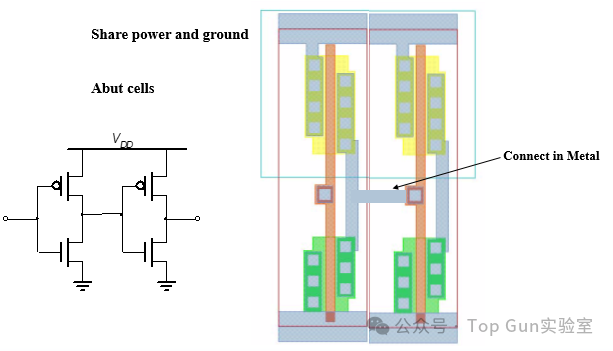

1)减小CL:精细的版图设计有助于减小扩散电容和互连线电容,优秀的设计实践要求漏扩散区的面积越小越好;

2)增加晶体管的W/L:这是设计者手中最有力和最有效的性能优化工具。带来的影响:增加晶体管的尺寸也增加扩散电容3)提高电源电压带来的影响:

a)能量损耗

b)增加电源电压超过一定程度后改善就会非常有限,因而应当避免

c)从可靠性方面考虑,氧化层击穿和热载流子效应等问题迫使在深亚微米工艺中对电源电压要规定严格的上限

注:文中公式推导详细过程可参阅数字集成电路设计相关内容

0

0