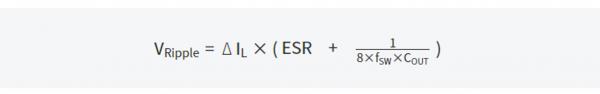

开关稳压器纹波电压公式

在数字电路处理高速信号时,抖动的要求规格也变得严格,因此,需要减小影响抖动特性的脉动电压。这次,为了将影响抖动特性的开关稳压器的脉动控制在最小,我们来看看应该怎么做。

VRipple: 纹波电压

ΔIL:电感器的纹波电流

ESR:输出电容器的ESR

fSW:开关频率

COUT:输出电容器的容量

开关调节器的纹波电压可以用上述公式来表示。

从这个公式可以看出,电感器的纹波电流(ΔIL)越大,纹波越大。

感应器纹波电流定义为负载所需电流的40%。

因此,FPGA等的数字电路所要求的电流值增加的话,脉动就会变大。

因此,在低电压、大电流化正在加速的现状下,由于不能减小电感器的脉动电流,所以需要在上述公式的其它项目中减小脉动电压。

要降低开关稳压器的纹波电压

除了上述公式中感应器的纹波电流之外,还有三个项目。

1. 输出电容器的ESR (ESR)

2. 输出电容器的容量 (Cout)

3. 开关频率 (fsw)

通过调整这3个项目,可以减小脉动电压。

1. 关于输出电容器的ESR,如式1的"纹波电流xESR"所示,与ESR成比例增大,因此通过使用ESR小的陶瓷电容器,可以减小ESR。

2. 关于输出电容器的容量,因为在式1的分母中,所以通过增大输出电容器的容量,脉动会变小。要增加容量,可以通过多搭载陶瓷电容器来实现。但是,由于板面积变大,成本增加,所以希望将搭载数控制在最小限度。

3 . 关于开关频率,因为也是在式1的分母中,所以通过提高开关频率,脉动会变小。但是,一般来说,提高开关频率的话,开关损失会变大,效率会降低。因此,需要一边确认效率是否有问题,一边研究提高频率。

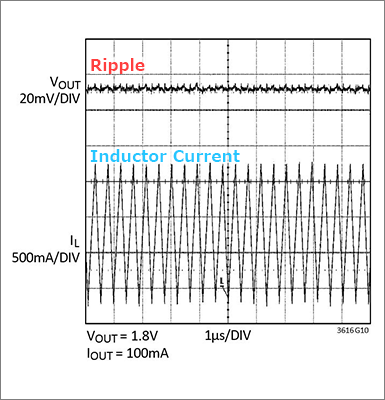

图1是同步整流型DC/DC转换器LTC3616的纹波电压和电感器电流的波形,纹波非常小,只有几mV。

图1:纹波和电感器电流

开关频率和效率

提高开关频率的话,开关损失变大,效率降低。

几年前,2MHz是最高的开关频率,最新的设备已经推出了4~5MHz产品。

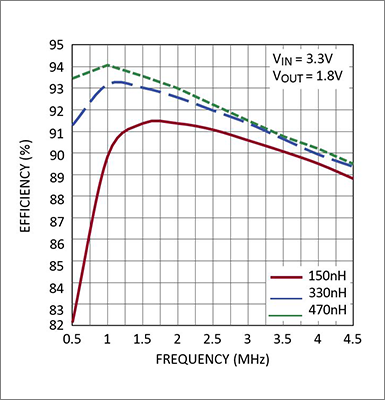

图2是同步整流型DC/DC转换器LTC3616的开关频率 ― 效率特性曲线。

当开关频率为1~2MHz时,效率将达到峰值,并逐渐下降到4MHz。但是,在4MHz时也达到了约90%,所以效率没有问题。

图2:开关频率 ― 效率特性

开关频率可调节到4MHz的单片同步整流降压调节器的列表如下。

通过使用这款产品,可以减小波纹,抑制数字电路的抖动成分,进行电路设计。

| Part # | Product Features | Input Voltage Range |

|---|---|---|

| 1.25A, 单片同步整流降压稳压器 | 2.5~5.5V | |

| 可由1个电阻配置的1.5A同步整流降压稳压器 | 4~15V | |

| 1.5A, 单片同步整流降压稳压器 | 4~15V | |

| 2.5A, 单片同步整流降压稳压器 | 3.6~15V | |

| 3A, 单片同步整流降压稳压器 | 2.25~5.5V | |

| ±5A, 单片同步整流降压稳压器 | 4~15V | |

| 5A, 单片同步整流降压稳压器 | 4~20V | |

| 用于DDR终端的±6A单片同步整流降压稳压器 | 2.25~5.5V | |

| 6A, 单片同步整流降压稳压器 | 2.25~5.5V | |

| 8A, 单片同步整流降压稳压器 | 2.25~5.5V |

注意事项!即使使用好的产品波纹也很大

通过使用开关频率为4MHz的产品,可以得到如图1所示的波纹电压那样小且漂亮的电压,但是,在开关调节器的设计方法的报道的后半部分中有记载,如果基板的PCB设计错了,就得不到希望的波纹波形。

一旦由于电路板的图案设计而在波纹上产生了较大的开关噪声,由于很多情况下不能通过追加电容器等来解决,所以需要注意。请一定参考厂家推荐的图案进行设计。

将布局的影响降到最低

由基板上的配线引线产生的配线图案的电感成分和IC的引线和焊线产生的电感成分引起的噪声会对脉动电压产生影响。

将该电感分量最小化的解决方案是Analog Devices公司的μModule。

支持4MHz开关频率的产品线如下。推荐给不想花费时间进行布局设计的人,以及希望尽可能抑制波纹来组装系统的人。

0

0