要点1:大电流的电源电压远端反馈差分走线

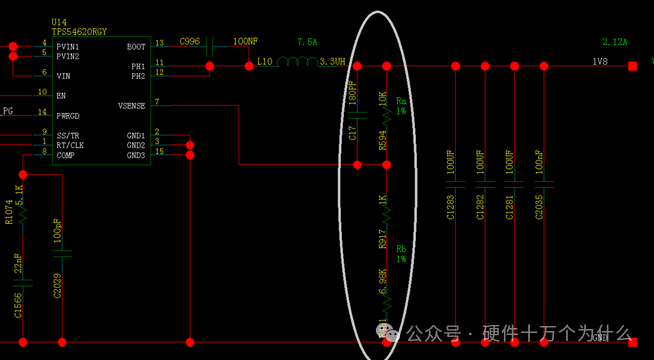

电压检测分反馈检测,反馈检测。一般小电流电源采用近端反馈,如下电路为检测电路。分压电阻及反馈线靠近电源输出(输出电容)处放置,并单端信号反馈即可。

一般大电流电源采用近端反馈,如下电路为检测电路。(如果有分压电阻,分压电阻靠近控制器放置)这对差分线的主要作用是为了抑制共模干扰,所以对于差分对的线长差没有要求。

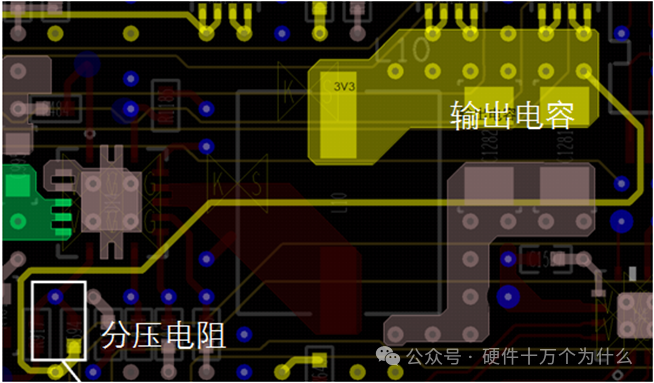

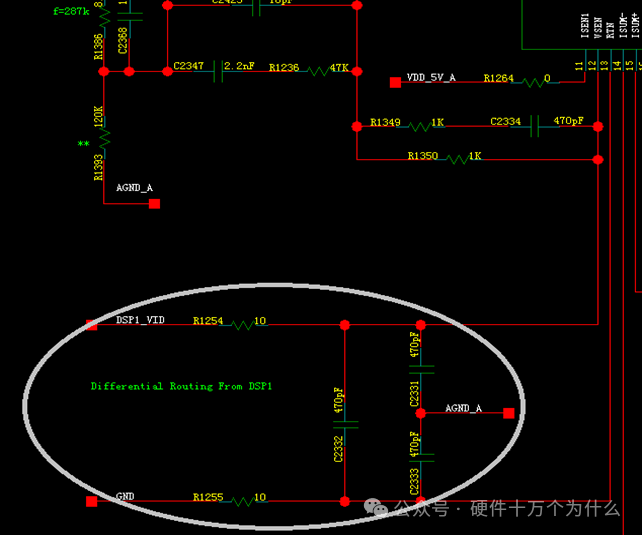

要点2:电源电流采样差分走线

电源电流采样为微弱信号,需要差分走线,并且远离干扰源。

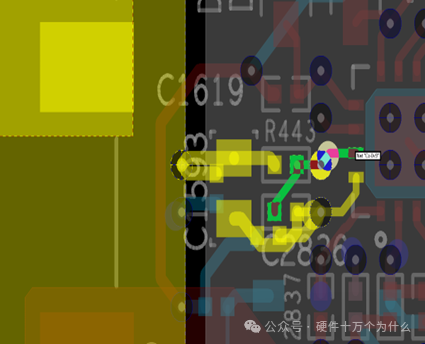

错误走线示范:

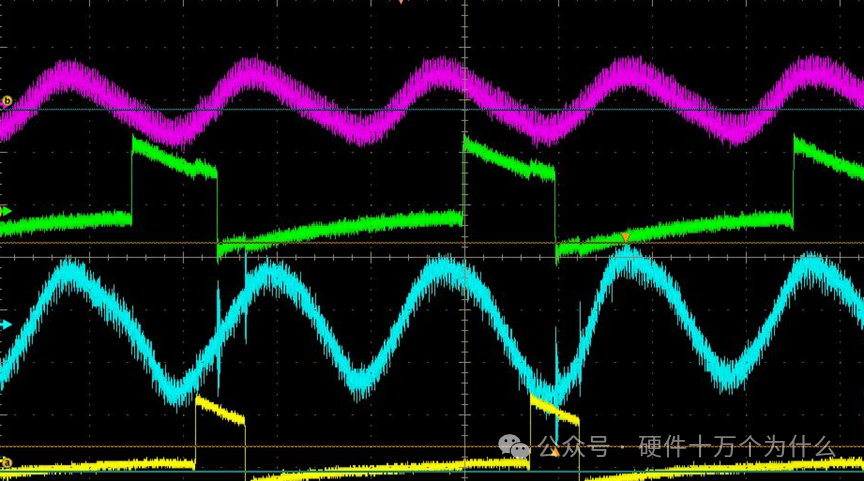

0.9V主要是给单板上的两个FPGA提供core电源,电流评估达到17.1A,电流比较大,因此怀疑是否因为过流导致的0.9V电压跌落,因此测试0.9V电流,测试结果显示的确是电流过流了(实际测试不到12A),但是没有达到原理图中设置的过流点(25A)。

正确的做法:从电感两端向中间引线,走成差分线,换算电路尽量都靠近控制器放置。

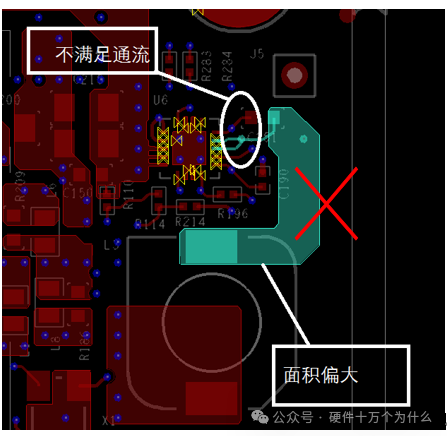

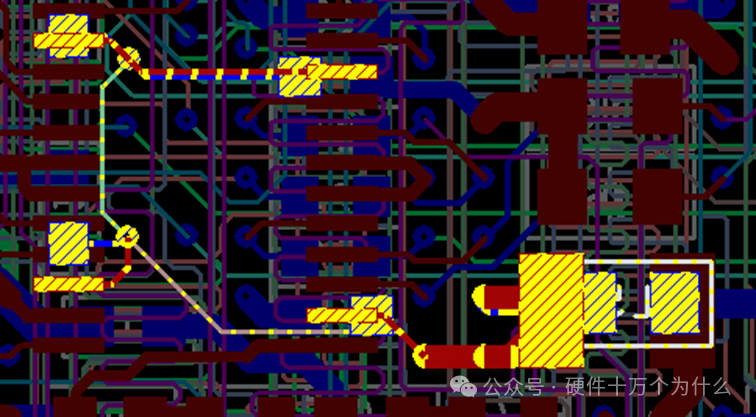

要点3:SW平面(Phase平面)在保证通流的前提下面积尽量小

Phase平面,即:下管的D极与下管的S极连接网络,在0V与12V不断跳变,对外辐射极大,电流也大。按照输出电流计算通流,保证通流,同时在满足通流的前提下保证面积较小。

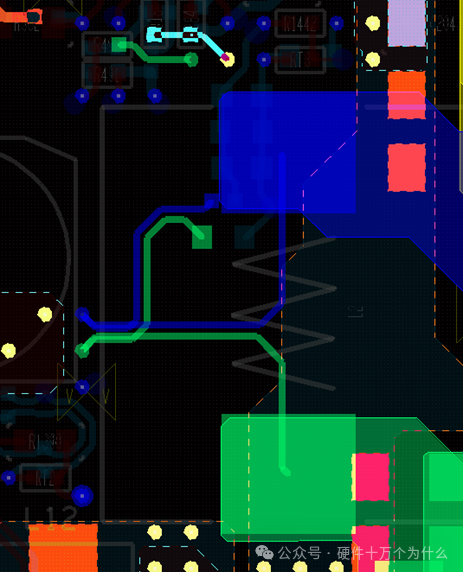

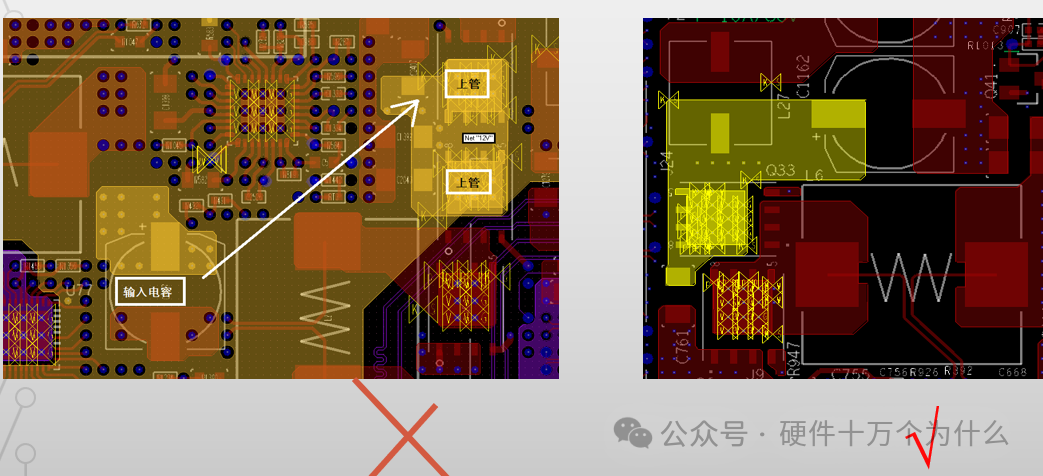

错误布线图如下:

干扰其他管脚和网络,EN最小只有1.14V,导致电源误关断。

出线后保证通流能力的同时尽量削减Phase平面面积,并远离易受干扰信号。如下图所示。

要点4:电源输出通流能力需要检查

重点检查过孔和线宽:通流与线宽关系有工具可以计算的,过孔的通流能力互连技术有做过实验,实验的结果是一个10MIL过孔可通2.7A电流,在设计过程中,考虑到电源的压降和可靠性等因素,我们通常会按照一个过孔过1-1.5A设计。

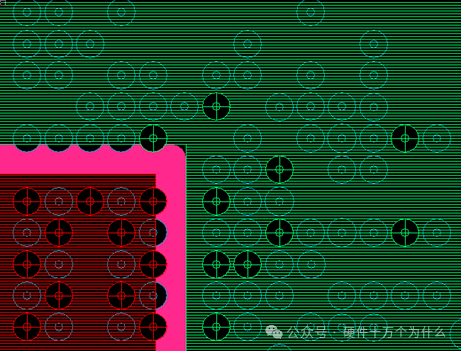

同时,需要关注,正负片铜是否有打断(BGA、过孔密集、以及过孔密集处是否有高速总线)。原本完整的电源平面会被密集过孔打的不满足通流要求。

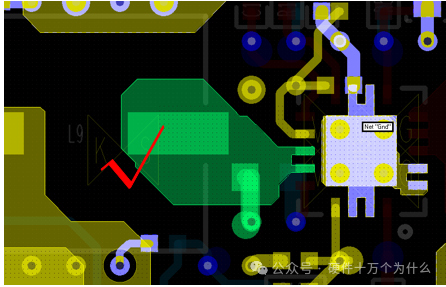

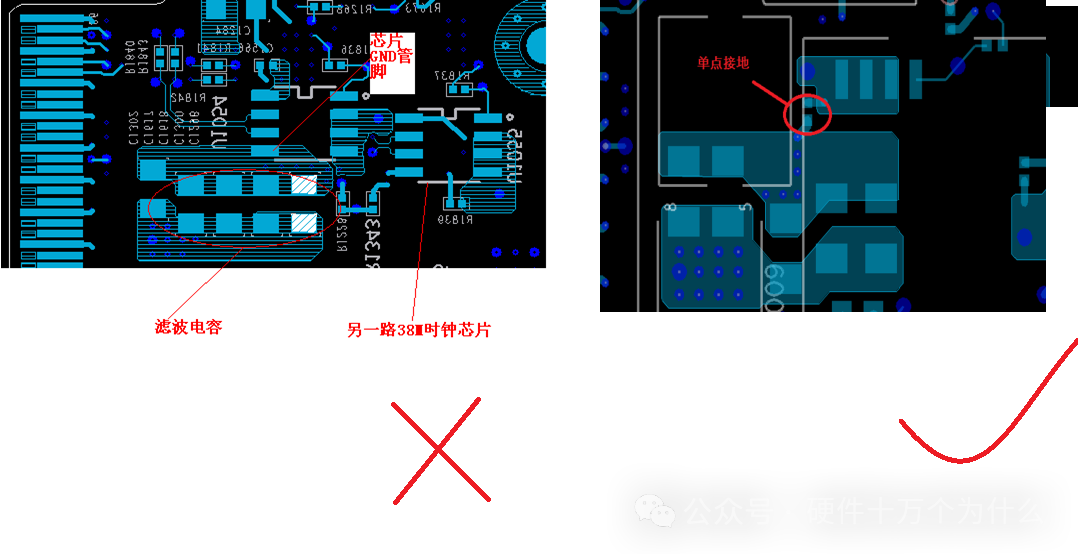

要点5:芯片的GND不能与电源滤波电容的GND共地(尤其需要远离输入电源的滤波电容)。

发现芯片的GND管脚上有干扰,随后确认电源滤波电容的干扰通过共地的GND管脚影响到芯片的差分输入。

在38.88M时钟线路收发器的差分输入端测试,发现输入的差分信号有干扰,后来查看PCB,发现芯片的GND管脚在bottom面与4个12V电源的滤波电容共地,于是测试芯片的GND管脚,发现GND管脚上也存在干扰,当撬起芯片的GND管脚接到附近另一个电容的地上时,干扰明显减小。初步确定电源滤波电容上的噪声通过共地平面,直接将噪声从芯片GND管脚串入,从而导致芯片的输入差分信号受到干扰。由于芯片的GND受到干扰,直接抬高了GND的电平,导致差分输入受到干扰,单端输出暂时还没有发现异常。PCB走线参见图

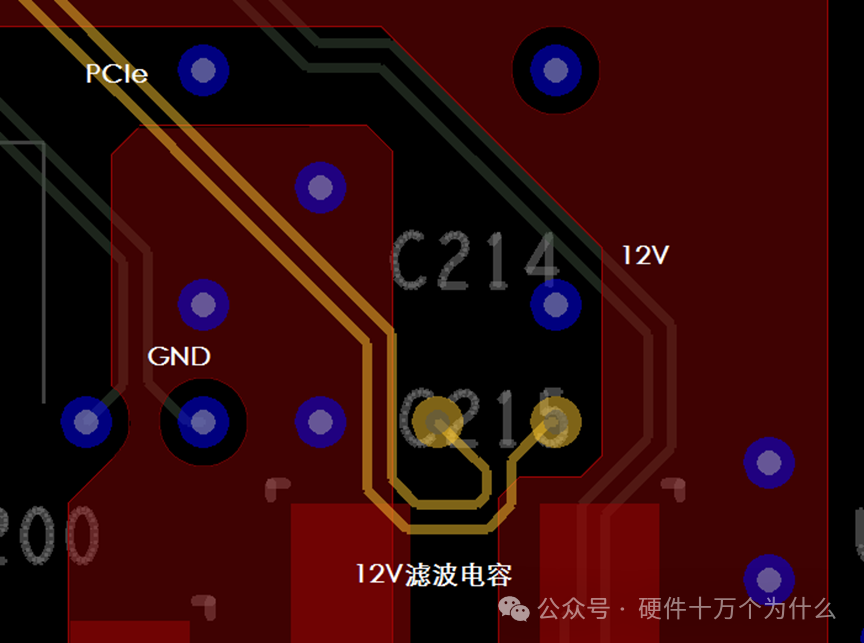

要点6:高速信号,敏感信号远离输入电源及输入GND。

12V的PCIe 11 lane 离12V电源平面过近,耦合到噪声导致掉为1X或者os下掉盘。

错误示范如下:

要点7:大电流的DCDC输入建议电感隔离

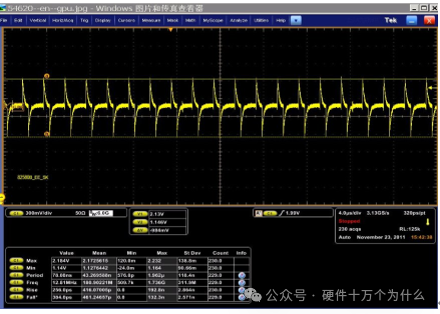

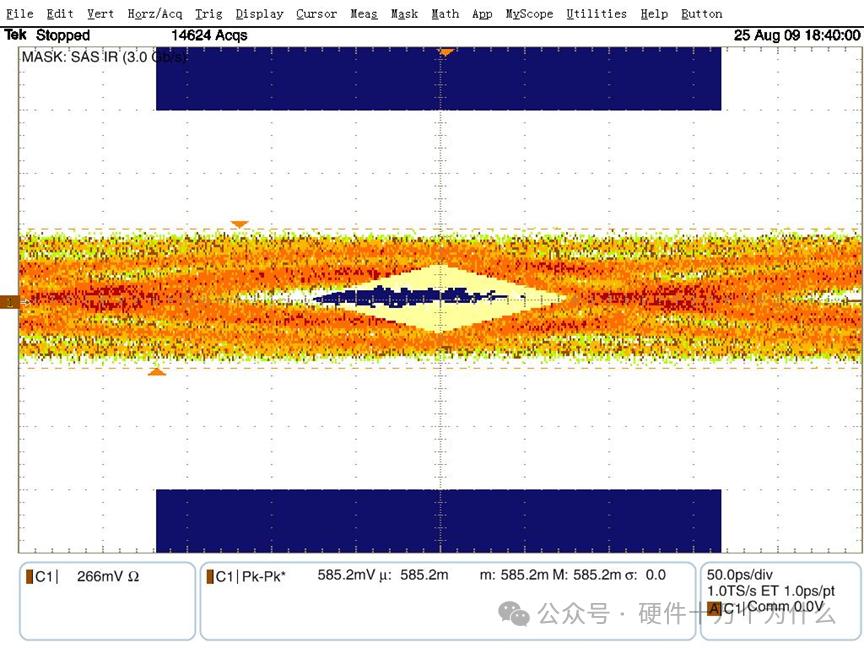

眼图很差,眼睛完全没睁开

根因分析:

12V上的开关噪声耦合到了1V1平面。VID电源的MOS管的开关噪声影响了前级的输入12V。而1.1V的参考地为12V,12V上的干扰耦合到了1.1V平面。

解决措施:

采用L型滤波,在VID输入的12V上串上1uH的电感,并并上一个470u电容。测量1.1V平面上的VID的噪声被完全滤除。现象也随之消除。

要点8:输入电容靠近上MOSFET放置

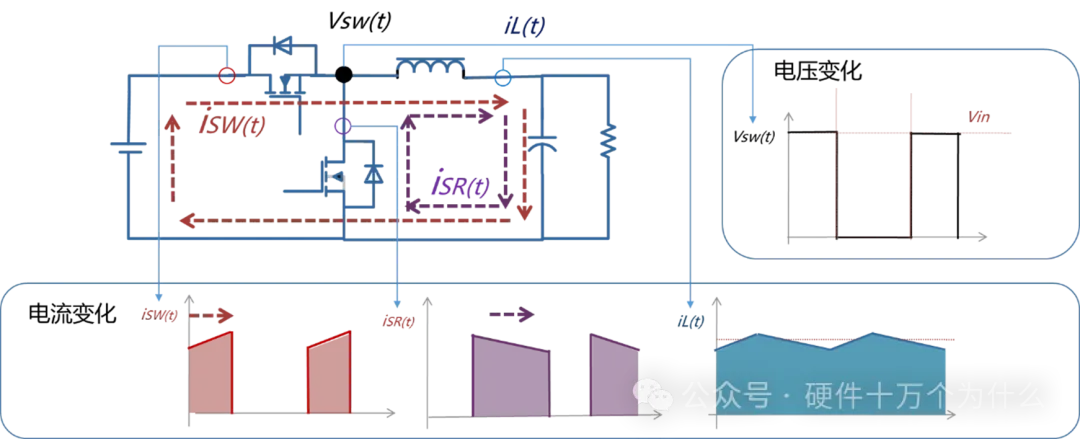

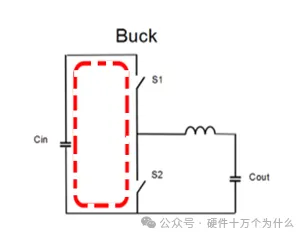

在开关电源工作过程中,上管打开的时候是下图中红色的电流环路;下管打开的时间内是下图中紫色的电流环路。但是两个时段叠加在一起,通过上管和下管的部分是一个大电流跳变的电流环路,而通过电感的电流跳变幅度并不大(蓝色波形)。

所以我们把上管下管和输入电容这个环路作为一个干扰环。

所以我们要把输入电容靠近上管和下管放置,尽可能减小这个环的面积。

要点9:GATE,BOOT电容走线尽量短粗

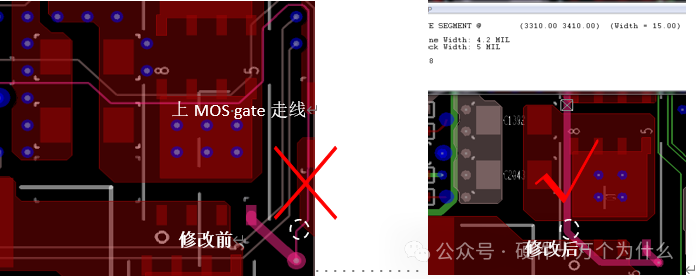

MOS管的栅极驱动由于开关电压差较大,瞬间电流很大,所以在布线时要尽量走短而粗的线,减小走线沿路的干扰和走线的电感效应,保证mos管可靠开闭,一般15mil或以上,如果空间不够的话,互连也会走10mil的大小。

下图左边的图中粉红色高亮的线为上MOS管的驱动走线,该走线在内层的布线宽度只有4.2mil,而且线长也没有做到最短。开关电源的MOS管在板上用到的数量不算多,所以要挨个排查驱动线的走线,特别是换层后走线宽度是否仍满足宽度要求。

要点10:二极管、电感、磁珠、RC滤波的电阻前后的走线线宽需要保持一致;

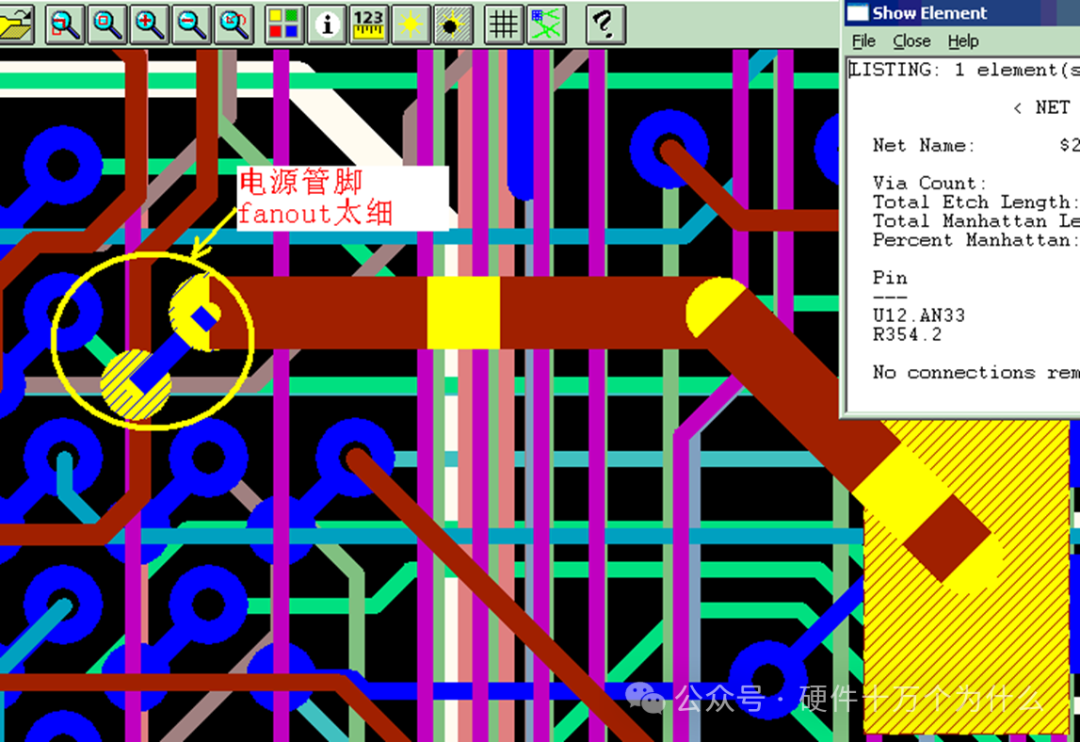

如下图中,磁珠隔离后,给器件的4个电源管脚供电,走线太细,宽度只有5mil;

如下图圈中,core电源线满足要求,但fanout太细;

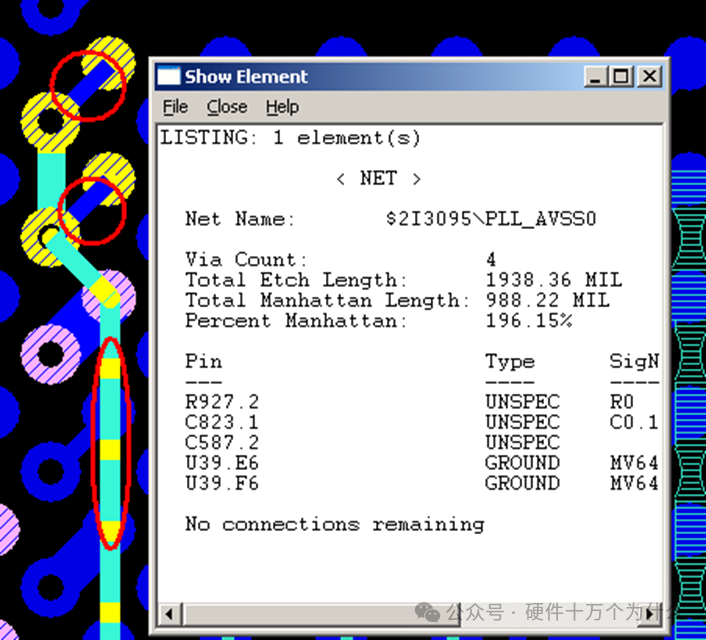

如下图圈中,锁相环地经过磁珠滤波后,走线太长太细,fanout太细;

0

0