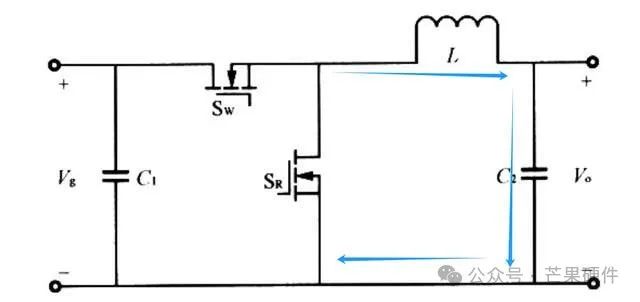

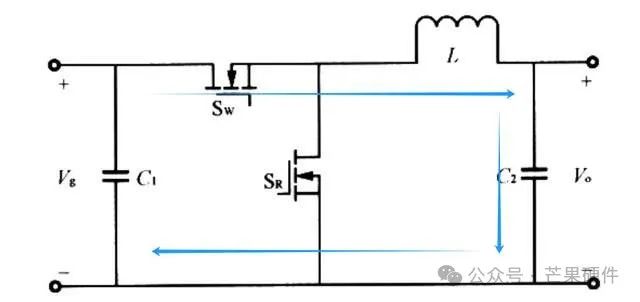

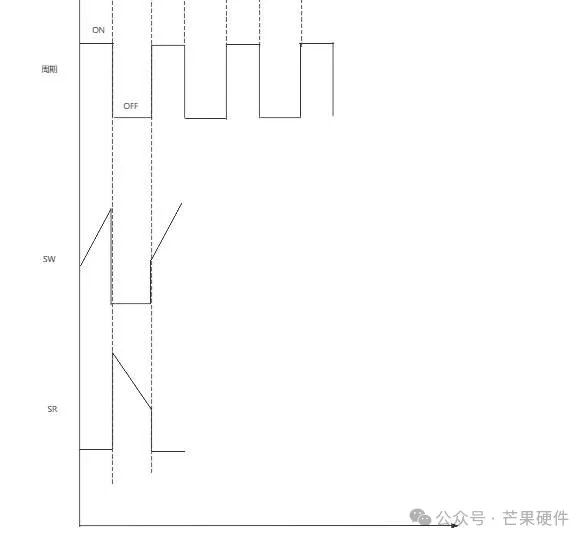

关于buck电路的Layout设计注意事项,我们先上图,看看Toff时的电流回路,Ton时的电流回路,以及Toff, Ton时的MOS管电流图形。

Toff时电流回路

Ton时电流回路

SW&SR电流

我们知道信号一般是当di/dt或者dv/dt发生剧烈变化的时候,才会产生一些严重的信号问题,即所谓的EMI问题。

SW点的布局:因此我们不难观察SW&SR电流波形图,是开关管开关的那一瞬间容易产生EMI问题。因此我们在实际布局的时候应该尽可能减小功率回路的面积,降低噪声的发射。并且由于SW这一点是噪声源,在保证电流尽量小的面积的同时,要远离敏感的易受干扰的位置。

FB/REF点的布局:尽量使反馈迹线远离电感器和噪声电源迹线。还应让反馈迹线尽可能直且稍宽一些。如果可能,则在与电感器相对的 PCB 一侧铺设反馈走线, 并使用接地平面将两者分开。

输入电容:输入电容靠近芯片放置,去耦电容距离最好不要超过40mil。

对于铺铜:对于一些容易发热的器件例如MOS管,二极管我们需要在WCA提前考虑好环温,结温这些信息。这对于我们的散热设计很关键。如果计算有较热的风险,我们也需要考虑来铺铜来散热。另外SW和Vin以及Vout处的铺铜也应考虑限流的问题。

降低频率:对于部分EMC问题,在不影响功能的前提下,我们可以考虑降低开关频率来解决问题。

0

0