本文介绍反激式转换器 RCD 缓冲电路的设计指南。当 MOSFET 关断时,由于主变压器的漏电感 (Llk) 与 MOSFET 的输出电容 (COSS) 之间存在谐振,漏极引脚 上会出现高压尖峰。

漏极引脚上的过高电压可能导致雪崩击穿,并最终损坏 MOSFET。因此,必须添加一个额外的电路,实现电压箝位。

一个最简单的拓扑是反激式转换器。该拓扑源自一个升 降压转换器,将滤波电感替换为耦合电感,如带有气隙 的磁芯变压器。当主开关导通时,能量以磁通形式存储 在变压器中,并在主开关关断时传输至输出。

由于变压器需要在主开关导通期间存储能量,磁芯应该开有气 隙。因为反激式转换器所需元件很少,因此该拓扑非常 合适中低功率应用,如电池充电器、适配器 和 DVD 播 放器。

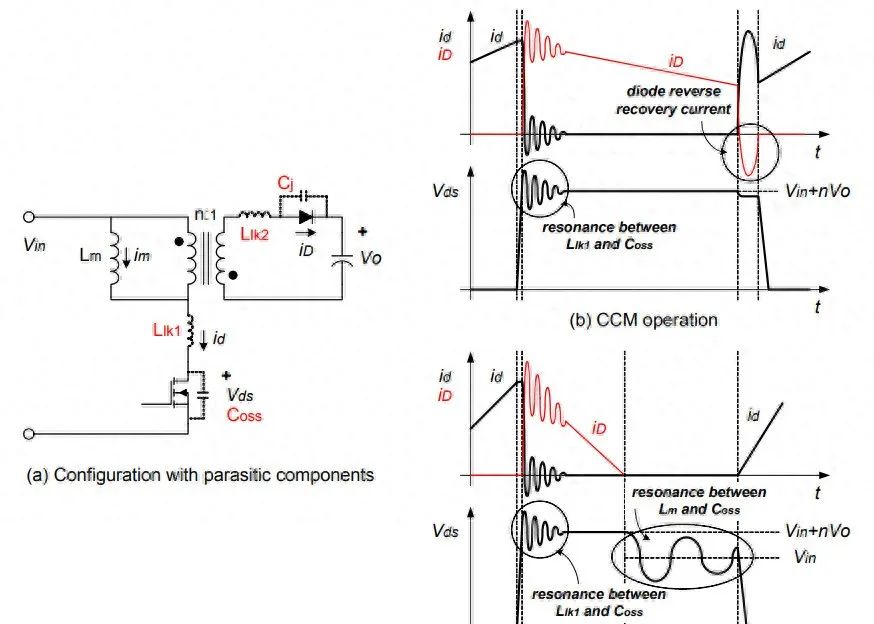

图 1 显示在连续导通模式 (CCM) 和不连续导通模式 (DCM) 下运行的反激式转换器,其中包含几个寄生元件,如初级和次级漏电感、MOSFET 的输出电容和次级 二极管的结电容。

当 MOSFET关断时,初级电流 (id) 在 短时间内为 MOSFET 的 COSS 充电。当 COSS (Vds) 两 端的电压超过输入电压及反射的输出电压之和 (Vin+nVo) 时,次级二极管导通,因此励磁电感 (Lm) 两 端的电压被箝位至 nVo。

因此,Llk1 和 COSS 之间存在谐振,具有高频和高压浪涌。MOSFET 上过高的电压可能 导致故障。在 CCM 运行模式下,次级二极管保持导通 直至 MOSFET 栅极导通。

当MOSFET导通时,次级二 极管的反向恢复电流被添加至初级电流,因此在导通瞬 间初级电流上出现较大的电流浪涌。同时,由于在 DCM 模式下次级电流在一个开关周期结束前干涸, Lm 和 MOSFET 的 COSS 之间存在谐振。

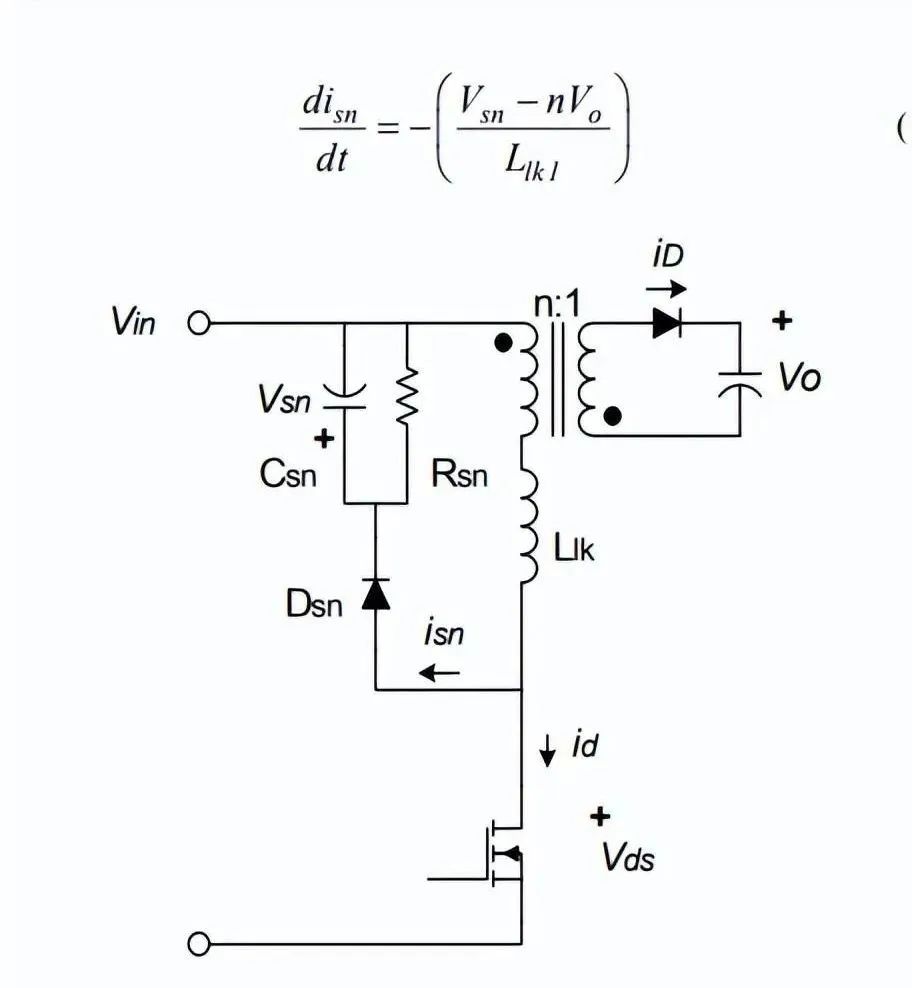

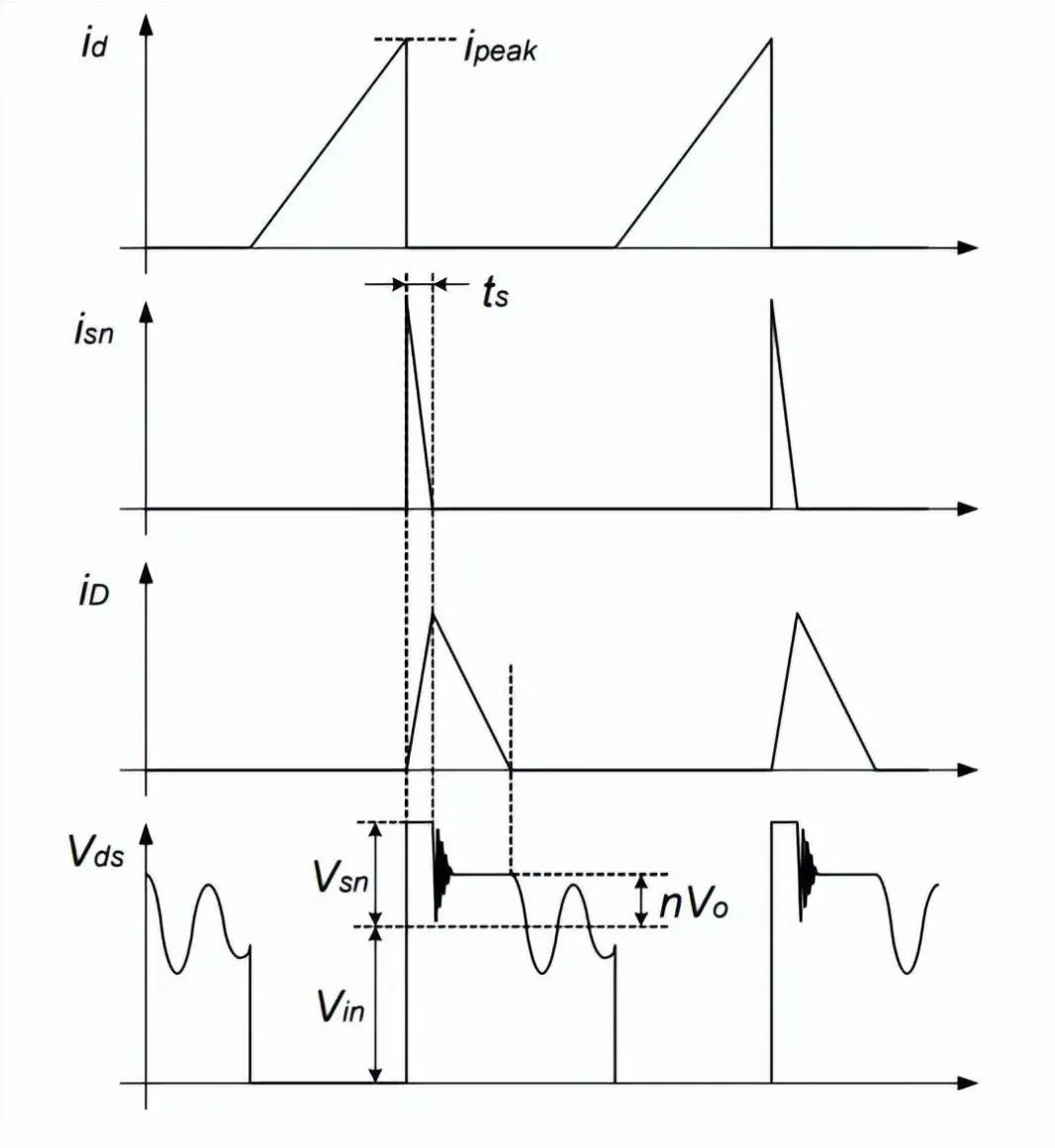

可通过添加一个额外的电路,将由于 Llk1 和 COSS 之间 的谐振产生的过高电压压制到一个可接受的电平,从而 保护主开关。图 2 和 3 显示 RCD 缓冲电路及其主要波 形。当 Vds 超过 Vin+nVo 时,RCD 缓冲电路通过导通缓 冲二极管 (Dsn) 吸收漏电感中的电流。

假定缓冲电容足够大,以致其电压在一个开关周期内不会发生变化。当 MOSFET 关断并且 Vds 被充电至 Vin+nVo 时,初级电流通过缓冲二极管 (Dsn) 流至 Csn。同时,次级二极管导 通。因此, Llk1 两端的电压为 Vsn-nVo。i sn 的斜率如下所示:

其中, isn 指流至缓冲电路的电流, Vsn 指缓冲电容 Csn 两端的电压,n 指主变压器的匝比,Llk1 指主变压器的漏 电感。时间 ts 可以表达为:

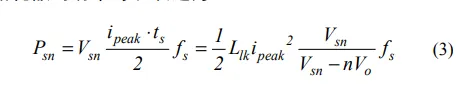

其中, ipeak 指初级峰值电流。缓冲电容电压 (Vsn) 应该在最小输入电压和满载条件下 确定。一旦确定了 Vsn,最小输入电压和满载条件下缓冲 电路耗散的功率可以表达为:

其中,fs 指反激式转换器的开关频率。Vsn 应该为 nVo 的 2 至 2.5 倍。若 Vsn 很小,可能导致缓冲电路中出现严 重的损耗,如上面方程式所示。

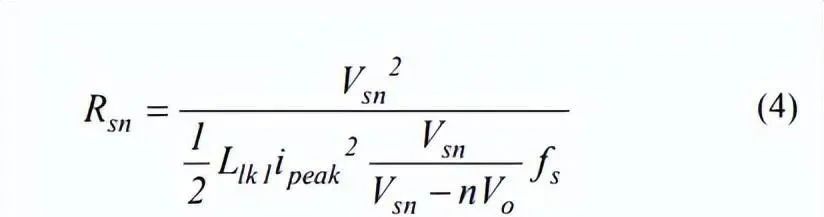

另一方面,由于缓冲电阻 (Rsn) 消耗的功率为 Vsn2/Rsn, 电阻可由下式得出:

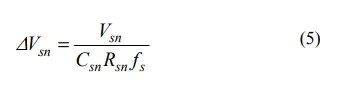

应该根据功耗,选择缓冲电阻以及合适的额定功率。缓冲电容电压的最大纹波可由下式得出:

通常,合理的纹波为 5-10%。因此,可采用上述方程式 计算缓冲电容。

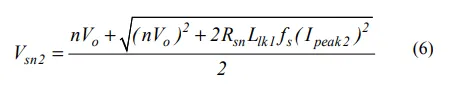

当转换器设计为 CCM 运行模式时,漏极峰值电流以及缓冲电容电压随输入电压增加而降低。最大输入电压和满载条件下的缓冲电容电压可由下式得出:

其中,fs 指反激式转换器的开关频率,Llk1 指初级端漏电 感,n 指变压器匝比,Rsn 指缓冲电阻,Ipeak2 指最大输入电压和满载条件下的初级峰值电流。

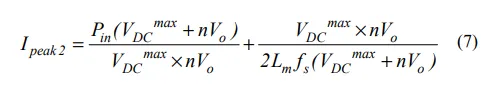

当转换器在最大 输入电压和满载条件下以 CCM 模式运行时,Ipeak2 可由下式得出:

当转换器在最大输入电压和满载条件下以 DCM 模式运 行时, Ipeak2 可由下式得出:

其中, Pin 指输入功率, Lm 指变压器的励磁电感, VDCmax 指整流后的最大直流输入电压。验证在瞬变期间和稳态期间, Vds 最大值分别低于 MOSFET 额定电压 (BVdss) 的 90% 和 80%。缓冲二极管的额定电压应该高于 BVdss。通常,在缓冲电路中采 用额定电流为 1 A 的超快二极管。

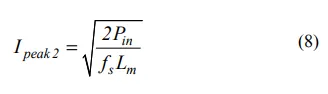

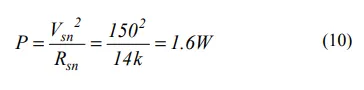

某个采用 FSDM311 的适配器具有以下规格:85Vac 至 265Vac 的输入电压范围,10W 输出功率,5V 输出电 压,和 67kHz 开关频率。当 RCD 缓冲电路采用一个 1nF 缓冲电容和一个 480kW 缓冲电阻时,图 4 显示交流 开关导通瞬间,在 265Vac 的几个波形。

图 4. 包含 1 nF 缓冲电容和 480 kW 缓冲电阻的启动波形

在图 4-7 中,通道 1 至 4 分别代表漏极电压(Vds,200 V/div),电源电压 (VCC, 5 V/div),反馈电压 (Vfb, 1 V/div)和漏极电流(Id,0.2 A/div)。内部 SenseFET 上的最大电压应力大约为 675 V,如图 4 所示。根据数 据表,FSDM311 额定电压为 650V。额定电压过高的原 因有两个:错误的变压器设计和 / 或错误的缓冲电路设 计。图 5 显示原因。

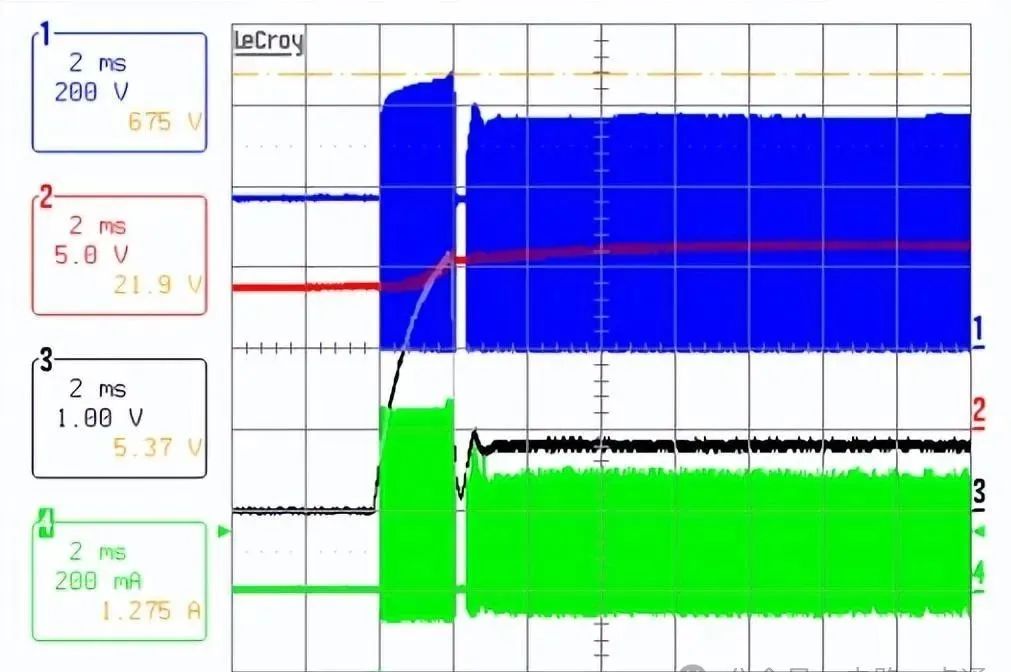

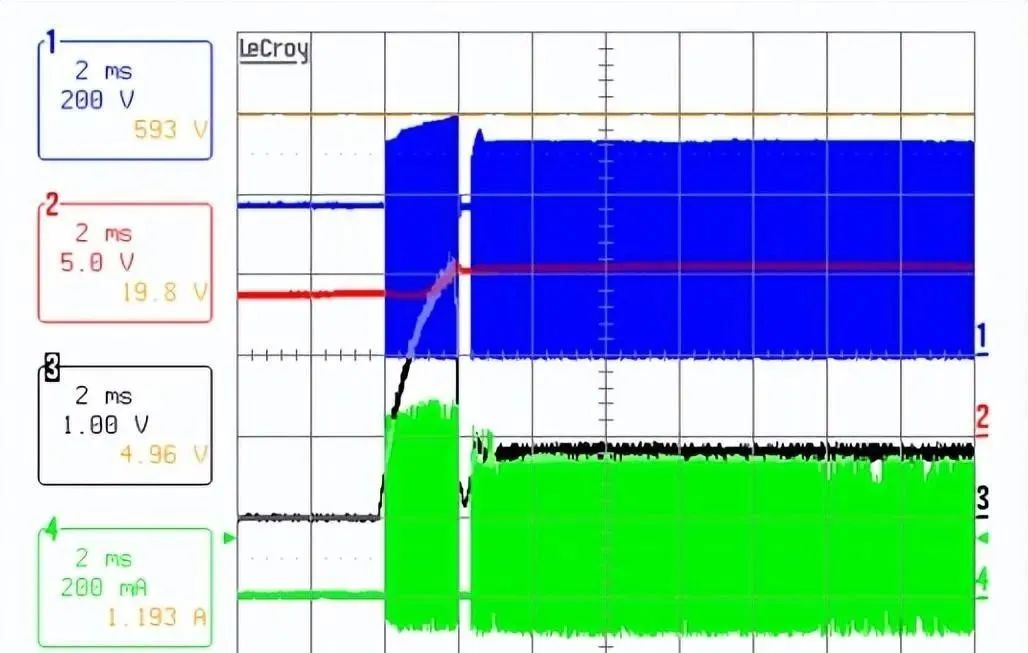

图 5. 稳态波形,带有 1 nF 缓冲 电容和 480 kW 缓冲电阻

为了保持可靠性,稳态时的最大电压应力应该等于额定 电压的 80% (650V * 0.8 = 520 V)。图 5 显示稳态时,并 且 Vin = 265 Vac 时,内部 SenseFET 上的电压应力高于 570 V。然而,Vin+nVo 约为 450 V (= 375V + 15 * 5V), 这说明变压器匝比为 15,这是一个合理的值。因此,缓 冲电路必须重新设计。

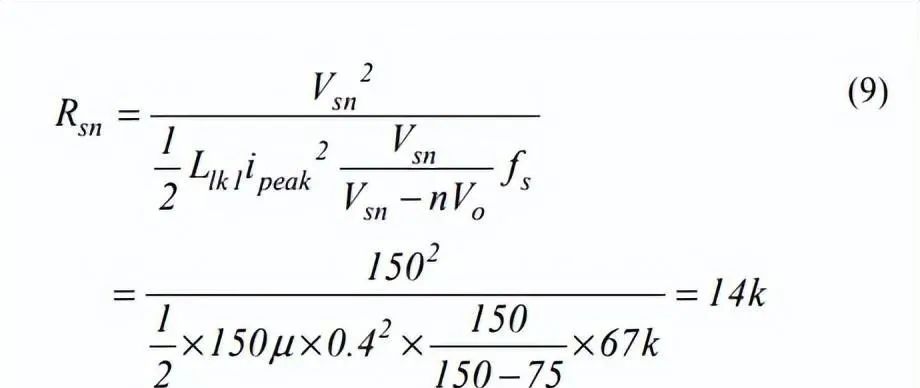

使 Vsn 为 nVo 的两倍,即 150 V,并且测得的 Llk1 和 i peak 分别为 150 μH 和 400 mA。缓冲电阻计算如下:

Rsn 释放的功率计算如下:

使缓冲电容电压最大纹波为 10%,则缓冲电容可由下式 得出:

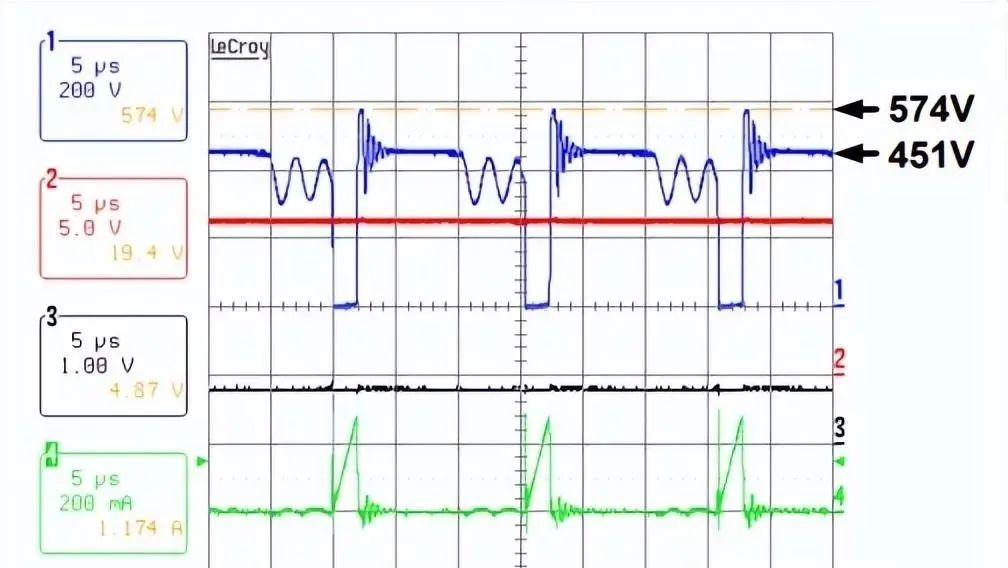

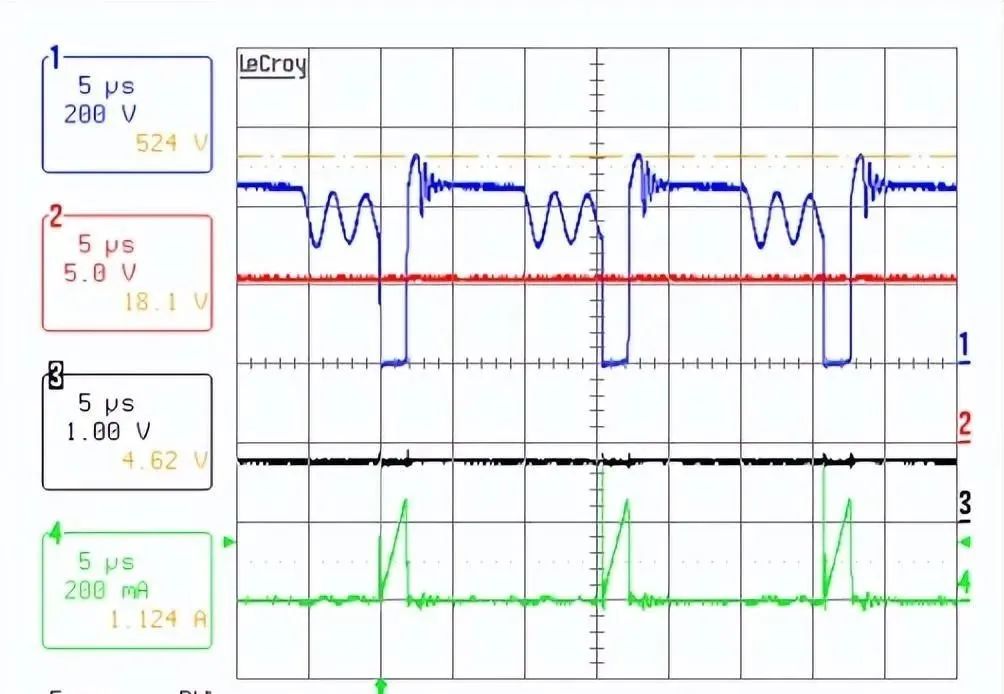

图 6 和 7 显示采用 14 kW (3 W) 和 10 nF 时的结果。

图 6. 启动波形,带有 10 nF 缓冲电容和 14 kW 缓冲电阻

图 7. 稳态波形,带有 10 nF 缓冲 电容和 14 kW 缓冲电阻

启动和稳态时内部 SenseFET 上的电压应力分别为 593 V 和 524 V。它们分别为 FSDM311 额定电压的 91.2% 和 80.6% 左右。

声明:内容来源于网络,版权归原作者所有。如有侵权,请联系删除。

0

0