一、明确优先级:重要的事情优先做

在开始布局之前,我们需要明确一个重要的原则:不是所有规则都同等重要。在众多的设计要求中,高速信号、大功率器件以及微弱信号的处理是重中之重。高速信号的走线需要特别注意,因为它们对信号完整性要求极高,任何微小的干扰都可能导致信号失真甚至系统故障。大功率器件则需要考虑散热和电源管理,避免因过热或电源不足而损坏。而微弱信号部分,如传感器信号,需要精心保护,防止受到其他强信号的干扰。只有优先处理好这些关键部分,才能确保整个电路板的稳定性和可靠性。

二、建立「分层决策树」破除信息过载

1. 核心矛盾分级(权重排序)

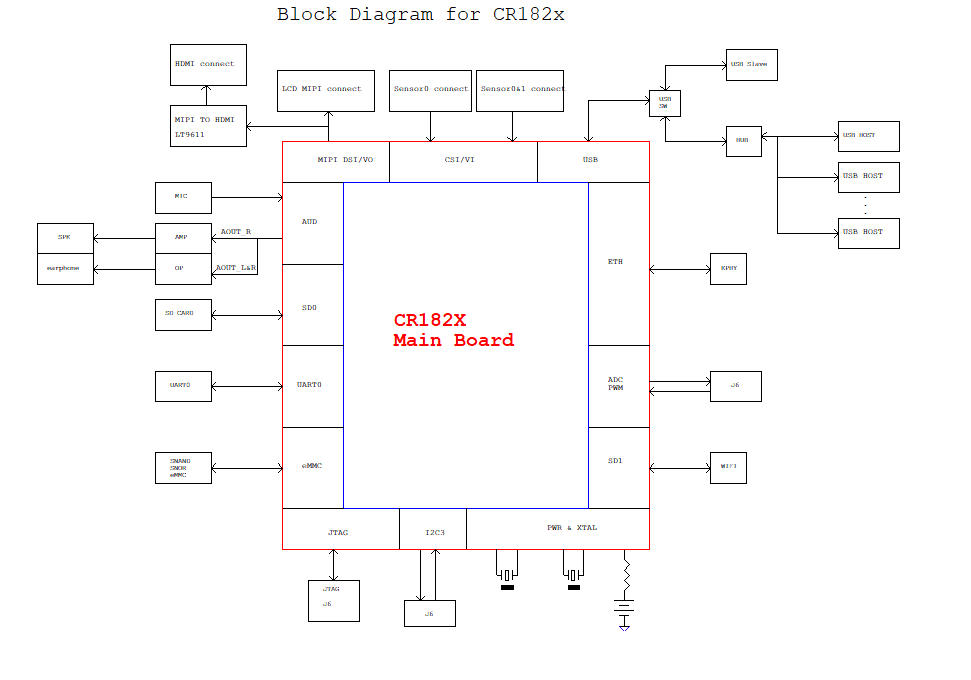

我们的PCB最重要的是MIPI(高速),然后是BT656,再就是TF卡,eMMC;这些接口处理完成之后,都是低速的SPI、I2C、UART、GPIO等。

当我们优先处理完电源、时钟问题之后,接口就按照重要级逐个优先处理。

2. 接受“80分法则”

初次布局目标不是完美,而是避免灾难性错误 (如电源短路、高速信号跨分割)。其他问题可在布线阶段优化。

三、实施「先固化再优化」布局术

1. 摆放“不可动件”锚点

- 连接器(位置机械固定)

- 发热器件(预占散热通道)

- 核心芯片(确定供电区域)

Step1:放置所有接插件 → Step2:固定散热器/功率管 → Step3:定位主控芯片及电源模块

2. 模块化拼图策略

将电路按功能切分为5-8个模块(如:电源区|MCU核心区|传感器接口|电机驱动),在草稿纸上手绘模块位置 ,允许模块内拥挤但确保:

- 模块间高压/高频干扰源远离敏感区

- 模块供电链路不交叉(如:12V→DCDC→3.3V线性稳压→MCU为直线流向)

四、决策比挑战更重要同事正在纠结这个网络变压器很难放置,空间不够。我直接告诉他,这个项目不用,实在不行就删除,不要考虑预留。我今天刚刚决策:把TF卡删除,预留一个8pin的连接器,用延长线做备份。另外比较连接器与TF卡座价格。同时验证一下可行性。然后直接删除这个器件。

五、基于物理定律布局布线:经验主义不可取

在布局布线时,不能仅仅依赖经验之谈,而应基于物理定律进行设计。PCB走线的实际阻抗和空间耦合强度是两个关键因素。走线的阻抗会影响信号的传输质量和电源的稳定性,而空间耦合则可能导致信号之间的干扰。例如,高速信号走线需要保持一定的间距,以避免信号之间的串扰;电源线和地线的阻抗也需要尽量降低,以减少电压降和电磁干扰。通过合理计算和设计,确保走线的阻抗符合设计要求,同时最大限度地减少空间耦合的影响,是实现高质量PCB设计的基础。

要在心中构建一个板子上的电磁场。

六、理顺电源树与时钟树:电源和时钟是基础

电源树的布局对于整个电路板的稳定性至关重要。电源树的结构决定了电源的分配和管理,合理的电源树布局可以有效减少电源噪声的传播。同时,时钟信号的布局也需要特别注意。时钟信号是数字电路的同步信号,其质量和稳定性直接影响到整个系统的性能。高速走线的关联关系也需要仔细考虑,例如,差分信号对需要保持等长和等距,以确保信号的同步传输。通过理顺电源树、时钟关系以及高速走线的关联关系,可以有效提高电路板的信号完整性和可靠性。

七、高速走线预留参考平面:信号完整性保障

在高速信号走线时,预留参考平面的位置是必不可少的。参考平面可以为高速信号提供稳定的参考电平,减少信号的反射和干扰。例如,在差分信号对的走线中,参考平面可以有效降低差分信号之间的串扰,提高信号的质量。同时,参考平面还可以作为电源和地的参考,进一步优化电路板的电磁兼容性。因此,在布局高速信号走线时,一定要预留足够的空间用于参考平面的设计,确保信号的完整性和稳定性。

八、去耦电容靠近用电侧:稳定电源的关键

去耦电容在PCB设计中扮演着至关重要的角色。无论是模拟器件还是数字器件,都需要在电源引脚附近连接一个旁路电容,通常电容值为0.1μF。去耦电容的作用是为器件提供稳定的电源,减少电源噪声的干扰。对于模拟电路,旁路电容可以旁路电源上的高频信号,防止这些高频信号进入敏感的模拟芯片,从而避免信号路径上的噪声引入。对于数字电路,去耦电容则作为“微型”电荷库,在数字器件执行开关动作时提供额外的电荷,防止电源电压发生大的变化,避免数字信号电平进入不确定状态。因此,去耦电容必须尽量靠近器件的电源引脚,引脚尽量短,以减小走线的感抗,确保其能够有效地发挥去耦作用。

电源时钟连接器,还有定位孔等确定性的组件放置之后,重点看以SoC或者MCU或者CPU、GPU为核心的芯片组成的小系统。这个小系统包括处理器周边所有器件,和去耦电容,要围绕在处理器周围,看成一个整体。

九、保证地线良好:降低电磁干扰、保障电源完整性

地线是PCB设计中不可或缺的一部分,良好的地线布局可以有效降低电磁干扰。地线的作用是为电路提供一个稳定的参考电平,同时作为信号回流路径。如果地线布局不当,可能会导致地电位不一致,从而产生共模噪声和差模噪声。例如,电源线和地线配合不当可能会设计出系统环路,增加电磁干扰的可能性。因此,在布局地线时,应尽量采用大面积的接地平面,减少地线的阻抗,确保地电位的一致性。同时,数字地和模拟地应分开布线,最后在合适的位置连接到系统地,以避免数字信号对模拟信号的干扰。通过合理设计地线,可以有效降低电磁干扰,提高电路板的信号完整性和可靠性。

0

0