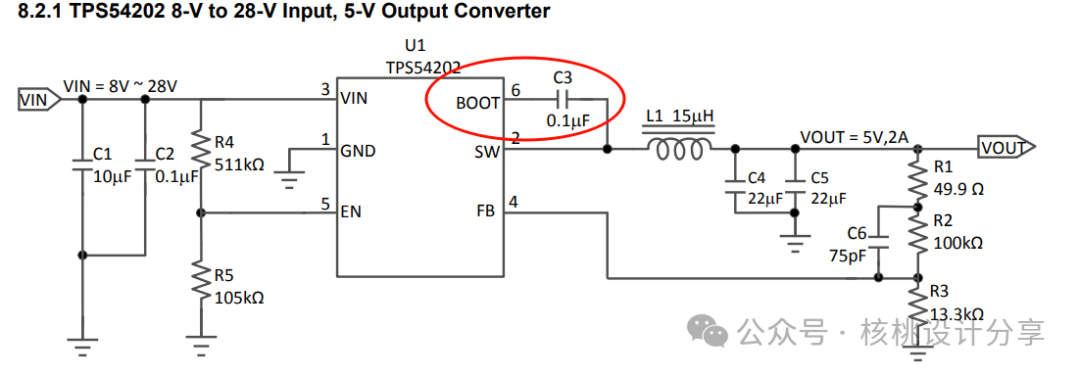

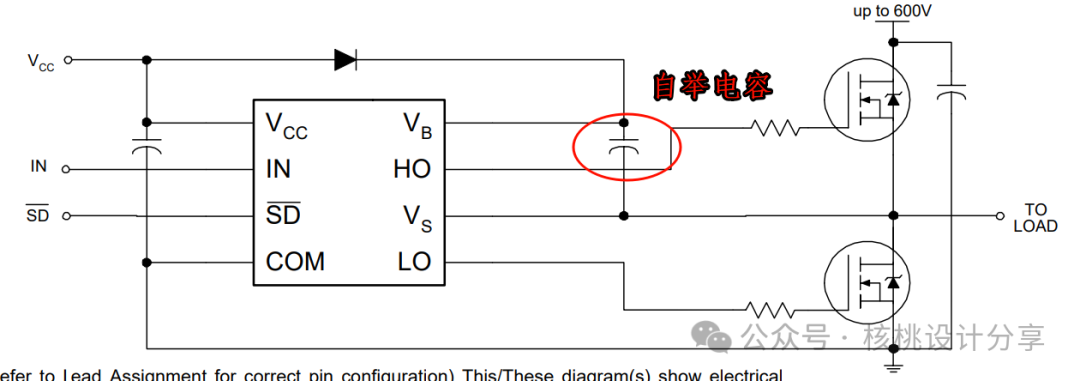

如上图所示,就是接在BOOT和SW管脚之间的一个电容,一般情况下,常用0.1uF即可满足要求。那加这个电容的作用是什么?先来了解一下基本概念:自举电容其核心的作用就是通过电容充放电过程,把低侧电压与电源叠加形成更高的驱动电压,主要用于控制高侧功率器件(比如MOS管)的栅极,使之顺利导通。可能对于一些初学者来说,上面这段话过于抽象了,那我们换个角度去思考。

如上图所示,就是接在BOOT和SW管脚之间的一个电容,一般情况下,常用0.1uF即可满足要求。那加这个电容的作用是什么?先来了解一下基本概念:自举电容其核心的作用就是通过电容充放电过程,把低侧电压与电源叠加形成更高的驱动电压,主要用于控制高侧功率器件(比如MOS管)的栅极,使之顺利导通。可能对于一些初学者来说,上面这段话过于抽象了,那我们换个角度去思考。 我们尝试从DC-DC的基本拓扑来展开,可能大伙更容易接受。(1)使用PMOS搭建的电源拓扑,如下图所示:

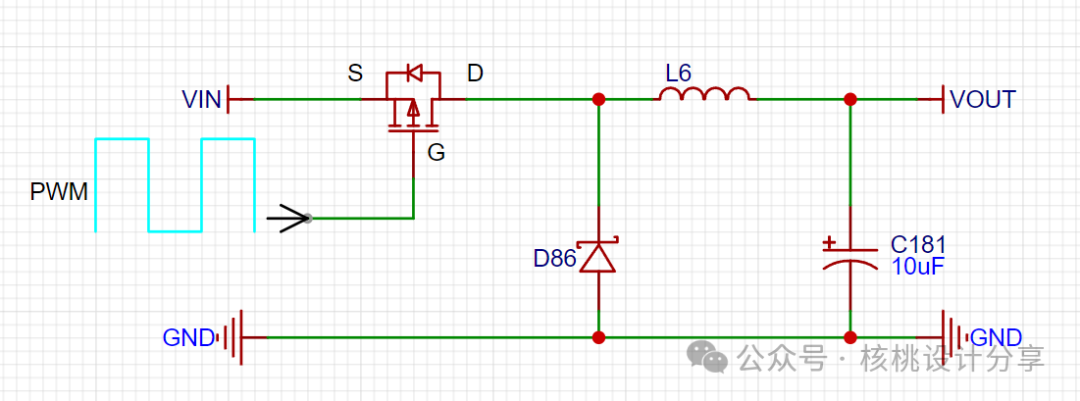

我们尝试从DC-DC的基本拓扑来展开,可能大伙更容易接受。(1)使用PMOS搭建的电源拓扑,如下图所示: 从上图可以知道,要使MOS管导通,只需要满足输入的PWM为低电平(0V)即可(Vgs<0)。那如果说把上图中的PMOS更换成NMOS呢?会怎样,如下图所示:

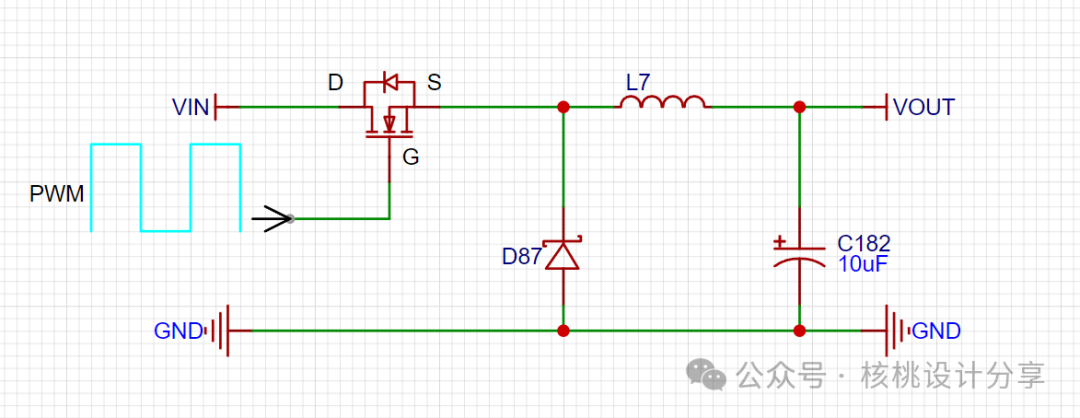

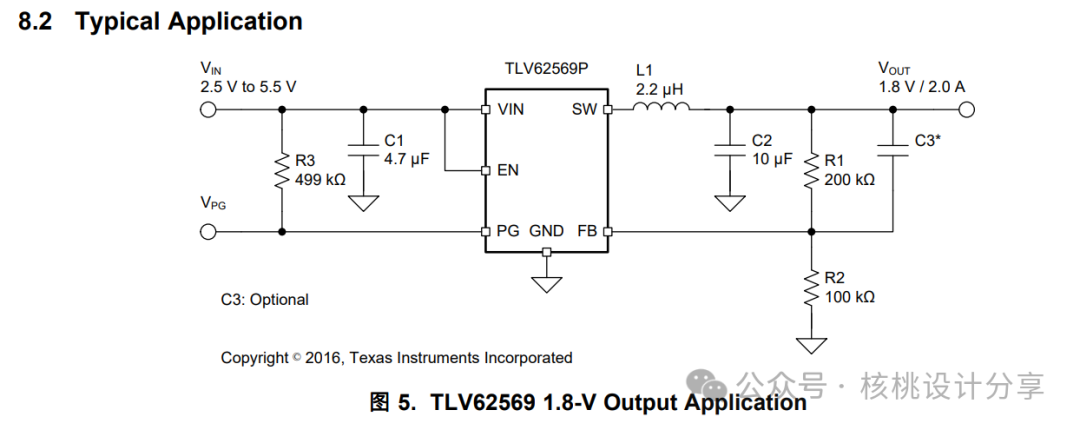

从上图可以知道,要使MOS管导通,只需要满足输入的PWM为低电平(0V)即可(Vgs<0)。那如果说把上图中的PMOS更换成NMOS呢?会怎样,如下图所示: 那要想上图中的NMOS管导通就需要满足Vgs>0,那怎么样才能让PWM的电压高于S极呢?这时候,加上自举电容就能解决这个问题了。这个时候,有小伙伴就会问了,那么麻烦,直接用PMOS不就行咯!是的,直接用PMOS是没有问题,市面上不用自举电容的DC-DC芯片也是有的,比如TLV62569PDDCR,如下图所示:

那要想上图中的NMOS管导通就需要满足Vgs>0,那怎么样才能让PWM的电压高于S极呢?这时候,加上自举电容就能解决这个问题了。这个时候,有小伙伴就会问了,那么麻烦,直接用PMOS不就行咯!是的,直接用PMOS是没有问题,市面上不用自举电容的DC-DC芯片也是有的,比如TLV62569PDDCR,如下图所示:

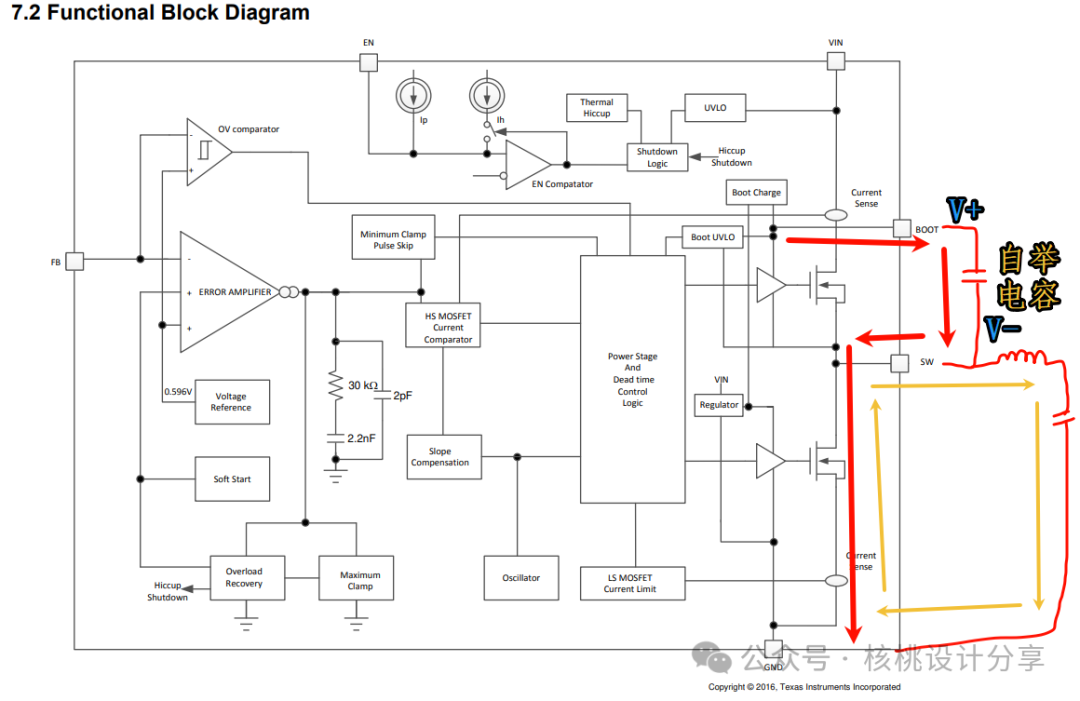

但从MOS管的生产工艺上看,PMOS的导通电流可以做不到很大,相同成本下,NMOS电流可以做到很大(Rdson相对较低)。我们以TPS54202DDCR内部框架图来举例,如下图所示:

上图中我们可以看出是有两个NMOS管的,一个在上面,一个在下面,分别称为高侧MOS管和低侧MOS管。假如某一时刻低侧MOS管导通了,那自举电容会如上图中的红色路径所示进行充电,直到充到和Boot Charge一样的电压。而此时DC-DC芯片是处于续流的状态,续流路径如上图黄色箭头所示。输出主要靠电感和电容维持。当低侧MOS管被关闭时,要想让高侧MOS管导通,就必须满足Vgs>0,而高侧MOS的S极是接在SW(输出端),G极是接在内部的高侧驱动器,而自举电容直接并在BOOT和SW之间,在低侧MOS管关闭,高侧MOS管需要导通时,此时自举电容就会向高侧MOS提供导通能量,使之满足导通条件Vgs>0,这样,就可满足下一个循环了。高侧MOS管关闭时,下侧MOS管导通,继续为自举电容进行充电,然后下管MOS关闭,自举电容放电,高侧MOS导通。其实不单单是DC-DC电路中有用到自举电容,驱动电机的H桥驱动电路中也同样采用这种方式,原理都是一样。

上图中我们可以看出是有两个NMOS管的,一个在上面,一个在下面,分别称为高侧MOS管和低侧MOS管。假如某一时刻低侧MOS管导通了,那自举电容会如上图中的红色路径所示进行充电,直到充到和Boot Charge一样的电压。而此时DC-DC芯片是处于续流的状态,续流路径如上图黄色箭头所示。输出主要靠电感和电容维持。当低侧MOS管被关闭时,要想让高侧MOS管导通,就必须满足Vgs>0,而高侧MOS的S极是接在SW(输出端),G极是接在内部的高侧驱动器,而自举电容直接并在BOOT和SW之间,在低侧MOS管关闭,高侧MOS管需要导通时,此时自举电容就会向高侧MOS提供导通能量,使之满足导通条件Vgs>0,这样,就可满足下一个循环了。高侧MOS管关闭时,下侧MOS管导通,继续为自举电容进行充电,然后下管MOS关闭,自举电容放电,高侧MOS导通。其实不单单是DC-DC电路中有用到自举电容,驱动电机的H桥驱动电路中也同样采用这种方式,原理都是一样。

0

0