上一讲我们介绍完了前段STI 模块形成的过程,我们继续介绍前段的另一个模块。即阱(Well)定义模块。

阱(Well)是指在硅表面注入掺杂物的局部区域,以调整其电气特性并优化晶体管性能。阱还通过在邻近PMOS和NMOS器件之间建立二极管屏障,增强了浅沟槽隔离提供的电气隔离效果。

-

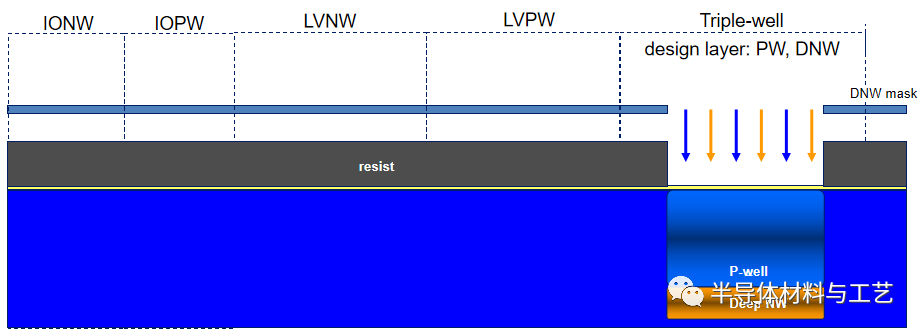

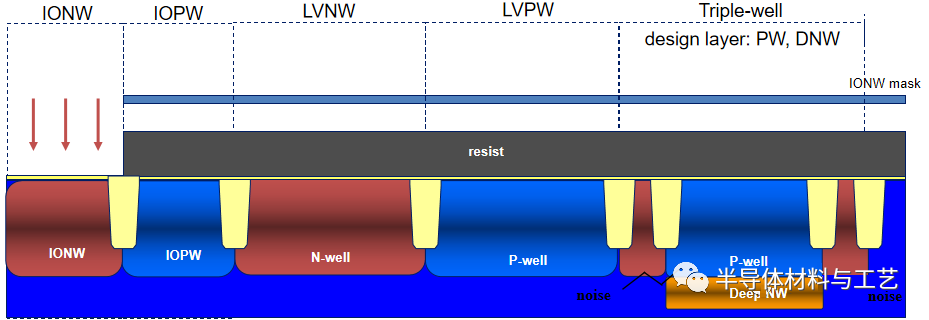

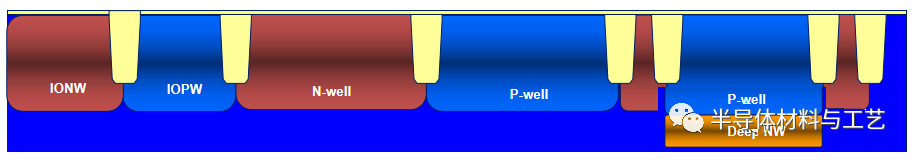

DNW(Deep NWell) IMP(PR Strip 步骤已省略,下同)

一般在做IMP之前,要先Coating 光阻(更先进的节点可能需要加BARC/TARC,比如在28节点以下),然后曝光显影定义出需要IMP的位置。对于DNW我们一般会打P并且IMP会分几次注入。

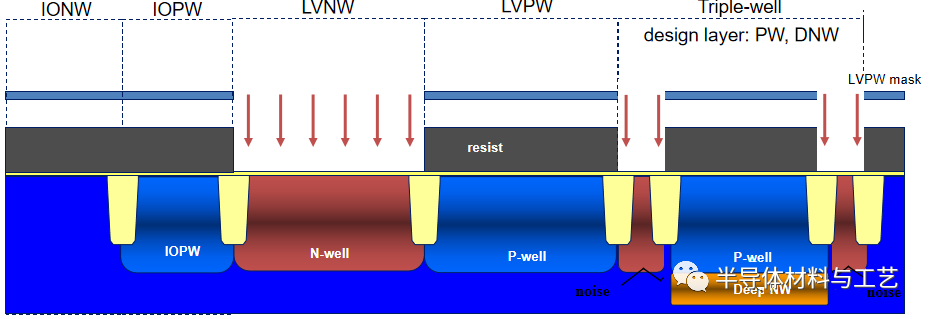

2. LVPW IMP

一般的普通的Logic 器件会分Core区和IO区。此处我们做打core区的IMP。

LV=Low Voltage,SV=RV=Standard Voltage=Regular Voltage

HV=High Voltage 一般通过IMP反型离子/元素的剂量来调控阈值电压(Threshold Voltage)

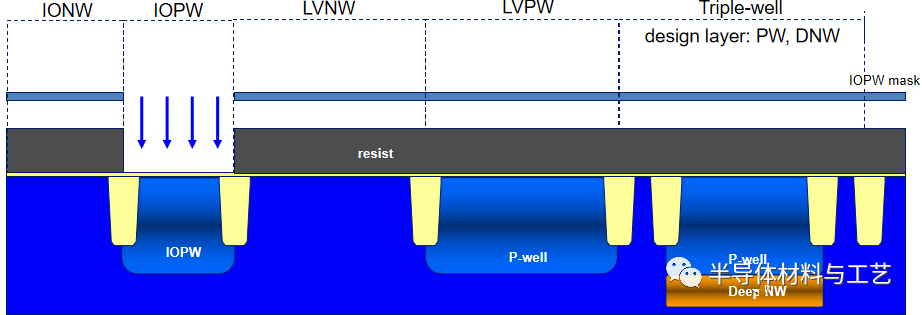

3. IOPW IMP

4. LVNW

5. IONW

6. Well Anneal

最后通过退火(Anneal)激活注入的杂质并修复损伤。

7. 注:正常Well IMP会打三次主要原因是为了注入不同的深度。

第一次离子注入较深,能量很高,调节阱的浓度,降低阱的电阻,有效防止闩锁效应(Latch Up)。

第二次离子注入较浅,能量较低,调节沟道浓度,防止器件源漏穿通漏电(APT=Anti-Punch Through)。

第三次离子注入主要集中在表面,能量很低,主要调节器件的阈值电压。

Well 模块比较Care的点有PR residue以及Thermal budge和Plasma induce damage等

我们继续介绍前段Dual Gate Oxide模块和Poly Gate模块。

(一)DGO Module

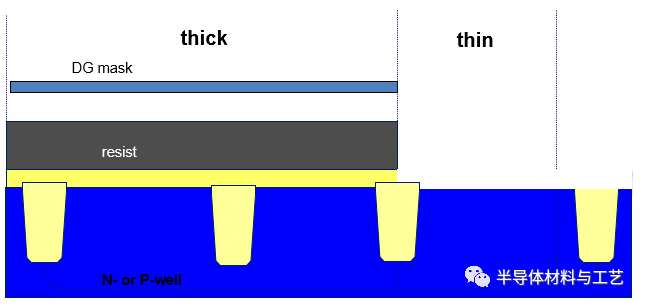

1.DGO Growth

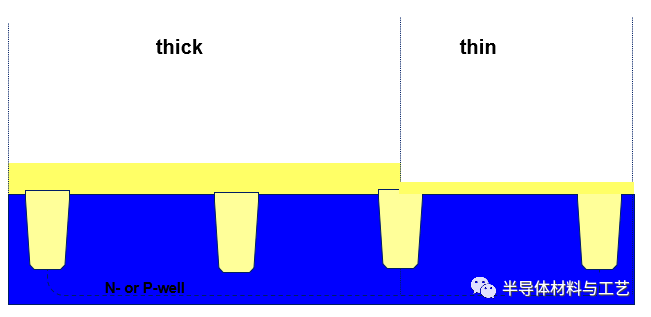

在长Gate Ox前先做一道Wet clean 去除表面的PA和一些污染源。然后通过炉管的方式长一层大约40A左右的Ox,用PR挡住需要做厚栅氧部分,用干发刻蚀去除薄栅氧。做完的示意图如下:

接下来通过ISSG的方法继续长一层30A左右的薄Ox。

ISSG=In-situ Steam Generation 原位水气生成

反应式:Si + 2O2 + 2H2→SiO2 + 2H2O

一种新型低压快速氧化技术,主要用于超薄氧化物薄膜生长,由于原子氧的强氧化作用,其最终得到的氧化物薄膜体内缺陷少,界面态密度小,氧化物的薄膜质量较高。

此外,此处通常用ISSG+DPN+PNA的方式。

DPN:Decoupled Plasma Nitridation

PNA:Post Nitridation Anneal

主要目的是:

(1).ISSG oxide has best uniformity, corner rounding.

(2).With DPN and PNA, increase GOX k value.

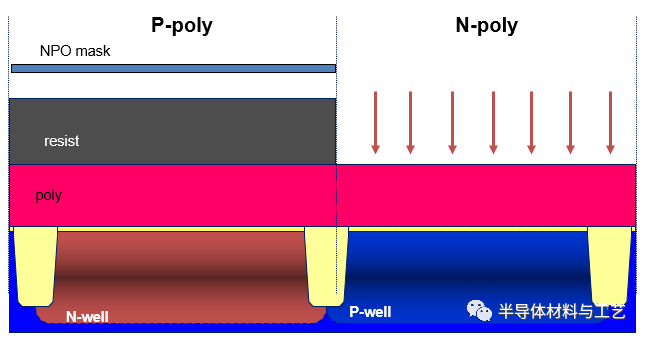

(二)Poly Gate Module

1.Poly deposition

首先Dep一层1000A的Poly,接下来做一道Poly Pre-doping.

Q:Why need pre-doping activation?

A:1.To re-distribute pre-doping profile. Make pre-doping ion profile more uniform in poly for easier etch recipe tuning.

2.Reduce Poly depletion.

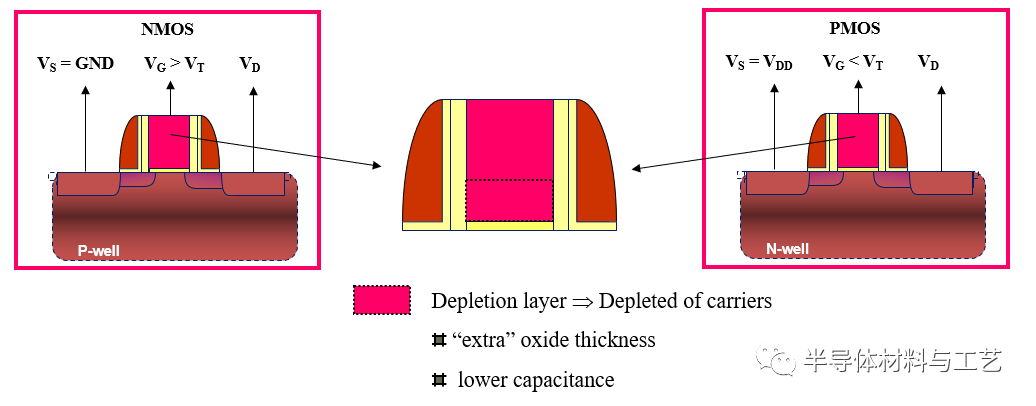

Q:What is poly depletion?

Poly depletion

Factors of poly depletion:

-

Silicide suck-out effects

-

Insufficient implant dose

-

Dopant evaporation

Poly depletion results in:

-

Reduced inversion capacitance Þ“artificially” thicker oxide

-

Reduced current drive

Poly depletion is improved with:

-

Poly gate changed to metal gate

-

Sufficient Poly doping or ION activation

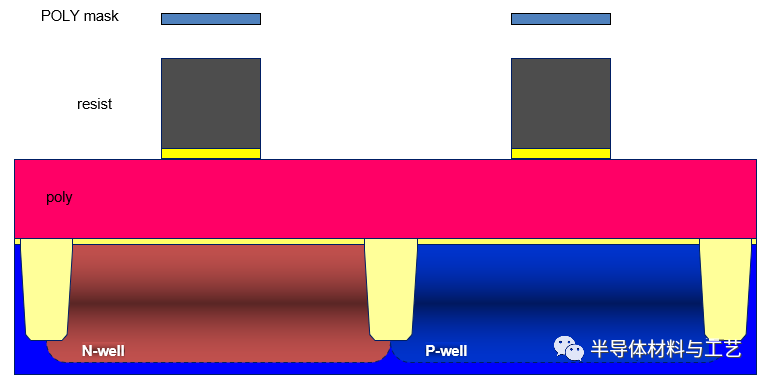

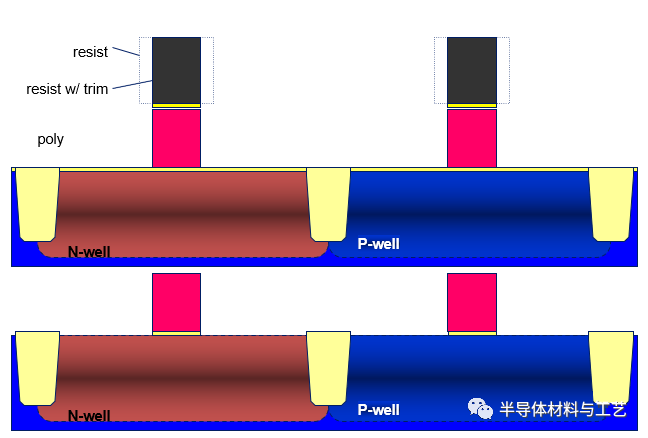

2.Poly hardmask oxide deposition

用CVD的方式沉积一层350A左右的oxide,Coating PR+BARC.

3.Poly cut

到此。Poly 模块已经结束,接下来一讲会给大家介绍侧墙工艺(Spacer Sidewall)

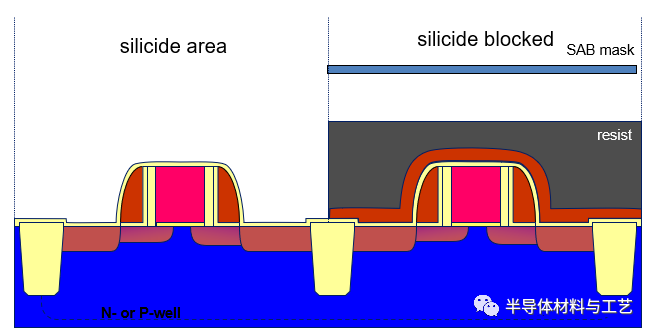

(一).SAB( Self Aligned Silicide Block自对准金属硅化物阻挡层)工艺

-

LTO & SiN DepS/D IMP做完后,继续Dep 一层LTO(低温氧化层),然后进行Spike Anneal(和S/D的Anneal merge在一起,降低thermal)。用PECVD的方式沉积一层150A左右的SiN,接下来用PR遮挡住non-silicide的区域。

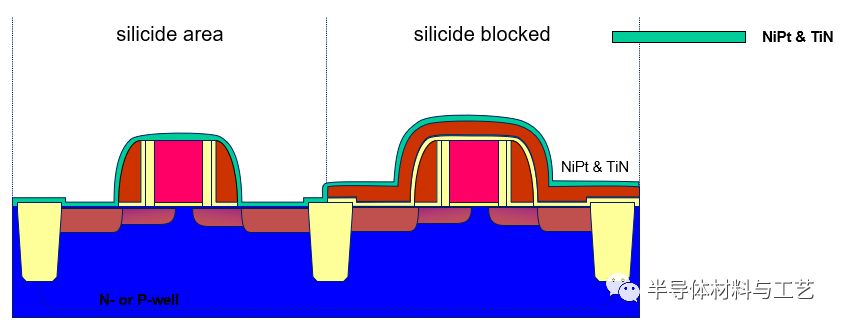

2.PR Strip & Oxide Etch

用O2和HF分别拔掉PR和Ox,然后用PVD的方式沉积Ni金属。

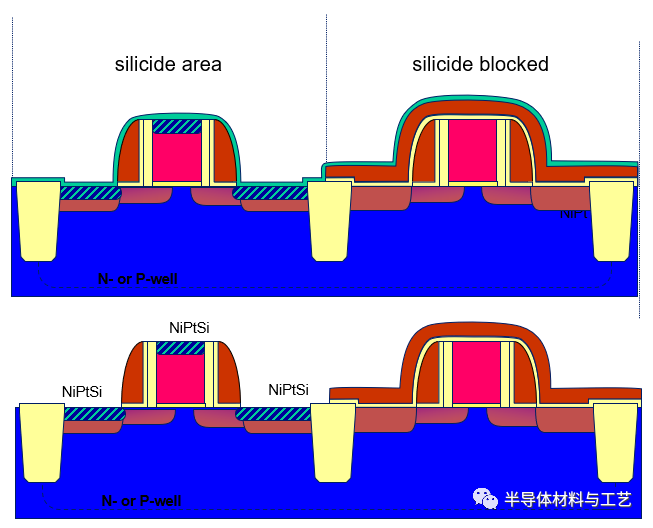

3.NiSix Anneal(Double)

Ni沉积完通过第一次Anneal1形成高阻态的NiSix,然后去除多余未反应的metal Ni,接下来进行第二次Anneal2形成稳定低阻态的NiSi2 silicide.

(二).ILD Module

ILD:Inter Layer Dielectric 层间介电层ILD工艺是指在器件与金属1(Metal 1)之间填充的介电材料,形成电性隔离,可以有效地隔离金属互联线与器件,降低金属与衬底之间的寄生电容,改善金属横跨不同的区域而形成寄生的场效应晶体管。ILD的介质材料一般是氧化硅。-

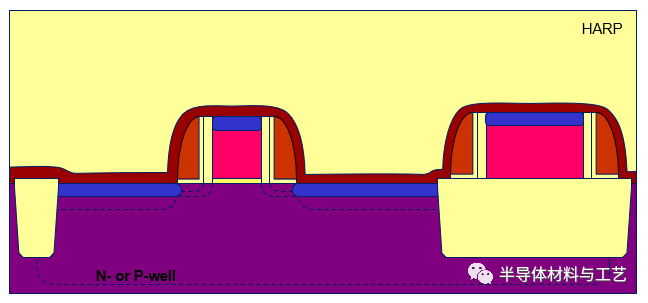

ILD Dep

用HARP的方式Dep一层大约8000A左右的Ox,然后通过CMP磨掉大约4000A的Ox,再过一道Wet clean。

3

3