eg:

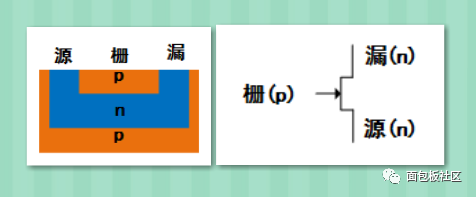

P-channel JFET:

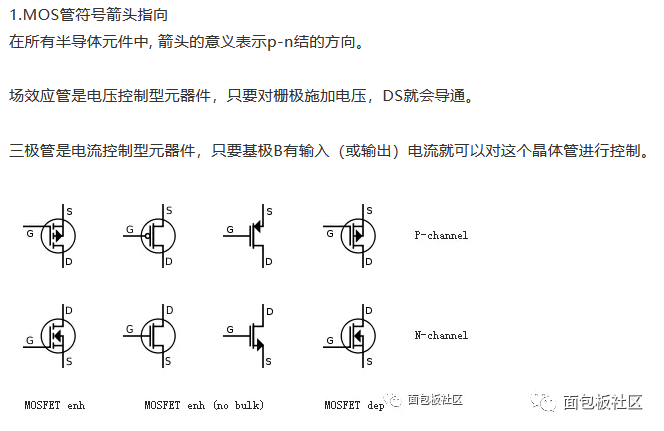

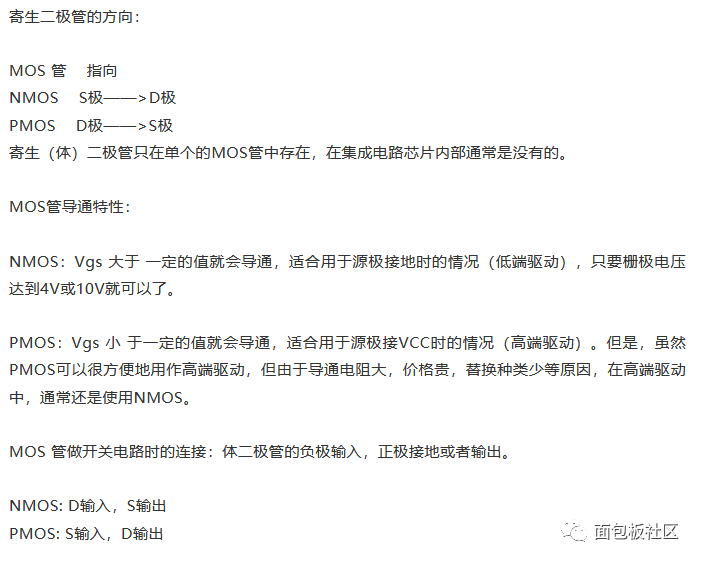

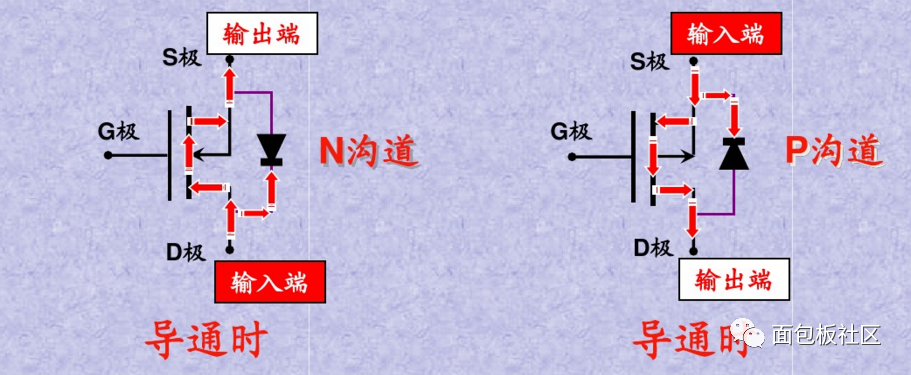

电路中的 MOS 管符号:

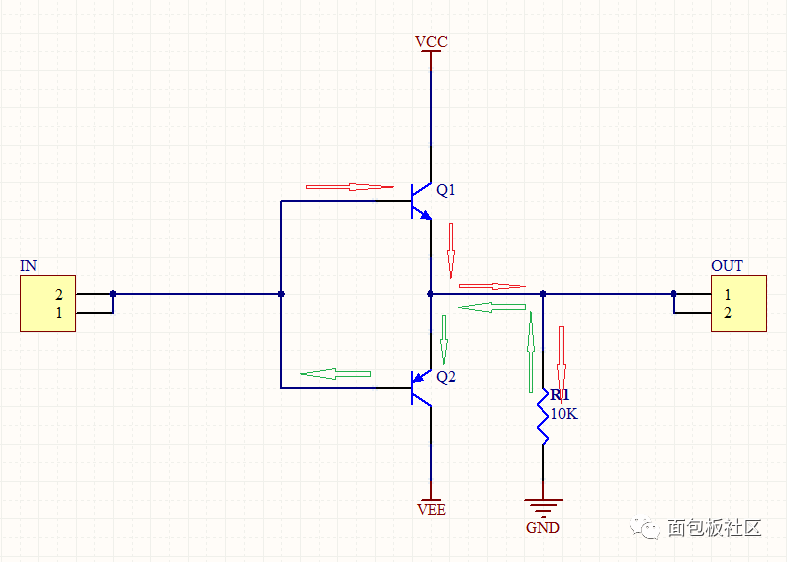

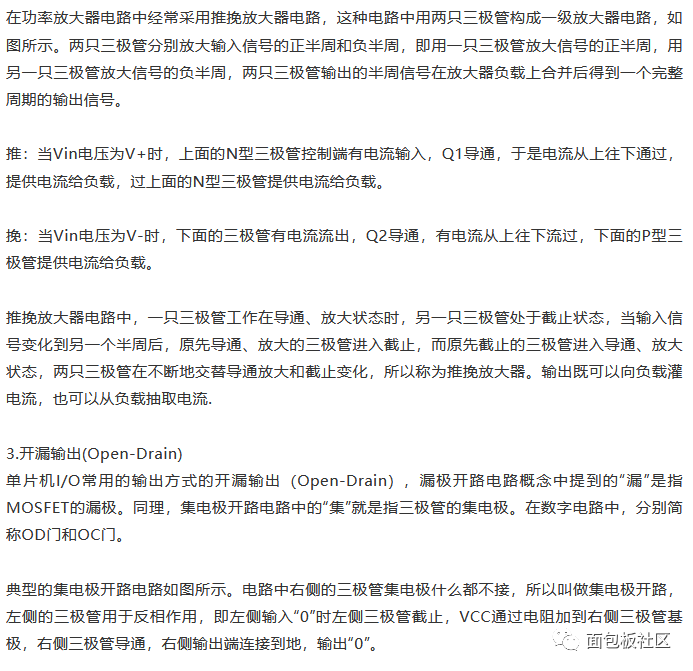

2.推挽输出(Push-Pull)

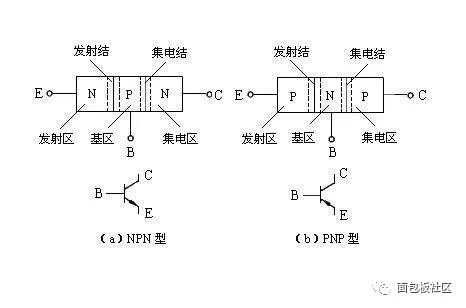

推挽输出是用两个晶体管或者场效应管构成的推挽电路,电路的特点就是输出电阻小。可以输出高,低电平,连接数字器件。push-pull 高低电平由IC的电源低定,不能简单的做逻辑操作等。push-pull是现在CMOS电路里面用得最多的输出级设计方式。

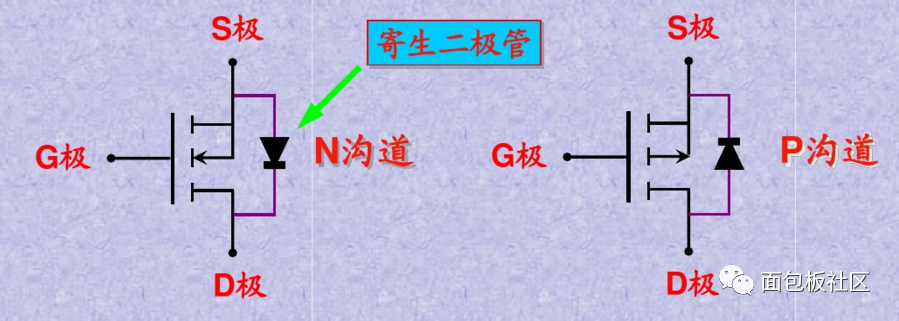

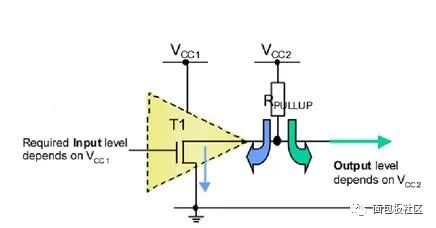

集电极开路输出除了可以实现多门的线与逻辑关系外,通过使用大功率的三极管还可用于直接驱动较大电流的负载,如继电器、脉冲变压器、指示灯等。由于现在MOS管用普遍,而且性能要比晶体管要好,所以很多开漏输出电路和推挽输出电路都用MOS管实现。

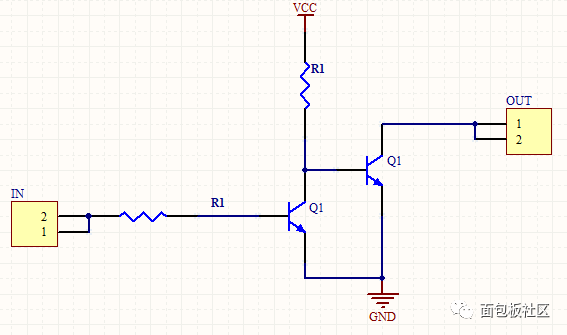

完整的开漏电路应由开漏器件和开漏上拉电阻组成。这里的上拉电阻R的阻值决定了逻辑电平转换的上升/下降沿的速度。阻值越大,速度越低,功耗越小。因此在选择上拉电阻时要兼顾功耗和速度。标准的开漏脚一般只有输出的能力。添加其它的判断电路,才能具备双向输入、输出的能力。

开漏电路做驱动器时,由于OC门电路的输出管的集电极悬空,使用时需外接一个上拉电阻R到电源VCC。OC门使用上拉电阻以输出高电平,此外为了加大输出引脚的驱动能力。上拉电阻阻值的选择原则:从降低功耗及芯片的灌电流能力考虑应当足够大;从确保足够的驱动电流考虑应当足够小。

可以利用改变上拉电源的电压,改变传输电平。如上图, IC的逻辑电平由电源Vcc1决定,而输出高电平则由Vcc2(上拉电阻的电源电压)决定。这样我们就可以用低电平逻辑控制输出高电平逻辑了(这样就可以进行任意电平的转换)。(例如加上上拉电阻就可以提供TTL/CMOS电平输出等。)

将OC门输出连在一起时,再通过一个电阻接外电源,可以实现**“线与”**逻辑关系。只要电阻的阻值和外电源电压的数值选择得当,就能做到既保证输出的高、低电平符合要求,而且输出三极管的负载电流又不至于过大。当这些引脚的任一路变为逻辑0后,开漏线上的逻辑就为0了。在I2C等接口总线中就用此法判断总线占用状态。

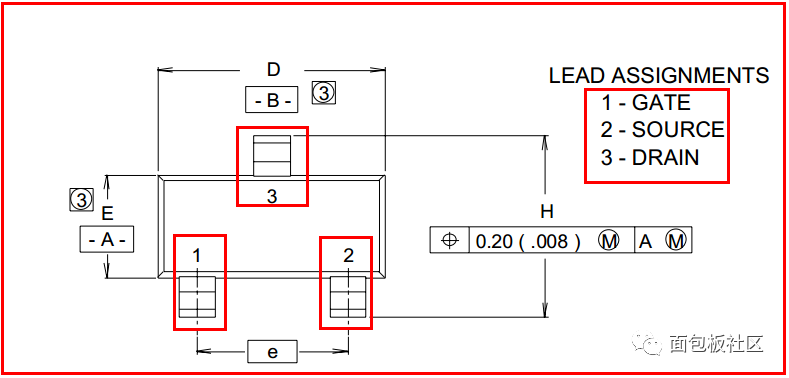

4.器件引脚排布

0

0