摩尔定律一直推动着集成电路特征尺寸的持续微缩,随着MOSFET(金属氧化物半导体场效应晶体管)沟道长度的减小,源极和漏极之间的距离变得越来越短,栅极对沟道的控制能力逐渐减弱。这一现象,即短沟道效应(Short Channel Effect,SCE),成为制约器件性能提升的关键因素之一。

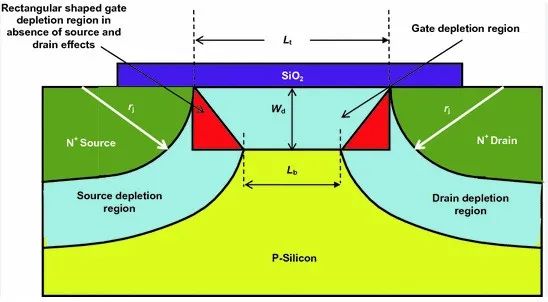

在长沟道器件中,等电位线是一维的,电场垂直于沟道表面,由栅极电压控制,沟道四周的“边缘效应”可以忽略不计。然而,在短沟道器件中,漏极和源极结构更靠近沟道,特别是当沟道长度小到可以与源漏结的耗尽区宽度相比拟时,短沟道器件的等电位线变为二维,源漏结的耗尽区对沟道内电势分布产生显著影响,导致一系列特性的改变。

二、短沟道效应的影响

-

阈值电压

短沟道器件的阈值电压对沟道长度变化非常敏感。随着沟道长度的减小,源漏结的耗尽区在整个沟道中所占的比重增大,栅极下表面形成反型层所需的电荷量减小,从而导致阈值电压降低。此外,漏致势垒降低(DIBL)效应也会影响阈值电压。当漏极电压增加时,漏极和衬底构成的PN结会导致势垒降低,从而使得阈值电压减小且电流增大,严重时甚至会导致源漏穿通,造成器件失效。

-

速度饱和效应

速度饱和效应是指当电场强度增加到一定程度时,载流子的漂移速度不再随电场强度的增加而增加,而是趋于饱和的现象。在短沟道器件中,由于电场强度过高,载流子速度达到极限,电流不再随漏极电压的增加而增加,导致电流饱和。这种效应在高速开关操作中尤为明显,会严重影响器件的开关速度和效率。

-

热载流子效应

由于短沟道器件的漏极存在一个强电场,该电场会对载流子进行加速,使其获得高动能成为热载流子,进而导致器件性能退化甚至失效。这一现象被称为热载流子效应(Hot Carrier Effect,HCE)。热载流子效应主要以两种方式影响器件性能:一种是载流子的能量超过Si-SiO2势垒(3.5eV),直接通过热载流子注入(Hot Carrier Injection,HCI)或通过隧穿效应进入栅氧化层,导致器件性能失效;另一种是漏极附近热载流子的运动因碰撞电离而产生电子空穴对,电子形成附加的漏电流,多数空穴则被衬底收集形成衬底电流,而部分空穴随着漏极向栅极正向电场的形成而注入栅氧化层。

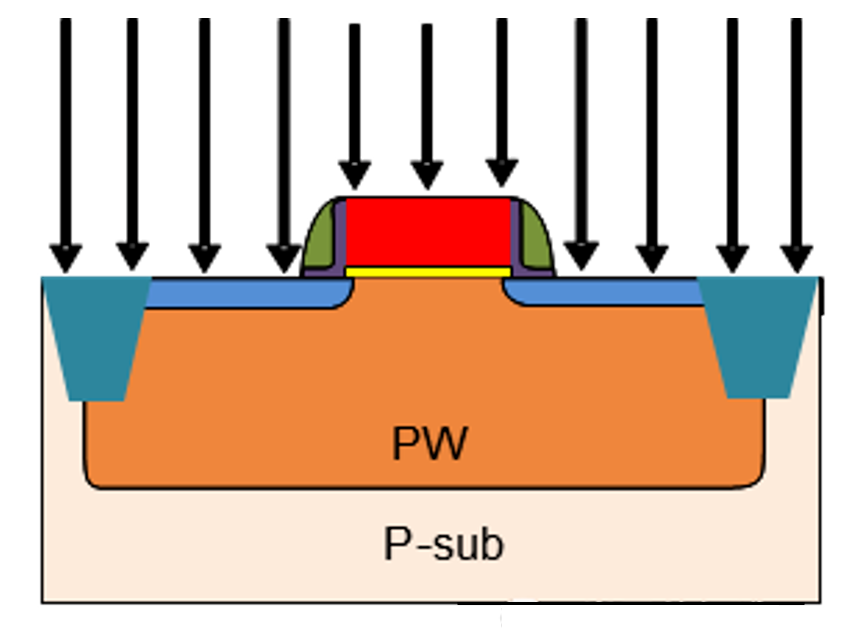

为了降低短沟道效应的影响,研究人员对传统平面器件结构进行了改良。一方面设法降低沟道电场,尤其是漏区电场;另一方面要消除PN结之间、器件之间的相互作用。因此,轻掺杂漏(Lightly Doped Drain,LDD)工艺和绝缘体上硅(Silicon on Insulator,SOI)技术工艺应运而生。SOI的一个优点是减少源漏区与体硅之间的寄生电容,从而使器件有较高的速度;另一个优点是有较低的漏电流,具有低功耗特性。然而,SOI技术也存在成本较高、制造难度大、散热和工艺兼容性等问题。相比之下,LDD工艺因其简单有效而得到了广泛应用。

三、LDD工艺与DDD工艺

-

DDD工艺的优缺点

-

LDD工艺的优缺点

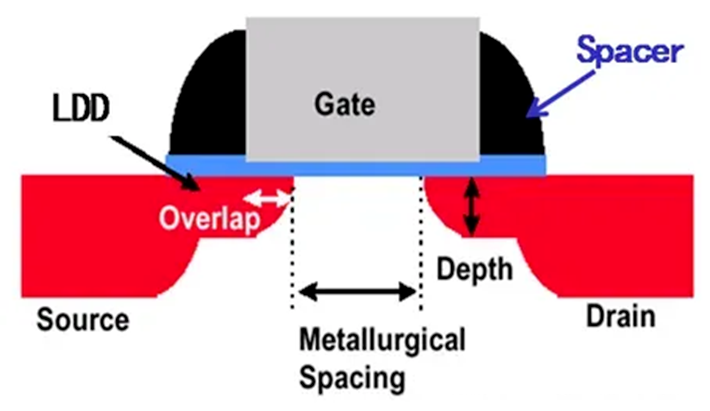

为了改善DDD工艺的问题,研发人员开发出轻掺杂漏(LDD)工艺。与DDD工艺不同的是,LDD的结深很浅,它不需要利用热退火进行扩散,而是利用侧墙(Spacer)工艺。在侧墙形成之前增加一道轻掺杂的离子注入工艺,侧墙形成后依然进行源漏重掺杂离子注入工艺。这样,漏极与沟道之间会形成一定宽度的轻掺杂区域,从而降低漏极附近峰值电场强度,达到削弱热载流子效应的目的。

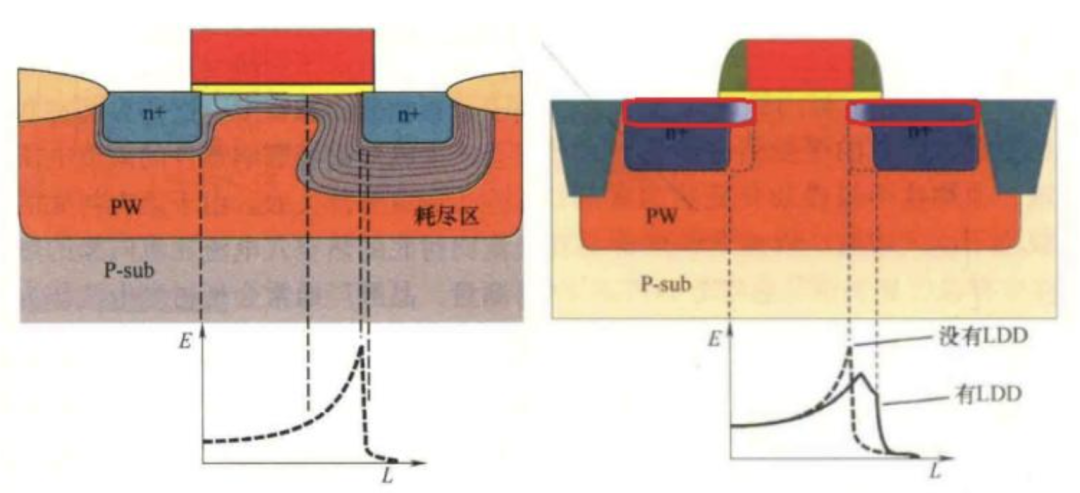

当器件工作在饱和区时,轻掺杂的LDD与P阱形成耗尽区。耗尽区从LDD与P阱的交界向沟道方向延伸的同时也会向LDD内部延伸,并到达重掺杂的漏极有源区。这时,漏区内部会形成很小的耗尽区。LDD结构作为漏有源区与沟道之间的衔接区,使电场强度出现一个缓变的过程,削弱了最强电场强度的峰值,并使电场强度重新分布,其峰值出现在LDD结构内部。这样可以有效地改善热载流子注入效应。而没有LDD结构的NMOS从P阱到重掺杂的漏区是一个突变的过程,电场强度会突然达到最大值,没有一个缓变的过程,并且电场强度的峰值很高。

-

不同技术节点的侧墙工艺

当工艺节点减至0.18μm时,因Si3N4应力过大影响器件性能,采用ONO三明治结构(SiO2+Si3N4+SiO2)减薄Si3N4并控制应力。至90nm节点,则采用双重侧墙工艺增加栅极与LDD区宽度,控制寄生电容。 摩尔定律驱动晶体管尺寸持续缩小,漏电与寄生电容问题凸显,成为尺寸缩减的障碍。为此,引入了LDD轻掺杂与侧墙工艺,并随尺寸缩小不断改进,形成多层结构。 LDD工艺对解决短沟道效应至关重要,并将随工艺节点缩小和技术进步不断优化,以适应集成电路发展需求。

0

0