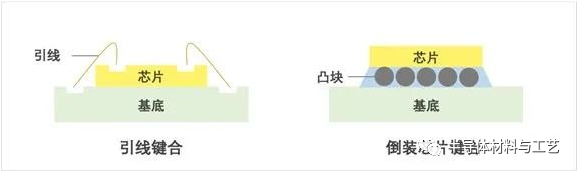

晶圆级封装(WLP)技术正在流行,它可将封装尺寸减小至IC芯片大小,并以晶片形式成批加工制作,以降低封装成本,提高电路的可靠性。晶圆级封装成本还会随芯片尺寸的减小而下降。晶圆级封装工艺是通过在芯片电路层上再次布线来实现焊点的重新分布。在重新分布的焊点上生长焊料凸点,以此实现与外围电路的互连,然后经过切割,制成倒装芯片的样式。WLP取代了高密度的引线键合,实现了真正意义上的芯片尺寸封装。

射频前端(RFFE,Radio Frequency Front-End)模组国内外手机终端中广泛应用。它将功率放大器(PA,Power Amplifier)、开关(Switch)、低噪声放大器LNA(Low Noise Amplifier)、滤波器(Filter)、无源器件等集成为一个模组,从而提高性能,并减小封装体积。然而,受限于国外专利以及设计水平等因素,国产滤波器的份额相当低。在模块集成化的趋势下,国内射频巨头在布局和生产滤波器。声学滤波器可分为声表面滤波器和体声波滤波器,其中声表面滤波器可根据适用的频率细分为SAW、TC-SAW和IHP-SAW。体声波滤波器适用于较高的频段,可细分为BAW、FBAR、XBAR等。无论是SAW(Surface Acoustic Wave filter)还是BAW(Bulk Acoustic Wave Filter),均是在晶圆级封测后以倒装芯片的工艺贴装在模组上。在晶圆级封装工艺中,Bump制造是相当重要的一道工序,因此本文将浅谈滤波器晶圆级封装(Wafer Level package)中Bump制造的关键点。

凸块是定向生长于芯片表面,与芯片焊盘直接相连或间接相连的具有金属导电特性的凸起物。凸块工艺介于产业链前道集成电路制造和后道封装测试之间,是先进封装的核心技术之一。

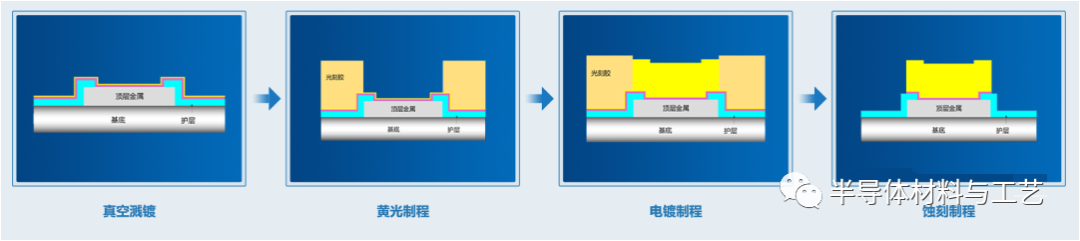

凸块制造过程一般是基于定制的光掩模,通过真空溅镀、黄光、电镀、蚀刻等环节而成,该技术是晶圆制造环节的延伸,也是实施倒装(FC)封装工艺的基础及前提。相比以引线作为键合方式传统的封装,凸块代替了原有的引线,实现了"以点代线"的突破。该技术可允许芯片拥有更高的端口密度,缩短了信号传输路径,减少了信号延迟,具备了更优良的热传导性及可靠性。此外,将晶圆重布线技术(RDL)和凸块制造技术相结合,可对原来设计的集成电路线路接点位置(I/O Pad)进行优化和调整,使集成电路能适用于不同的封装形式,封装后芯片的电性能可以明显提高。

二、凸块制造技术演变及发展历史

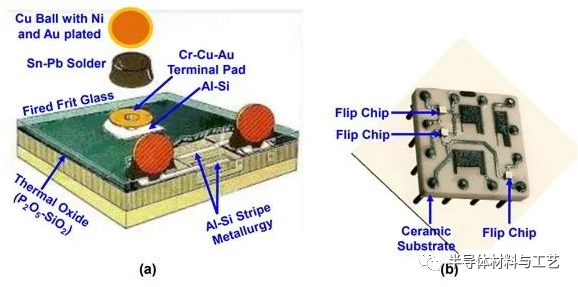

凸块制造技术起源于 IBM 在 20 世纪 60 年代开发的 C4 工艺,即"可控坍塌芯片连接技术"(Controlled Collapse Chip Connection'),该技术使用金属共熔凸点将芯片直接焊在基片的焊盘上,焊点提供了与基片的电路和物理连接,该技术是集成电路凸块制造技术的雏形,也是实现倒装封装技术的基础,但是由于在当时这种封装方式成本极高,仅被用于高端 IC 的封装,因而限制了该技术的广泛使用。

(a) IBM 的首个具有 3 个端子晶体管的倒装芯片组件;(b) IBM 首个在陶瓷基板上的倒装芯片组件(3 个芯片)

(a) IBM 的首个具有 3 个端子晶体管的倒装芯片组件;(b) IBM 首个在陶瓷基板上的倒装芯片组件(3 个芯片)C4 工艺在后续演化过程中逐渐被优化,如采用在芯片底部添加树脂的方法,增强了封装的可靠性。这种创新使得低成本的有机基板得到了发展,促进了 FC 技术在集成电路以及消费品电子器件中以较低成本使用。此外,无铅材料得到了广泛的研究及应用,凸块制造的材料种类不断扩充。

在 20 丗纪 80 年代到 21 世纪初,集成电路产业由日本转移至韩国、中国台湾,集成电路细分领域的国际分工不断深化,凸块制造技术也逐渐由蒸镀工艺转变为溅镀与电镀相结合的凸块工艺,该工艺大幅缩小了凸块间距,提高了产品良率。

近年来,随着芯片集成度的提高,细节距(Fine Pitch)和极细节距(Ultra Fine Pitch)芯片的出现,促使凸块制造技术朝向高密度、微间距方向不断发展。

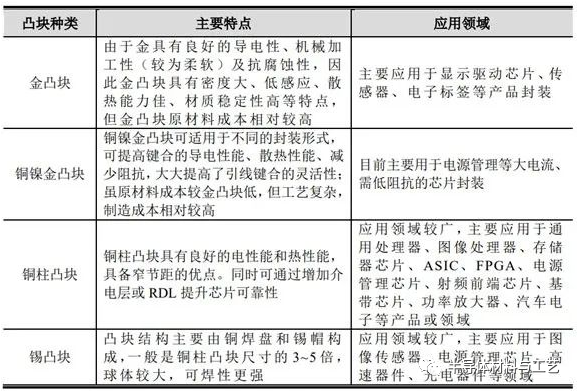

三、凸块制造的主要技术类别

凸块制造技术是诸多先进封装技术得以实现和进一步发展演化的基础,经过多年的发展,凸块制作的材质主要有金、铜、铜镍金、锡等,不同金属材质适用于不同芯片的封装,且不同凸块的特点、涉及的核心技术、上下游应用等方面差异较大,具体情况如下:

1.金凸块

金凸块,Gold Bumping,是一种利用金凸块接合替代引线键合实现芯片与 基板之间电气互联的制造技术,主要用于显示驱动芯片封装。金凸块制造技术主要用于显示驱动芯片的封装,少部分用干传感器、电子标签类产品。目前,LCD、AMOLED 等主流显示面板的驱动芯片都离不开金凸块制造工艺,后续可通过倒装工艺将芯片倒扣在玻璃基板(Glass)、柔性屏幕(Plastic)或卷带(Film)上,利用热压合或者透过导电胶材使凸块与线路上的引脚结合起来。

金凸块工艺流程

金凸块工艺流程2.铜镍金凸块

铜镍金凸块,CuNiAu Bumping,是一种可优化 I/O 设计、大幅降低了导通电阻的凸块制造技术,凸块主要由铜、镍、金三种金属组成,可在较低成本下解决传统引线键合工艺的缺点。

在集成电路封测领域,铜镍金凸块属于新兴先进封装技术,近年来发展较为迅速,是对传统引线键合(Wire bonding)封装方式的优化方案。具体而言,铜镍金凸块可以通过大幅增加芯片表面凸块的面积,在不改变芯片内部原有线路结构的基础之上,对原有芯片进行重新布线(RDL),大大提高了引线键合的灵活性。此外,铜镍金凸块中铜的占比相对较高,因而具有天然的成本优势。

电子显微镜下的铜镍金凸块结构

电子显微镜下的铜镍金凸块结构由于电源管理芯片需要具备高可靠、高电流等特性,且常常需要在高温的环境下使用,而铜镍金凸块可以满足上述要求并大幅降低导通电阻,因此铜镍金凸块目前主要应用于电源管理类芯片。

铜镍金凸块工艺流程

铜镍金凸块工艺流程3.铜柱凸块

铜柱凸块,Cu Pillar,是一种利用铜柱接合替代引线键合实现芯片与基板之间电气互联的制造技术。铜柱凸块技术是新一代芯片互连技术,后段适用于倒装(FC)的封装形式,应用十分广泛。

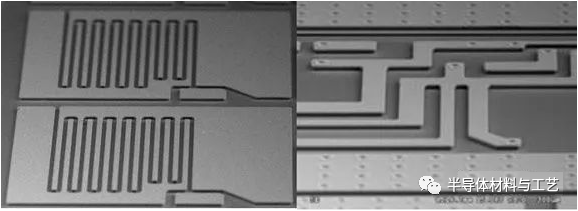

电子显微镜下的铜柱凸块结构

电子显微镜下的铜柱凸块结构铜柱凸块技术是在覆晶封装芯片的表面制作焊接凸块,以代替传统的打线封 装,可以缩短连接电路的长度、减小芯片封装体积,使其具备较佳的导电、导热和抗电子迁移能力。

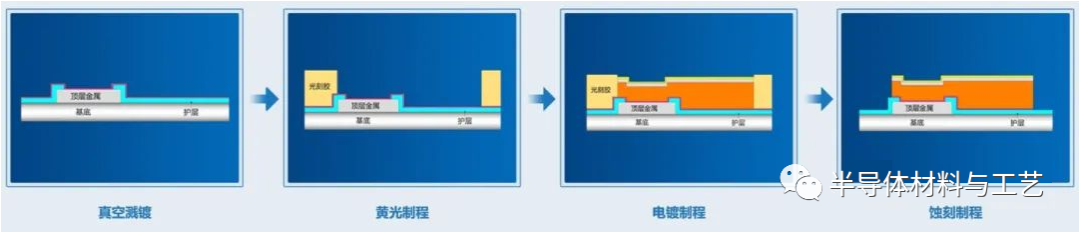

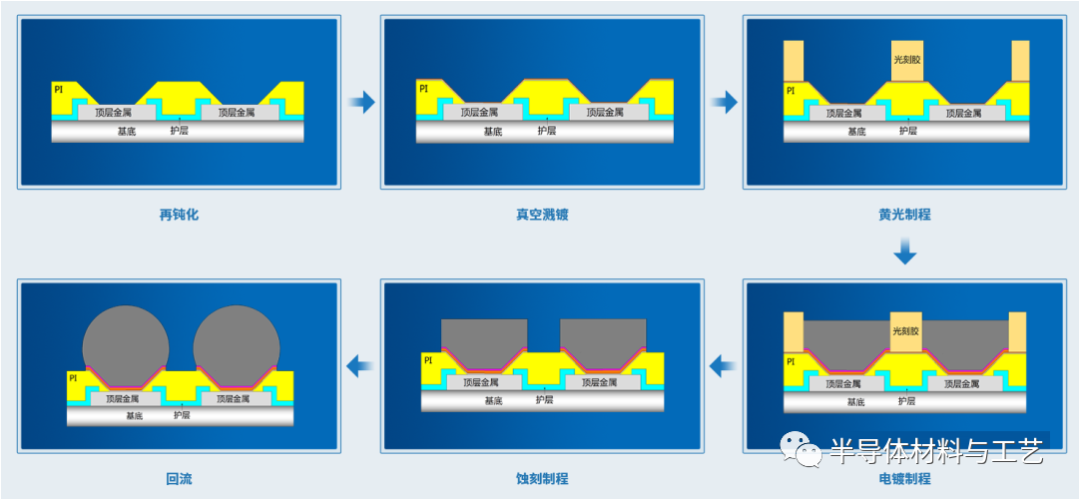

铜柱凸块制造主要步骤包括再钝化、真空溅镀、黄光、电镀、蚀刻等,具体工艺流程图如下:

铜柱凸块工艺流程

铜柱凸块工艺流程4.锡凸块

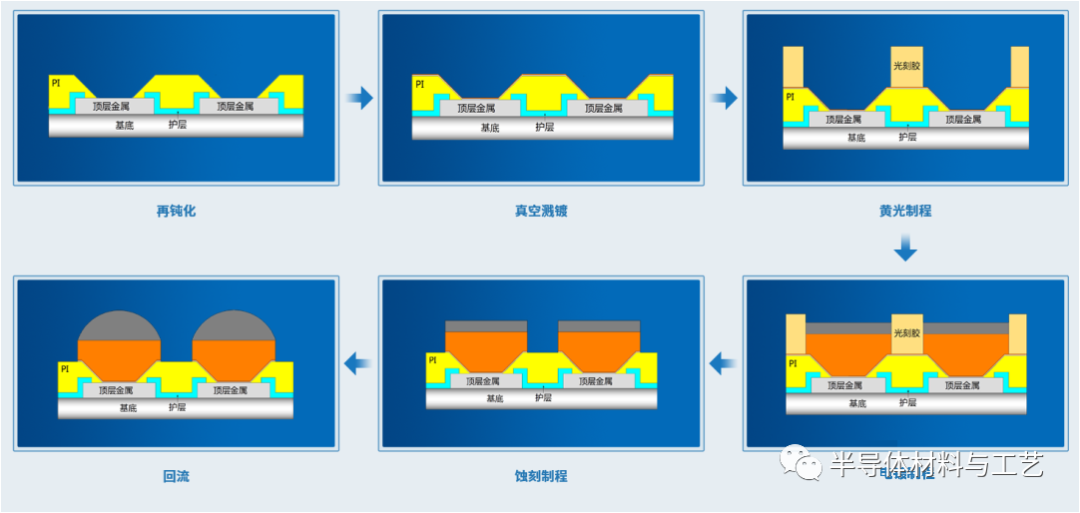

锡凸块Sn Bumping,是一种利用锡(Sn)接合替代引线键合实现芯片与基板之间电气互联的制造技术。锡凸块结构主要由铜焊盘(Cu Pad)和锡帽(SnAg Cap)构成(一般配合再钝化和 RDL 层),锡凸块一般是铜柱凸块尺寸的 3~5 倍,球体较大,可焊性更强(也可以通过电镀工艺,即电镀高锡柱并回流后形成大直径锡球),并可配合再钝化和重布线结构,主要用于 FC 制程。

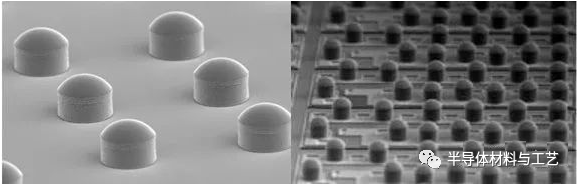

电子显微镜下的锡凸块结构

电子显微镜下的锡凸块结构锡凸块技术可以为电镀焊锡或植球焊锡,一般情况下,电镀焊锡尺寸可控制的更小。锡凸块多应用于晶圆级芯片尺寸封装,可以达到小尺寸封装,满足封装轻、薄、短、小的要求。

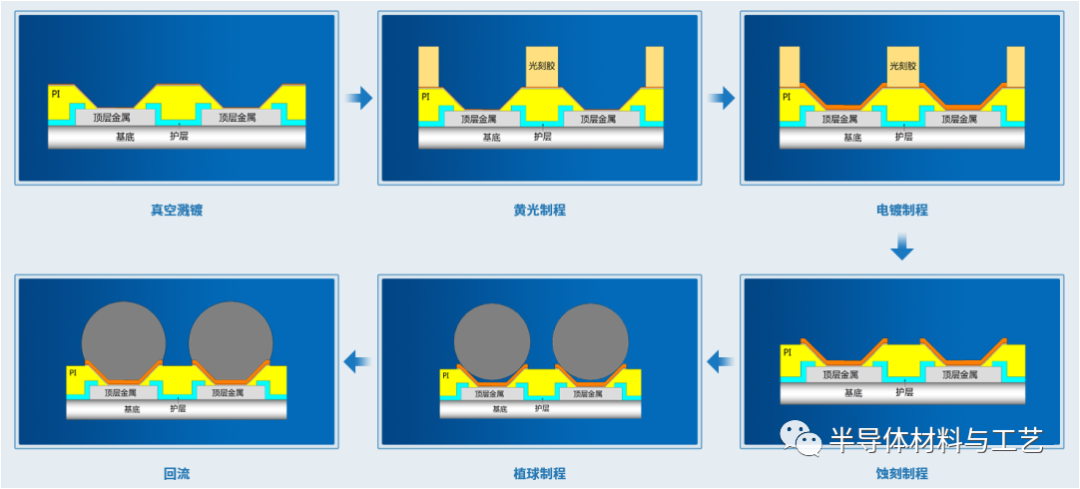

电镀焊锡凸块工艺流程

电镀焊锡凸块工艺流程 植球焊锡凸块工艺流程

植球焊锡凸块工艺流程

当前业内常见的几种SAW filter Wafer Bumping工艺如下:

1、通过打线工艺在晶圆的UBM(Under Bump Metal)上植金球。

2、通过钢网印刷工艺在UBM上印刷锡膏,再经过回流焊成球。

3、先在晶圆的UBM上印刷助焊剂,将锡球放到UBM上,再经过回流焊完成植球。

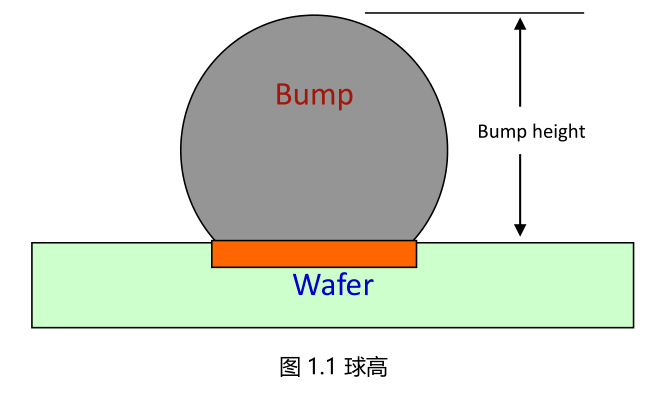

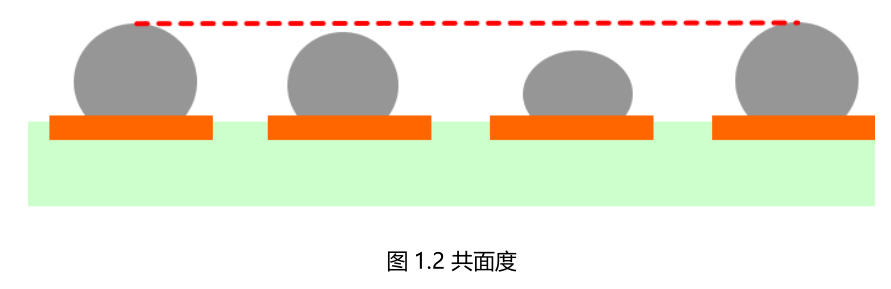

本文重点介绍第二种工艺。通过对印刷锡膏方案的剖析发现,在Bumping工艺中Bump的高度和共面度(同一颗芯片上Bump高度最大值最小值之差,差值越低越好)是最重要的关键指标(如图1.1、图1.2)。下面从钢网的工艺和设计、锡膏的特性等方面进行分析。

钢网印刷

钢网印刷的目的是使锡膏材料通过特定的图案孔沉积到正确的位置上。首先,将锡膏放到钢网上,再用刮刀使其通过钢网开孔沉积到焊盘上。钢网与晶圆之间的距离(印刷间隙)、印刷角度、压力、速度和膏体的流变特性是确保锡膏印刷的关键参数。一旦钢网开孔被膏体填满,脱模后膏体留在每个焊盘上,沉积在焊盘上的体积取决于钢网的孔距和孔壁的质量、焊盘的表面特性和膏体的流变性能。

钢网的加工工艺与开孔设计

钢网孔壁质量、尺寸一致性、定位精度和钢网生产成本是钢网生产工艺的选择标准。考虑到带有Bump的滤波器是以倒装芯片的工艺应用在前端射频模组里,其特点是Bump的尺寸小(bump高度在50~100μm之间)、间距小、对Bump高度的一致性要求高(共面度在10μm以内)。为了满足以上要求,业内最常选用的是纳米涂层钢网和电铸钢网。

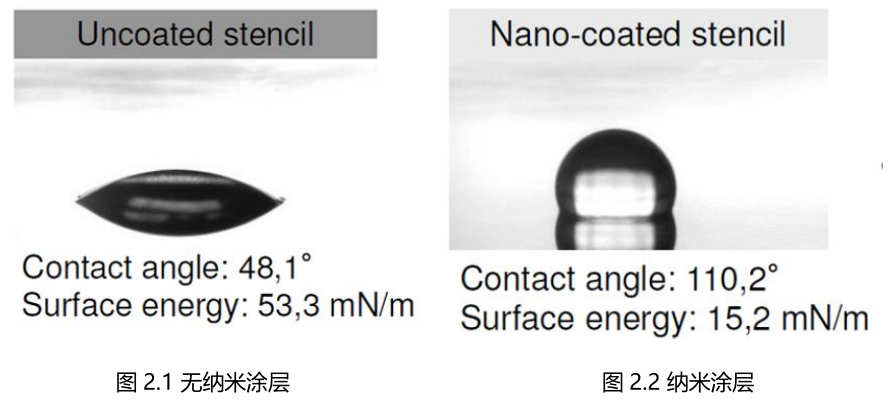

纳米涂层钢网的工艺是:在激光切割的基础上对钢网进行清洗,然后在钢网内壁进行打磨抛光以降低粗糙度,最后涂覆纳米涂层。纳米涂层使接触角显著增加,从而降低钢网材料的表面能,有利于锡膏脱模。

Source: Laser Job

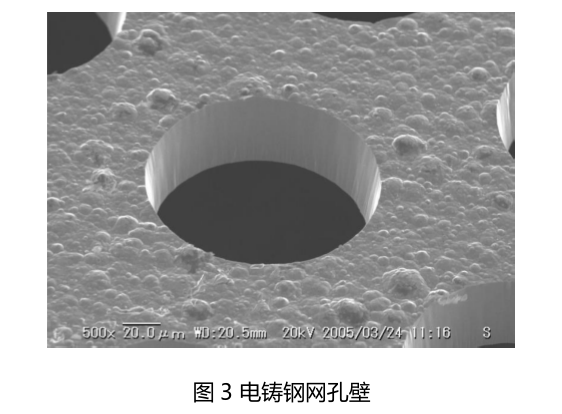

电铸钢网的制作方法是:先在导电基板上用光刻技术制备模板,然后在阻胶膜周围进行直流电铸,最后从光刻胶孔上剥离。电铸钢网的质量和印刷性能取决于光刻胶的灵敏度、所用光刻工具的类型、导电基材的光学性能和电铸工艺。电铸钢网的开孔内壁非常光滑(如图3所示),其印刷脱模的表现也最好最稳定。

Source: Bon Mark

小结,纳米涂层钢网的印刷表现略逊于电铸钢网,其涂层在批量生产一段时间后可能会脱落,但是纳米涂层钢网的价格远低于电铸钢网;电铸钢网的侧壁非常光滑,其印刷表现最好,是超细间距应用的最佳选择,但电铸钢网的价格相当昂贵。钢网的选择取决于客户对产品特性和成本的综合考量。

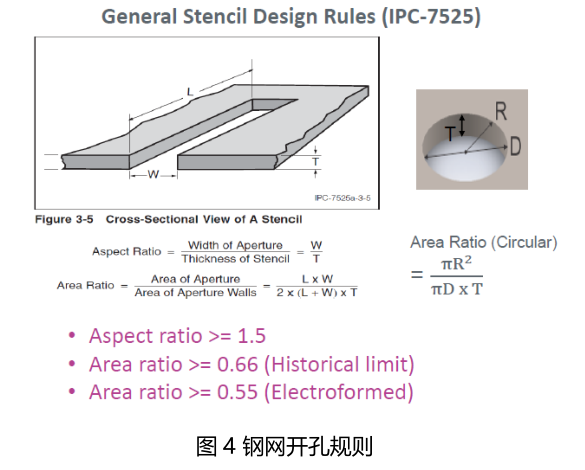

开孔面积比

由于CTE不匹配会影响封装的可靠性,符合高度要求的Bump在这方面会起到积极的作用。这就要求钢网印刷过程可靠地沉积稳定的锡膏量,以产生坚固的互连。锡膏从钢网孔的释放是由锡膏在钢网孔侧壁和晶圆焊盘之间的相互作用决定的。据文献记载,为了从钢网印刷中获得良好的膏体释放效率,模板开孔面积比[开孔面积比=开口面积/孔壁面积] 应大于0.66。该比率限制了给定孔径大小的模板厚度,并要求使用更薄的模板来印刷更细的间距。随着钢网制作工艺的提升,钢网开孔的面积比可以适当降低,如下图4所示。

锡膏

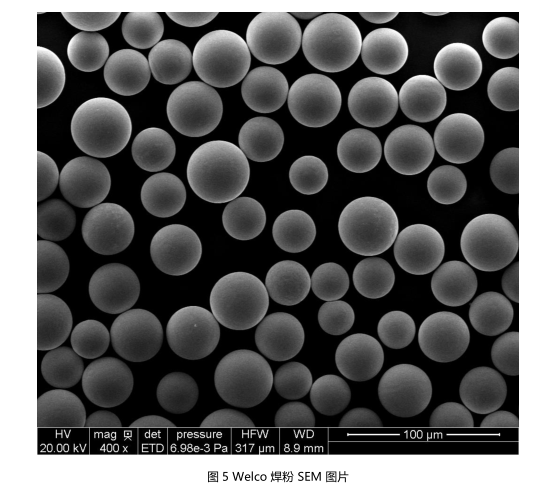

锡膏是由焊粉和助焊剂均匀混合而成的膏体,其中锡球的形状、颗粒大小、尺寸分布、氧化程度以及助焊剂载体的流变性能和配方体系,都对锡膏的印刷和回流性能起着重要作用。细间距印刷用的焊粉一直是贺利氏电子的优势,因为Welco® technology(一种在油介质中分散熔融合金的制造技术)利用两种不同介质的表面张力存在差异的原理,用工艺配方控制粉末尺寸范围,摒弃了传统的网筛工序,避免了粉末颗粒因网筛而导致的形变(表面积变大)。再者,粉末在油介质中得到充分保护,减少了粉末表面的氧化。Welco®焊粉搭配贺利氏独特的助焊剂配方体系,使印刷锡膏的转化率能够得到保证。

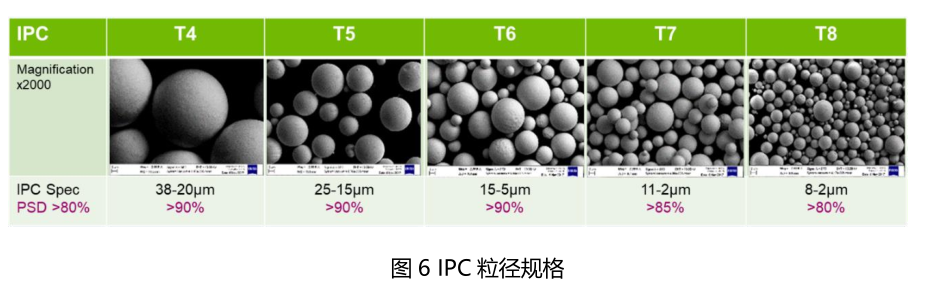

当前市场上SAW/BAW滤波器的应用中常见的Bump高度为50-100μm,结合单个芯片的layout,即相邻bump的最小间距,以及相邻芯片的bump的最小间距,6号粉和7号粉锡膏是匹配的选择。粒径的定义是基于IPC的标准(如图6),即6号粉有80%的焊粉粒径分布在5-15μm的区间。

选择合适粒径的锡膏非常重要,助焊剂体系的选择也是非常关键。因为一些SAW 的IDT 位置是裸露的,焊锡膏或助焊剂的飞溅都有可能影响IDT 的信号和声波之间的转换。对此,贺利氏开发的AP5112和AP520系列产品在开发时均在飞溅方面做了深入的研究,从而尽可能避免飞溅问题。Bump 中空洞的表现也是非常重要的质量指标,尤其是在模组中经过多次回流焊之后。

案例分享

应用:SAW filter

6 inch 钽酸锂晶圆(印刷测试以铜板代替钽酸锂晶圆)

Bump 高度=72±8μm;共面度<10μm

钢网开孔尺寸:130*140*50μm

锡膏:AP5112 SAC305 T6

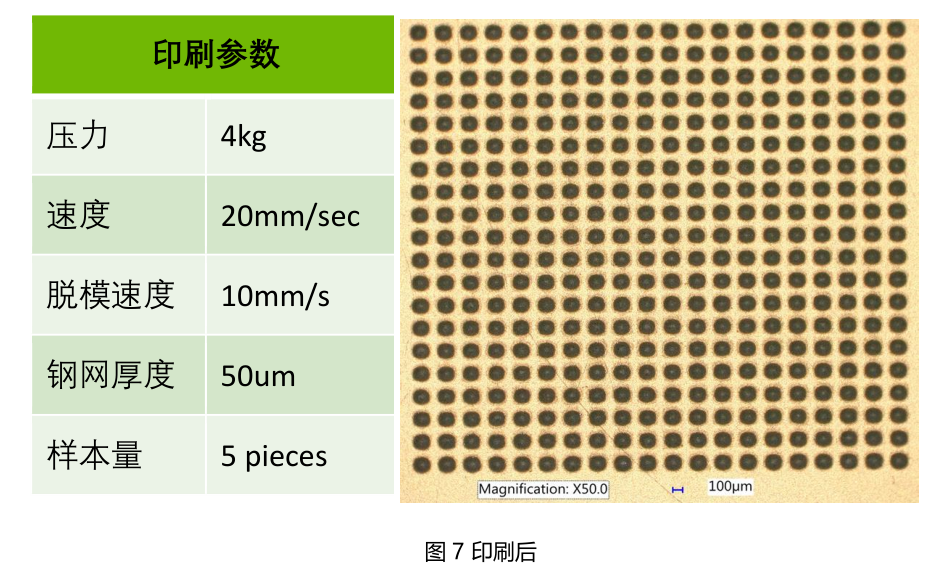

印刷稳定性是影响bump高度一致性的关键因素。印刷窗口的定义通常受印刷设备的能力、钢网的加工工艺、产品设计等因素的影响,通常通过实验验证获得。如图7所示,6号粉锡膏的连续印刷表现优异,没有发现连锡和大小点的问题。Bump的高度数据能够更好地说明。

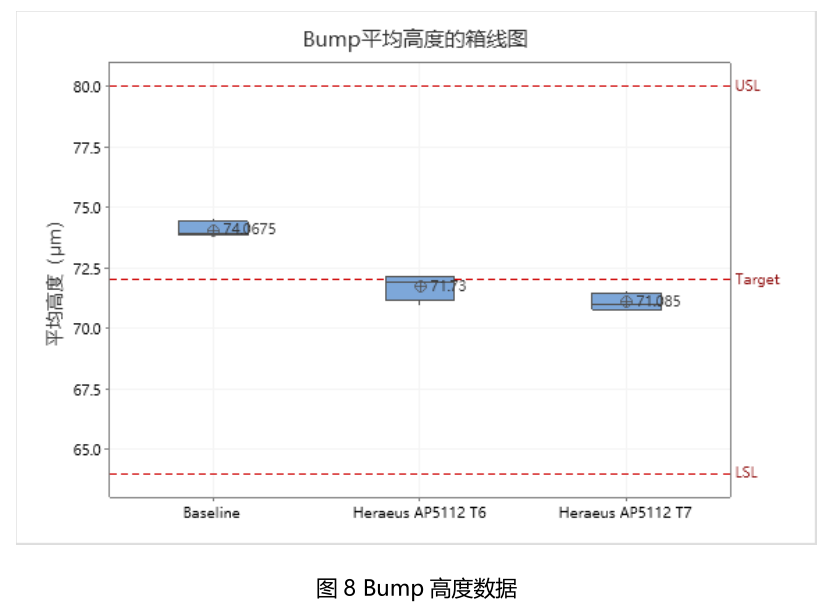

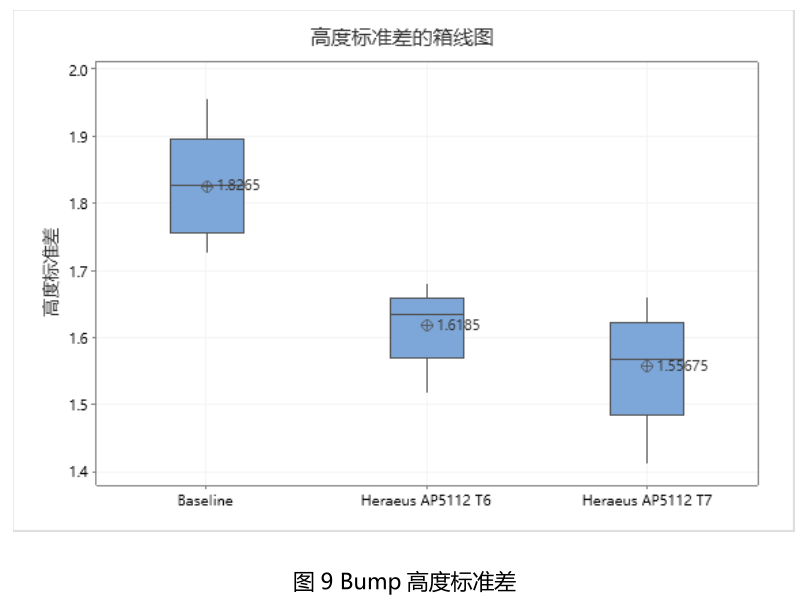

在回流焊过程中,已印刷在UBM区域的锡膏逐步熔化,助焊剂流至焊锡四周,而焊料熔化后回流到UBM上并在界面之间形成金属间化合物(Intermetallic layer),冷却后形成一定高度的Bump。Bump的平均高度非常靠近目标值,且标准差相对较小,如图8、图9所示。

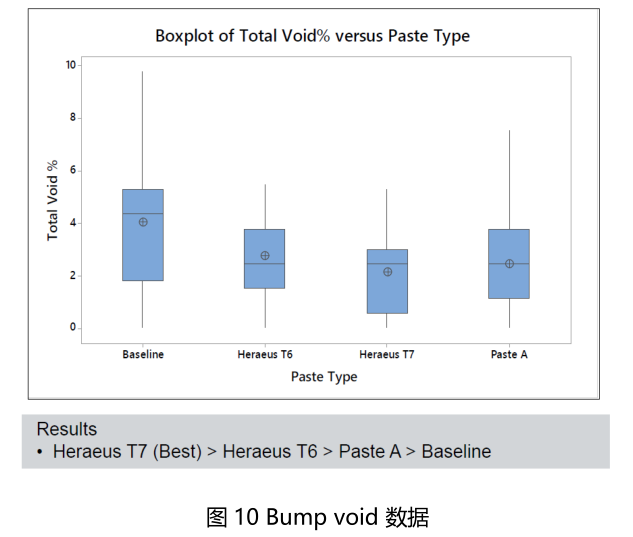

Bump 高度的指标非常关键,Bump中的空洞也至关重要。在SAW filter上面的结果显示,贺利氏的6号粉和7号粉具有良好的表现,如图10所示。

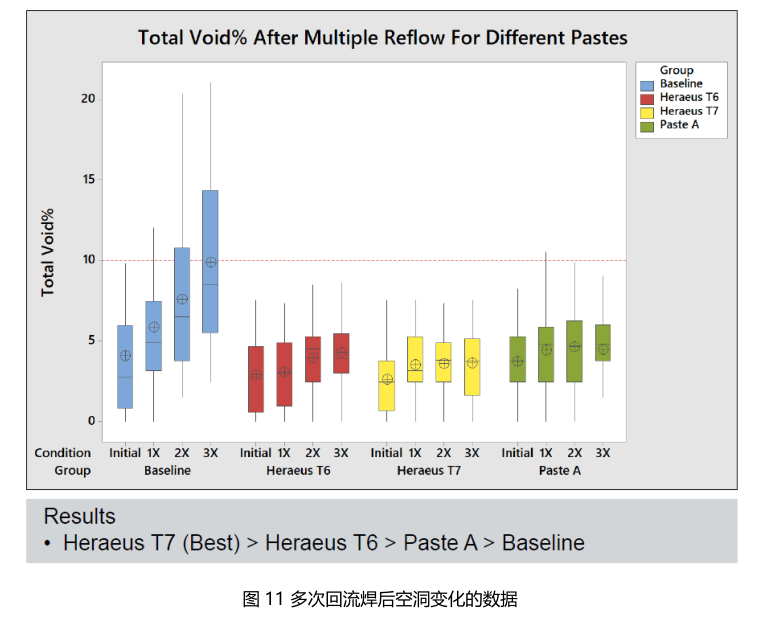

晶圆级封装最终会以芯片级应用到系统封装,即以倒装芯片的工艺集成到模组里。在此过程中会经历多次回流焊工艺,那么回流焊之后bump内部的空洞会发生怎样的变化?对此,我们测试了3次回流焊之后bump内部空洞的变化,结果如图11所示。

贺利氏的6号和7号粉锡膏对应的Bump,在经过3次回流焊之后仍然能够保持在比较好的水平。

总结,本文简单阐述了晶圆级封装的关键技术点。贺利氏Welco焊粉和独有的助焊剂配方体系能够匹配SAW、BAW 等滤波器的晶圆封装需求。更深层次的技术细节,如Bump高度的设计和球高与锡膏量的关系,敬请期待下一篇文章。不论是晶圆级封装还是先进封装贺利氏都能提供成熟的解决方案。

BUMP植球切线操作详解

0

0