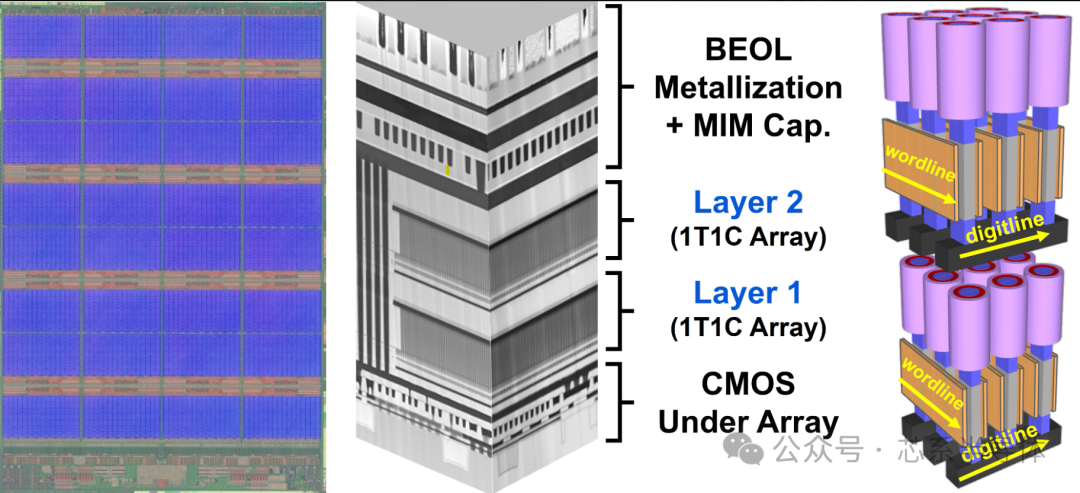

使用直接晶圆到晶圆键合来垂直堆叠芯片,可以将信号延迟降到可忽略的水平,从而实现更小、更薄的封装,同时有助于提高内存/处理器的速度并降低功耗。目前,晶圆堆叠和芯片到晶圆混合键合的实施竞争异常激烈,这被视为堆叠逻辑与内存、3D NAND,甚至可能在高带宽存储(HBM)中的多层DRAM堆叠的关键技术。垂直堆叠使得芯片制造商能够将互连间距从35µm的铜微凸点提升到10µm甚至更小。

然而,垂直堆叠也伴随着成本问题,这使得芯片制造商急于寻找减少晶圆边缘缺陷的方法。这些缺陷显著影响了晶圆上所有芯片的良率,而晶圆键合需要极为平坦、无缺陷的300mm晶圆。为了更好地控制整个晶圆加工过程中的晶圆边缘缺陷,以及在融合和混合键合过程中,工程师们正在微调新旧工艺。这些工艺包括一系列技术,涉及晶圆边缘的湿法和干法蚀刻、化学机械抛光(CMP)、边缘沉积和边缘修整步骤。

性能和功率效率的提升是显著的,先进封装正在通过芯片堆叠实现更高的处理速度和能力,将内存更接近CPU和GPU,将信息传输的线路缩短,从而加速计算。数据传输仍然占据芯片成本的很大一部分,通常需要进行几十到几百次内存访问,也许你只有两到四个周期来获取你需要的值。系统如果能将内存更靠近处理器,将大大提升性能。而且,通过垂直堆叠发送信号,相比将信号从芯片传输到外部内存再返回的长距离传输,能显著节省能量消耗。

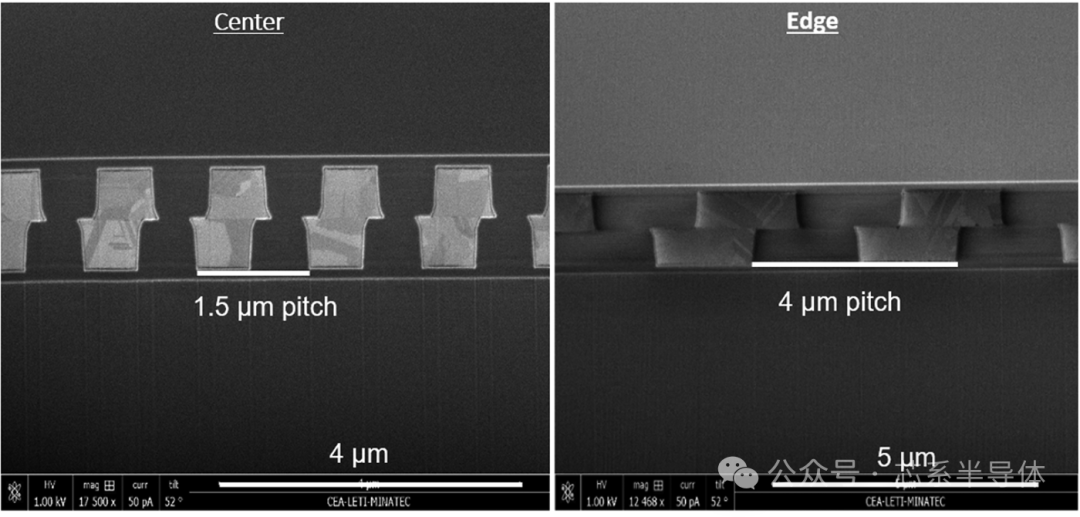

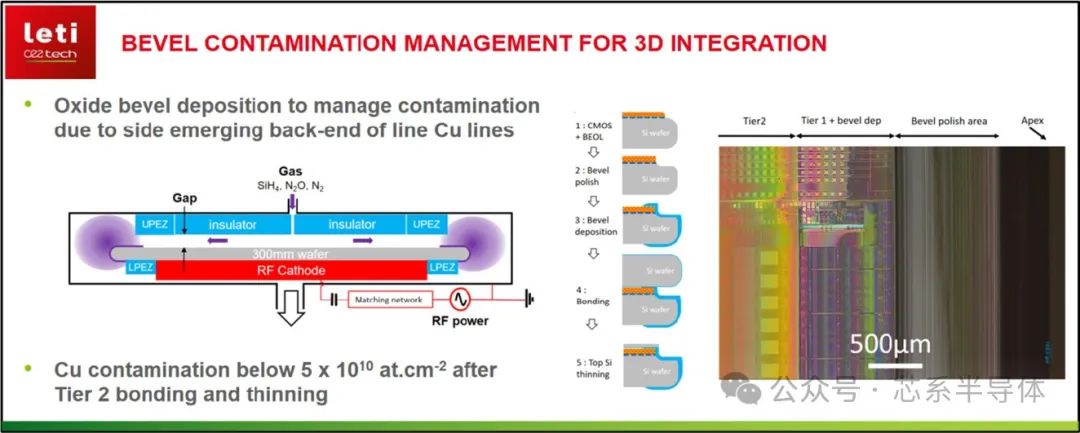

工艺也在针对先进封装的特定需求进行优化。例如,Lam Research与其合作伙伴CEA-Leti优化了一种面向先进封装应用的边缘沉积工艺,该工艺已于去年推出。在晶圆薄化之前,对键合晶圆的边缘进行沉积,可以提供增强支撑。这些结构需要材料来填补边缘的空隙,因此沉积的薄膜作为支撑层起作用。否则,在CMP过程中,由于去除速度在边缘更快,设备晶圆可能会在边缘发生开裂,导致形成缺口,这种缺口最终可能导致晶圆间隙接近零。如果没有边缘沉积,晶圆在薄化过程中可能会发生边缘开裂,严重影响良率。

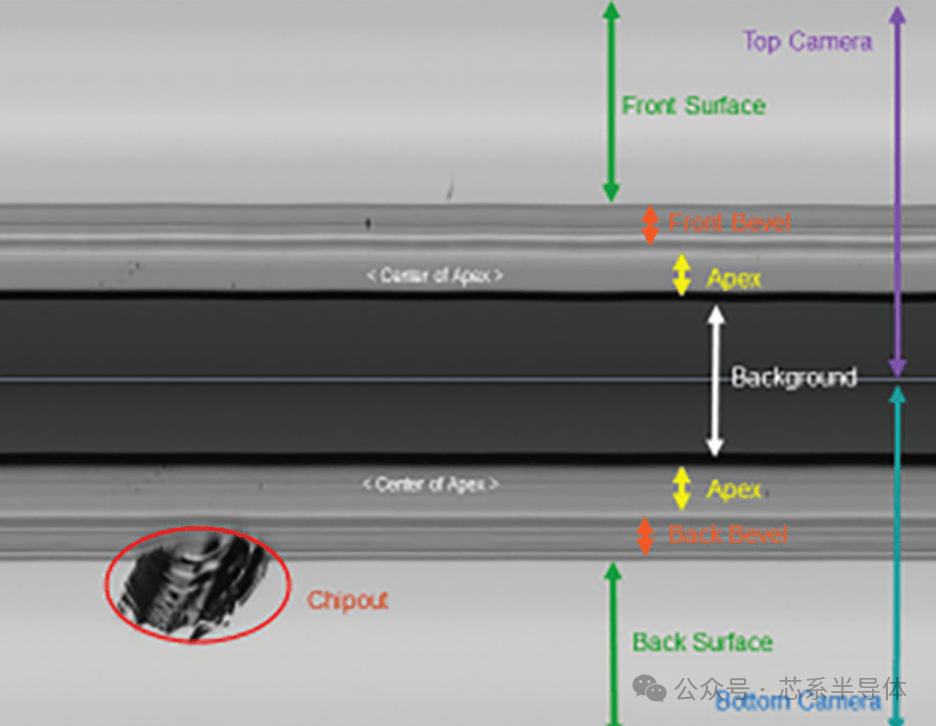

使用基于人工智能的先进工艺控制(APC)软件,工程师可以提高整个晶圆以及堆叠中晶圆之间的均匀性分析。APC涵盖等离子体限制、薄膜均匀性、光刻工艺的均匀性等方面的分析。准备进行混合键合的晶圆必须满足严格的工艺规格,以确保高良率的混合键合,例如极为平坦(<1nm的中心到边缘非均匀性)、无颗粒的晶圆、出色的晶圆/晶圆或芯片/晶圆对准、<200nm的芯片放置精度等。晶圆边缘缺陷包括颗粒、崩边、划痕、薄膜剥离、晶圆处理过程中造成的损伤,这些缺陷可能会脱落并成为影响产品良率的缺陷。

CMP挑战

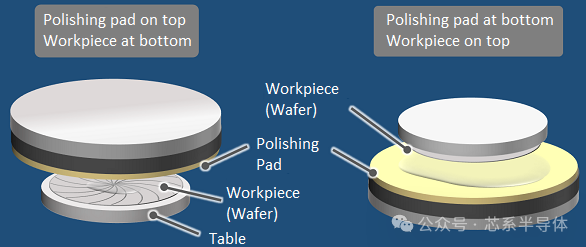

CMP(化学机械平坦化)最早由IBM在1980年代末期为引入铜大马士革互连技术而开发,它为平整化晶圆并在更薄的封装中增加更多功能提供了巨大的支持。晶圆平整度、控制边缘滚落以及减少颗粒是CMP的关键目标。如今,除了在平整化浅沟槽隔离、介电材料和BEOL互连中的铜时使用外,晶圆研磨和CMP还在优化过程中被用于在键合后显著薄化300mm硅晶圆的背面。

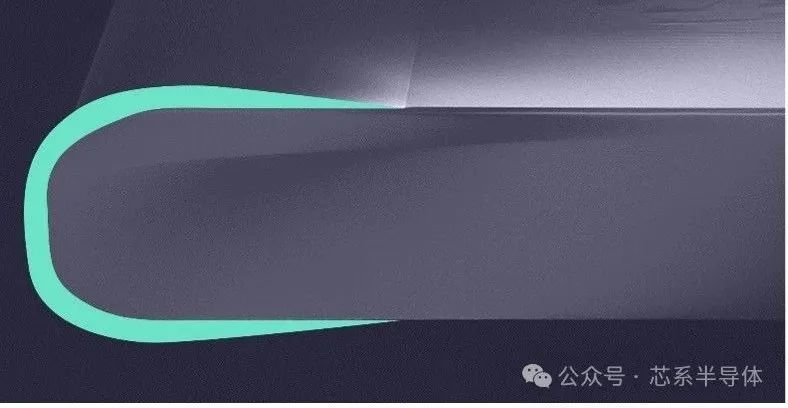

器件晶圆的质量也取决于起始硅的质量,晶圆边缘的处理一直是一个问题。因为边缘没有邻近材料,所以会发生不连续性或突变,改变了这些区域的物理特性。在裸硅晶圆的抛光过程中已经采取了一些措施来弥补这种变化,例如使用保持环。在这个CMP过程中,保持环支持晶圆在抛光夹具中,而晶圆边缘仅与保持环接触的部分非常小,裸硅晶圆边缘本质上被塑造成三个部分——一个锥形部分、更钝的边缘,再一个锥形部分,这被证明是理想的设计,有助于提高CMP性能,相比之下,圆形边缘的效果较差。

通量对所有晶圆工艺至关重要,如果CMP操作过快,就会引入非均匀性,并且有更高的机械损伤风险。因此,必须在最大化去除速率和保持均匀性、缺陷控制之间找到一个非常微妙的平衡。CMP设备供应商,如应用材料(Applied Materials)、江森自控技术(Ebara Technologies)和Axus Technology,与垫片和化学液体供应商一起,针对每个应用优化晶圆和晶圆间的均匀性,为目标工艺应用设计整个方案(化学试剂、抛光片、修整盘、P-CMP清洁剂)。

化学和机械工程师会考虑化学试剂、抛光片、修整盘的组合,控制CMP垫片的各种特性,包括刚性或硬度。颗粒的大小、分布和组成极为重要,因为这些特性部分决定了去除速率在晶圆之间的变化情况,表面图案工程和优化的抛光垫技术也被采用,同时还会使用实时传感和反馈技术,以便用户在CMP过程中及时调整并进行修正。CMP和湿法/干法蚀刻工艺都在专用设备上优化,以去除晶圆边缘的缺陷。

干法与湿法刻蚀

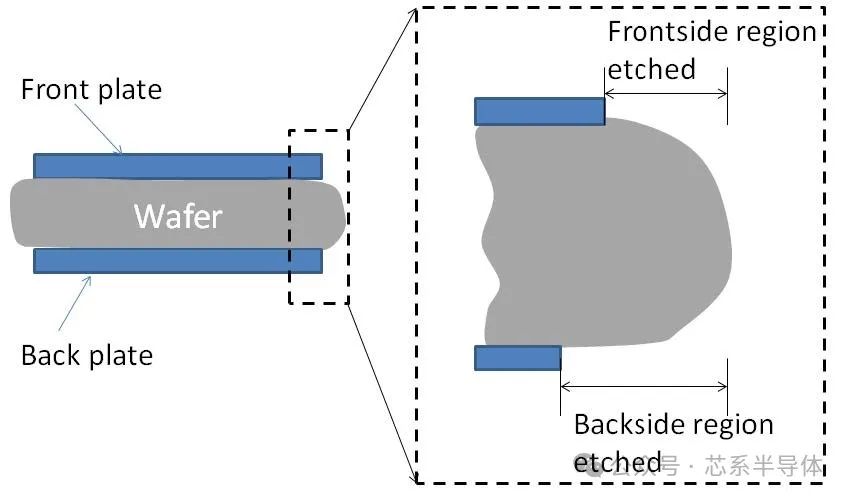

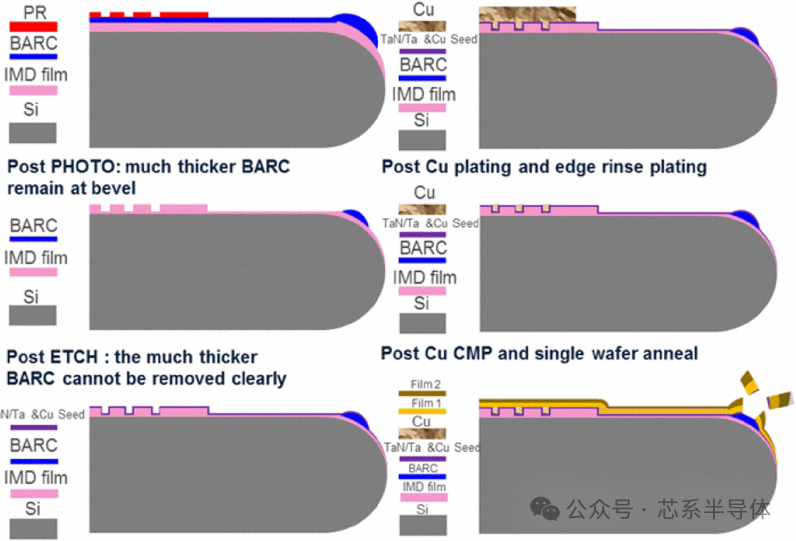

倒角刻蚀已投入生产约15年,旨在通过去除任何不需要的材料,如会损坏晶圆或从倒角移动到晶圆中心的颗粒缺陷来提高良率,需要在整个生产线上实施倒角刻蚀,因为工艺流程中有些环节会积聚这些材料。刻蚀设备经过优化,可去除晶圆边缘上的任何类型薄膜,无论是介电材料、金属还是有机物。在倒角的反应离子刻蚀(RIE)过程中,晶圆被上、下两块板固定,以确保只有晶圆的边缘、倒角部分和背面边缘暴露在外。

刻蚀过程根据客户和具体工艺流程的不同有不同的使用方式,一些客户等到积累了多层薄膜后,再清理至硅表面;而有时他们只是去除一层,比如用于深刻蚀NAND流程的厚碳硬掩模,这种碳掩模也是导电的,可能导致RIE腔室内的电弧,倒角刻蚀可以解决这些潜在的污染问题。

尽管湿法和干法清洁工艺各有其优势,但设备制造商通常会根据高产量生产选择其中一种。随着技术节点的缩小,这个问题变得更加重要,因为人们希望从晶圆边缘获得更多的良品。目前我们有一个2毫米的边缘排除要求,而客户更希望是1毫米,所以晶圆边缘的缺陷变得越来越重要。

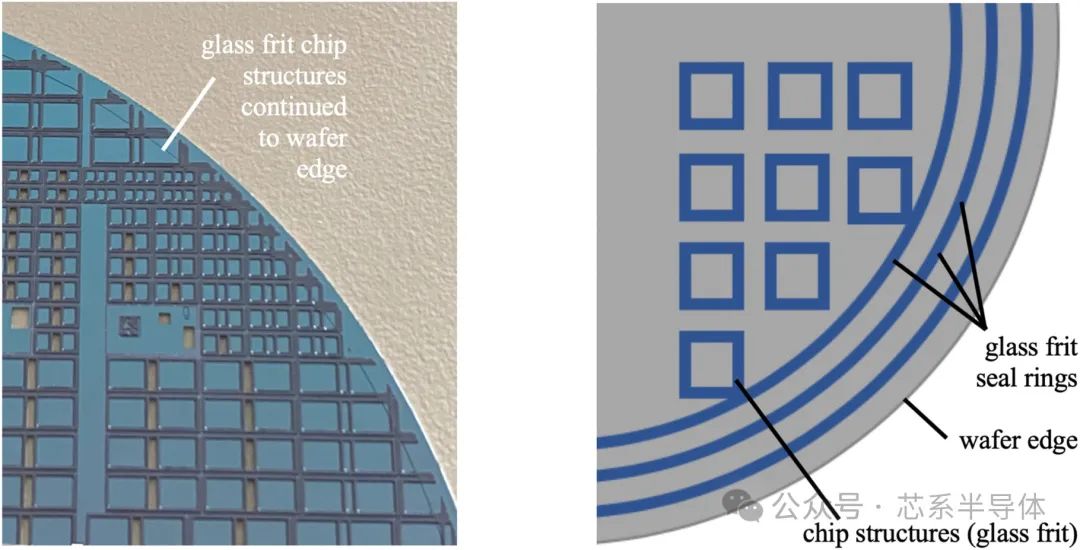

为了成功处理这些薄晶圆,在最终研磨/薄化步骤期间及之后,设备晶圆首先会与一片符合半导体行业标准的玻璃晶圆或硅载体晶圆进行键合。在键合步骤之前,这些晶圆将至少经过一步CMP处理步骤、随后的CMP后处理清洁步骤和键合过程本身。如果这些步骤不能达到关键质量要求,键合晶圆的边缘可能会出现空洞,甚至可能影响整个接合面。

例如,如果你有一层硅氮氧化物薄膜,可能会因为倒角处粘附力较弱而发生剥离。如果是像氮化钛(TiN)这样的材料,由于热应力也可能会发生剥离,因此可以用SC1清洁,而且对于去除背面聚合物也有类似的应用。经过等离子刻蚀后的薄膜,背面会有聚合物附着在边缘。CMP后也可能会有剥离现象。你需要去除这些,以防止剥离部分重新沉积在晶圆前面,造成缺陷并影响器件。

由于薄晶圆的处理和加工是一项挑战,大多数芯片制造商使用暂时键合技术,将晶圆键合到玻璃晶圆上,以便在加工过程中提供支持。对于这些非常薄的应用,尤其是当晶圆的厚度被薄化到仅为200µm时,客户使用Tyco环来固定晶圆,因为弯曲是最大的难题。

干法沉积

NAND设备是Lam公司首次开发倒角沉积的关键应用。倒角沉积系统沉积保护性的二氧化硅层,最早开始为3D NAND设备进行边缘沉积,现在它已经扩展到其他应用,其中最有趣的用途之一是支持3D封装的键合晶圆应用。沉积可以发生在正面、倒角或背面上的前几个毫米,从几百埃的厚度到几微米的材料。

另一个目前处于研发阶段的新应用是沉积薄的氮化硅薄膜,以控制铜污染。对于现有的应用,Lam公司的工程师预计每一步的良率提升将在0.2%到0.5%之间。

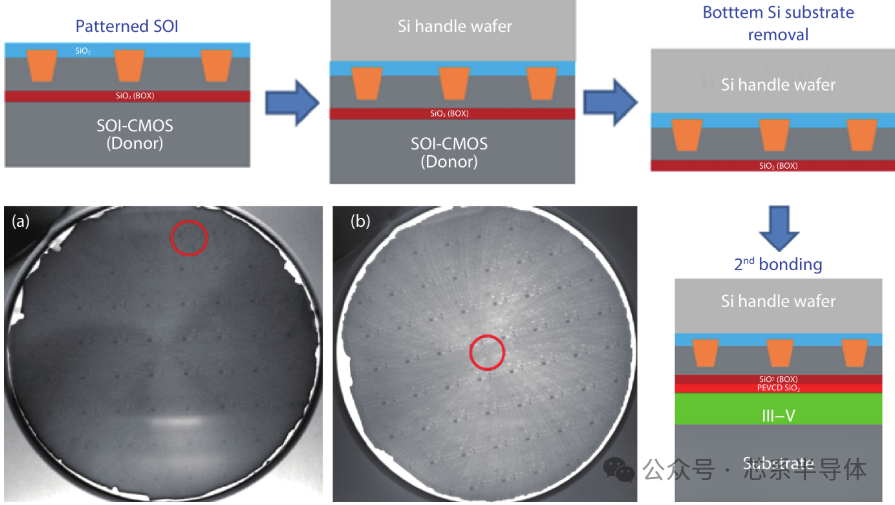

晶圆薄化与边缘修整

用于先进器件的基底硅晶圆薄化会引入显著的应力,当将其薄化时,基底硅变得越来越薄,因此会揭示出多个热应力和机械应力,表现为变形。例如,对于NAND和先进逻辑器件来说,剩下的硅几乎没有了,剩余的全是金属堆叠,而这些金属层会增加应力。

为了更好地理解去除的硅量,可以考虑原始晶圆的厚度。对于300毫米硅晶圆,原始厚度为775微米,经过所有器件加工后,薄化至35到50微米。尤其是当你开始考虑‘内存计算’的概念时,你将逻辑芯片直接堆叠在非常高性能、高带宽的内存之上,这样就涉及到完全不同的器件和完全不同的力和应力,这些应力存在于两者之间。

边缘修整过程是一种湿法工艺,可以去除晶圆外缘的1到1.5毫米,可以在预粘接或粘接步骤时进行。但假设你正在进行融合粘接,每个晶圆都有CMP滚落,然后基本上就是倒角。所以如果你将它们粘接在一起,始终会有一个区域没有完全填充。基本上会有一个非常非常小的间隙,慢慢地变为零。如果你现在开始研磨它,那个区域会变得非常脆弱,因为修整过程就像用刀修边。因此,如何控制这个边缘并管理它,目前是一个热门话题。

在芯片到晶圆的粘接中,芯片边缘的凸点非常容易受到应力的影响。如果设计人员无法改变应力分布,就必须调整设计规则,将I/O引脚移到芯片的中心。在晶圆到晶圆的粘接中,比如用于HBM时,晶圆边缘的凸点最容易受到应力影响。你会发现边缘有倒角,这很难控制,而且可能会有应力放大的边缘损伤。人们正在寻找不同的方法来解决这一问题。晶圆边缘修整在晶圆到晶圆的粘接、批量硅去除和CMP之前进行。许多传统的CMP供应商提供边缘修整工艺。

结论

晶圆边缘缺陷是制造中面临的重要挑战,正在通过CMP、干湿刻蚀、边缘沉积和晶圆边缘修整等方式加以解决。尽管一些领先的器件制造商已经在生产中使用了混合粘接技术,但它仍然是一个相对不成熟且成本较高的过程。通过专门为晶圆堆叠优化这些工艺,更多行业领域将能够使用这一赋能技术。

参考文献,见详细文件

半导体芯片切割加工品质的评价方法

方素平 小森雅晴 赵宇 植山知树 广恒辉夫 梅雪松

(西安交通大学 机械制造系统国家重点实验室 日本京都大学 工学院精密工学系 ∙陕西省计量科学研究院 日本 TOWA 株式会社)

摘要:

在对日本一些著名半导体生产企业实际生产中所用的质量控制方法和企业生产规范进行认真分析的基础上,提出了一组具有代表性的主要检测项目和相应的检测方法。设计了一组芯片切割实验方案并进行了切割实验,对所提出的检测项目及要求逐项进行了检测。明确了在正常切割条件下各项指标出现不合格品可能性的大小,证明了所提出的检测项目和检测方法对于控制芯片切割品质的有效性。研究成果对于芯片切割加工品质评价方法的规范化和标准化,对于高速切割机的设计和切割工艺的制定等均具有重要的参考价值。

0 引言

随着半导体制造技术的进步,大规模集成电路的集成度越来越高,除 CPU 芯片和大规模存储器芯片等少数芯片外,在笔记本计算机、液晶显示器、数码相机、手机及各种随身携带的视频与音像制品中大量使用的 IC 芯片,其成品的外形尺寸已经变得非常小。

本文主要就采用高速切割机切割半导体芯片切割品质的评价方法进行探讨。在对国际上的现行评价方法进行充分分析之后,进行了大量的切割实验,并对实验结果进行了分析和对比,在此基础上提出了一套可以有效控制半导体芯片切割质量的实用性评价方法及其相应的评价指标。

1 芯片切割加工品质的现行评价方法

目前国际上对芯片切割加工品质的评价指标有很多,没有形成统一的标准,世界著名企业都有自

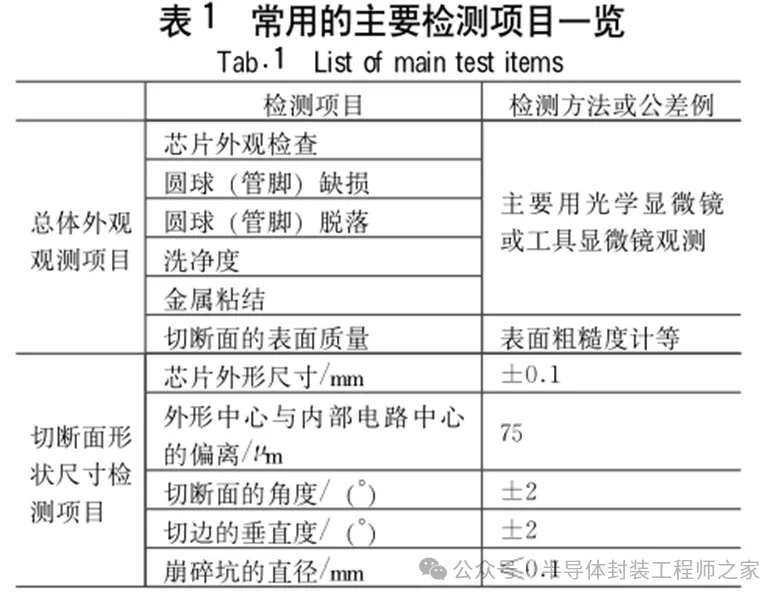

己的质量控制方法或生产规范[1-2] ,较小的企业则参考著名企业的做法制定出自己的检测项目。在这些企业自定的质量控制和评价指标中,有些项目是一致的,但具体指标值也有所不同,而有些项目则完全因企业而异。从日本几家著名半导体制造企业实施的检测项目中可以找出一些具有代表性的主要检测项目,将其列于表1中[1-2] 。按照检测方法的不同,这些主要检测项目可以分为芯片总体外观的观测项目和芯片切断面形状尺寸的检测项目两大类。

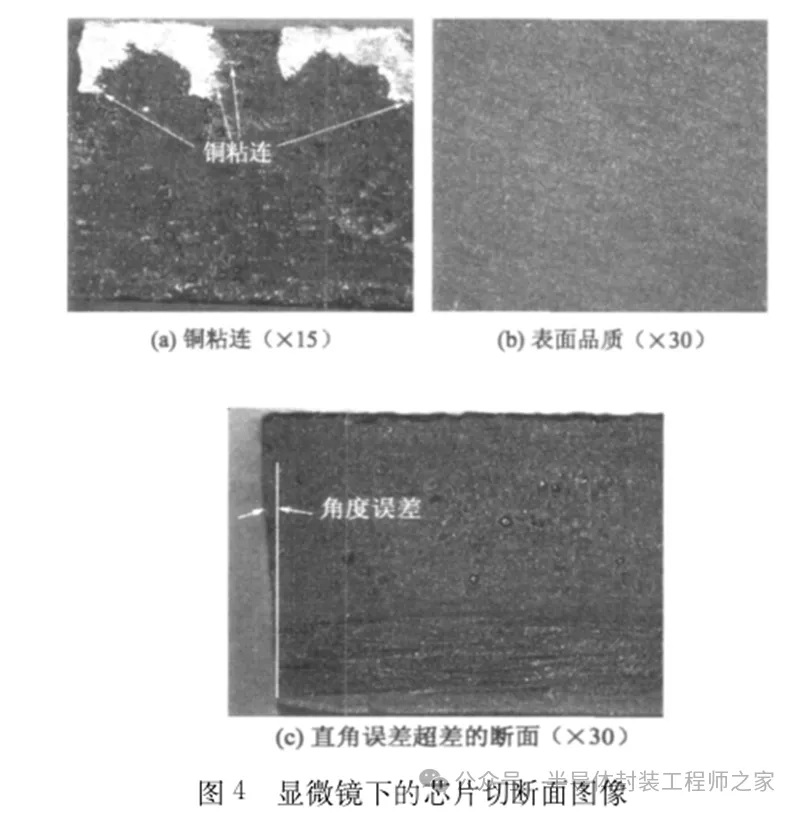

芯片总体外观的观测检查被认为是非常重要的,它可以给发生故障或出现某种问题的产品提供很多有益的信息,以帮助查明原因。对于刚切割成片的芯片,其主要检查项目有:芯片外观检查、管脚缺损、管脚脱落、芯片的洗净度、断面上的金属粘结、切断面的表面质量,等。这些项目一般采用光学显微镜或工具显微镜人为地进行观察和测量,因为现行的检查方法中大多没有规定具体的判断指标值,观察和测量的结果受人为因素的影响较大。但切断面的表面质量一般参照机械制造行业粗糙度的定义和检测方法给出较为具体的指标值,检测时也用表面粗糙度计进行精确测量。

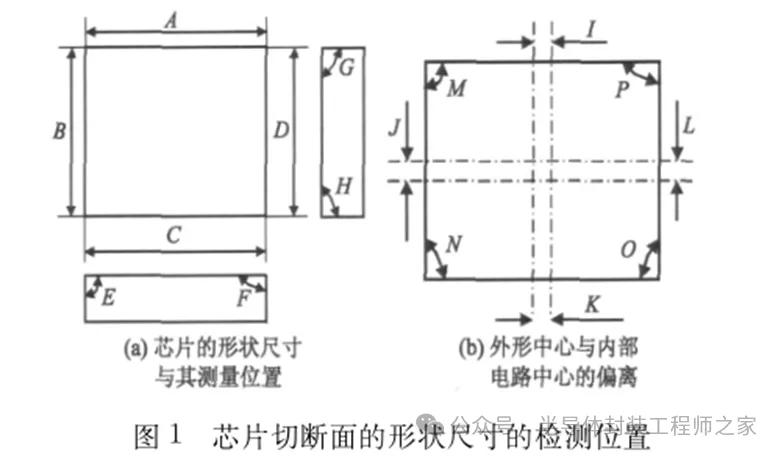

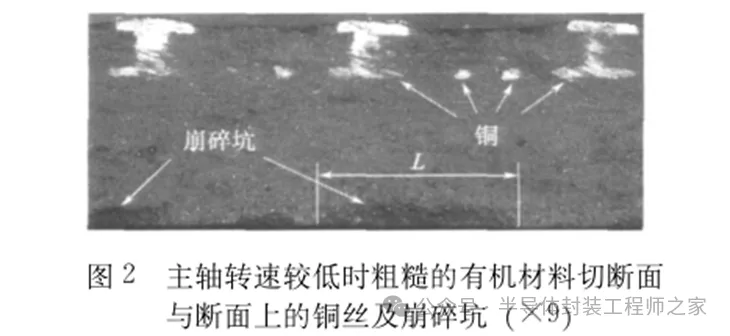

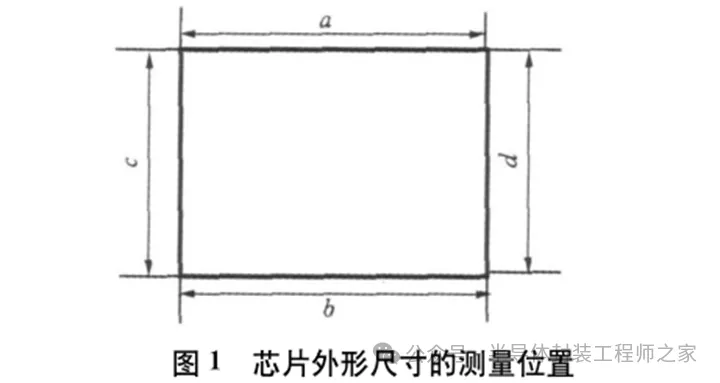

芯片切断面的形状和尺寸的检测项目主要有:芯片外形尺寸、切断面的角度、芯片外形中心与内部电路中心的偏离、切边的垂直度、崩碎坑的大小,等 (见 图 1)。其 中,芯 片 外 形 尺 寸 A、 B、C、 D 的公差一般参照机械制造行业长度量的公差给出,如±0∙1mm 等;断面的角度在每个断面上各有2个,如图1 (a) 中的 E、 F 和 G、 H;切边的垂直度指芯片正面相邻2边的垂直度误差;芯片外形中心与内部电路中心的偏离用从芯片断面到四个角上的小球中心的尺寸之差来衡量,如图1 (b)中的 I、 J、 K、L;崩碎坑系指断面上的树脂在切割过程中出现崩碎而形成的坑,目前一般仅用崩碎坑的直径 L 来衡量其大小并进行判断 (见图2)。

上述切断面的形状尺寸的检测项目多用工具显微镜来检测和观察,有条件的企业也用三坐标测量机等精度更高的检测设备来测量。

2 芯片切割实验的条件和实施方法

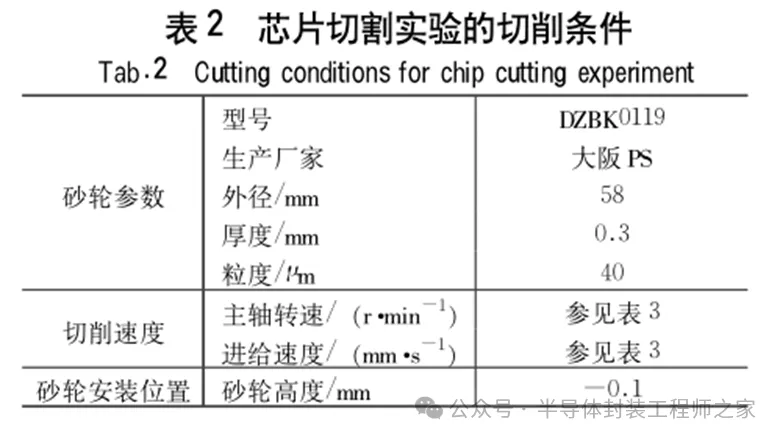

为了对芯片在不同的切割条件下的切割品质进行分析和评价,从中找出一些具有普遍意义的规律,对实用中的评价方法进行修改,提出一套适用的评价方法,设计了一组切割实验。芯片切割实验的切削条件如表2所示,所用的砂轮为一种圆型薄片砂轮,砂轮的安装位置为其外圈最低处,低于被切割基板的底边0∙1mm,以保证将被切割基板切断[3]。

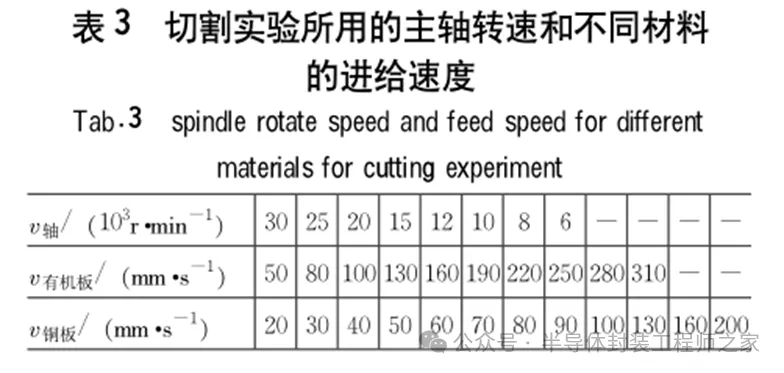

切割时所用的主轴转速 v轴 和进给速度如表3所示。由于所用切割机的最高转速为30000r/min,实验时所用的转速不能超过这个值。常见的芯片基板有有机材料基板和铜板基板两种,对于有机材料基板,其进给速度 v有机板可以高一些,目前生产中常用50~80mm/s,实验时最高 做 到 了310mm/s;对于铜板材料基板,其进给速度 v铜板 要低一些,生 产 中 常 用20~30mm/s,实 验 时 最 高 做 到 了200mm/s。将表3中的主轴转速和进给速度进行排列组合,分别进行切割实验,并对切割完的芯片逐项进行检测和分析。

3 芯片切割实验的结果及其分析

3∙1 芯片总体外观的观测结果

在工具显微镜下对上述实验中切割出来的各种不同芯片进行观测,得到的结果如下:

3∙1∙1 芯片外观检查

外观检查的项目主要有:芯片有无破损、有无发生变色、有无出现剥离、有无裂纹及其大小等。检查结果表明,在正常的切割条件下,出现上述明显缺陷的可能性极小。但对于重要的芯片,应该特别注意裂纹的检查,因为裂纹比较难以发现而常常出现遗漏,而裂纹中容易渗入湿气和其他杂质,是导致芯片出现故障的重要原因。国外常用荧光液渗透法来查微小的裂纹,效果比较好[1] 。

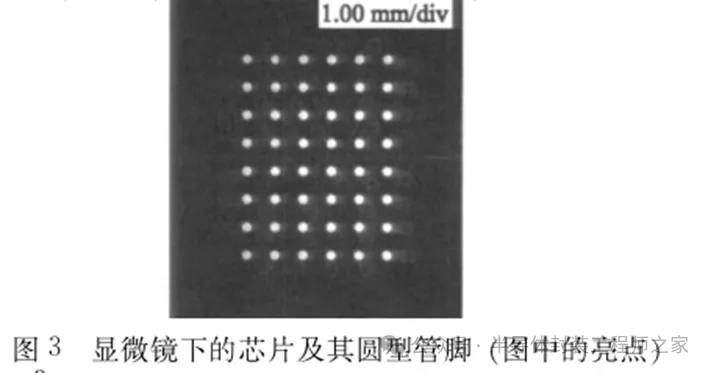

3∙1∙2 管脚缺损或脱落

这类芯片的管脚以小圆球形居多,如图3所示。检查结果表明,没有发现管脚脱落或较为明显的缺损,发现个别芯片上的管脚有少许轻微的机械性损伤,认为是由其他原因所致而非由切割所引起。说明正常切割情况下由切割致伤管脚的可能性极小。

3∙1∙3 洗净度

洗净度主要检查以下项目:高速切断时所产生的树脂粉末、水分、油脂成分及其他残渣异物有无附着在管脚等处,因为这些绝缘性材料如果附着在管脚等处,将直接影响到芯片的正常工作。检查结果表明,在正常洗净工艺下几乎没有发现明显的上述附着物,说明切割本身并不会导致更难洗净,但如果在切割时采用胶带纸来粘贴固定芯片,则应特别注意胶带纸的残留。

3∙1∙4 金属粘结

金属粘结主要是芯片机体内的铜丝在切断过程中发生的,由于铜的韧性很好,一般都会不同程度地发生粘连,需要对断面中铜丝的粘连程度进行检查。由于粘连情况的复杂性,目前也没能像机械制造行业那样给出具体的数字来进行判断,检查时仍有赖于人的经验判断。检查结果表明,在主轴转速较高时发生粘连的程度较轻,难以看到有明显的粘连 (见图4 (a)),基本上属于正常的范围之内,但转速较低时应引起注意[3] 。

3∙1∙5 切断面的表面质量

切断面的表面质量指的是其表面粗糙度,但由于芯片的切断面不同于机械零件的表面,没有配合、接触、承受载荷等方面的要求,实际给出的粗糙度值都非常低。实验结果表明,采用高速切割法切断的芯片,其断面比较光滑 (见图4 (b)),实测的粗糙度值一般都小于有关厂家所提出的值。因此,正常切割时实际上没有必要采用粗糙度计来监测。但在主轴转速较低时,其表面粗糙度较差 (如图2所示),有可能出现不合格品[3] 。

3∙2 芯片切断面的形状和尺寸的检测结果

芯片切断面的形状和尺寸的检测也在工具显微镜上进行,检测结果如下:

3∙2∙1 芯片外形尺寸

实际切割出来的芯片有可能出现倾斜的情况。因此,检测时芯片外形的长和宽均采取在两端分别进行检测的方法,将同一芯片两端的尺寸都检测出来,如图1 (a) 中的 A 和 C 及 B 和 D。判断时不仅要对单个尺寸的检测结果进行判断,还要算出两端尺寸之差,根据差值判断是否被切成了喇叭口形等。检测结果表明,以通常的速度进行切割时,芯片的外形尺寸精度都能满足要求,但在主轴转速较低,特别是进给速度较快时,会出现少量的尺寸不合格品[4-6] 。

3∙2∙2 切边的垂直度

检测结果表明,以通常的切割速度进行切割时,芯片四边的垂直度一般均能满足要求,但在主轴转速较低,和 (或) 进给速度较快时,会出现个别不合格品。

3∙2∙3 切断面的角度

检测结果表明,用现行的切割速度,即主轴转速为30000r/min,有 机 材 料 基 板 的 进 给 速 度 为50~80mm/s,铜 板 材 料 基 板 的 进 给 速 度 为20~30mm/s进行切割时,切断面的角度误差一般均在精度要求的范围 (±2°) 之内,但随着主轴转速的降低,和 (或) 进给速度的加快,出现的不合格品数将增多 (见图4 (c)),切削速度对切断面角度误差的影响较为显著[4-6] 。

3∙2∙4 外形中心与内部电路中心的偏离

检测结果表明,此项误差相对较小,在正常切割的情况下,一般均能满足要求,说明所用的切割机具有较高的定位精度。

3∙2∙5 崩碎坑的大小

检测结果表明,用现行的切割速度进行切割时,崩碎坑 (见图2) 一般较小,除个别之外,绝大多数均能满足要求,但随着主轴转速的降低,和(或) 进给速度的加快,不合格品将显著地增加,切削速度对崩碎坑的影响很大[4-6] 。

4 结语

通过大量的芯片切割实验,并对实验中切割出来的大量芯片按所提出的评价指标和检测方法逐项进行了检测,证明所提出的检测项目和检测方法对于控制半导体芯片的切割质量是有效的和可行的。指出了在正常切割条件下切断面的直角度和崩碎坑两项指标出现不合格品的可能性较大,在主轴转速较低或进给速度较快时,这两项指标出现不合格品的可能性将进一步增大。研究成果对于半导体芯片切割加工品质的评价方法的规范化和标准化具有一定的指导意义,对于相关企业的质量控制具有一定的实用价值,对于切割机的设计和切割工艺的制定具有重要的参考价值。

主轴转速对半导体芯片切割品质的影响

方素平 小森雅晴 赵宇 植山知树 廣恒辉夫 梅雪松

西安交通大学机械制造系统国家重点实验室 京都大学 陕西省计量科学研究院,西安T OW A 株式会社

摘要:

针对目前大量使用的有机材料基板芯片和使用量相对较少的铜板基板芯片,分别设计了一组实验,并对由实验切割出来的芯片的主要评价项目逐项进行了检测,明确了主轴转速对两种芯片的外形尺寸误差、芯片的喇叭口现象、切断面的角度误差、崩碎坑的数量和大小、表面粗糙度等的影响;得出了不管是哪一种基板的芯片,出现不合格的主要是崩碎坑指标这一结论。通过分析和比较,得出了实际使用的主轴转速不宜低于15000r/min 这一对于高速切割机的设计和切割工艺的制定具有重要参考价值的结论。

0 引言

由于大规模集成电路制造技术的进步,除了CP U 芯片和大规模存储器芯片等少数芯片之外,目前在笔记本计算机、液晶显示器、薄形电视机、手机及各种随身携带的视频与音像器件中大量使用的 IC 芯片,其外形尺寸已经被做得非常小。在制造过程中,这类 IC 芯片常被整齐而又紧密地排列在一块基板上,封装时常常将这些紧密排在一起的几片至几十片甚至上百片的芯片当作一个大块,在同一模具腔内用树脂将其一起封装起来,然后将其进行纵横切割,切成一片一片的芯片[1] 。将做在基板上的芯片切成单片的芯片,这一工作目前一般采用高速切割机来完成[2] 。本文探讨了采用高速切割机切割芯片时,切割机主轴的转速对芯片的切割品质的影响,在大量的切割实验的基础上,对实验结果进行分析和对比,揭示主轴转速对半导体芯片切割品质的各项评价指标的影响规律,为半导体芯片切割工艺的制定和半导体芯片切割机的研发提供理论依据。

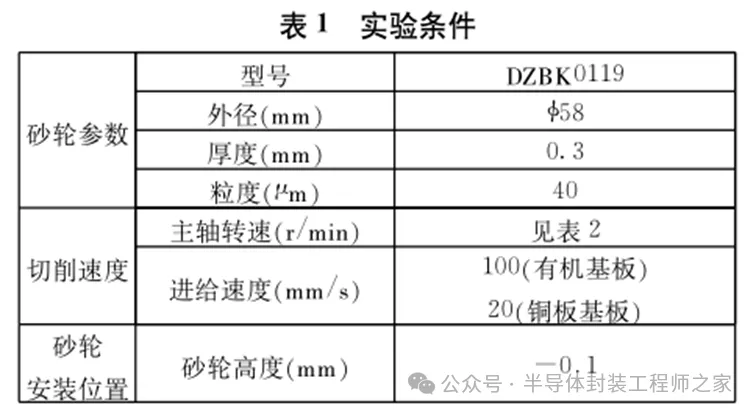

1 主轴转速对芯片切割品质影响实验

为了查明主轴转速对芯片切割品质的影响,并进一步找出其内在的规律,我们设计了一组半导体芯片的切割实验。切削条件如表1所示,所用的砂轮为一种圆型薄片砂轮,其参数见表1,砂轮的安装位置为其外圈最低处低于被切割基板的底边0∙1mm,以保证将被切割基板完全切断。切割时所采用的进给速度因被切割基板的材料的不同而不同,对于有机材料基板,其进给速度采用稍高于 目 前 生 产 中 的 实 用 速 度 ( 一 般 为 50~80mm/s) 的100mm/s;对于铜板材料基板,其进给速度则采用目前生产中常用的20mm/s。有机材料基板切割实验时采用高于目前生产中常用的进给速度的理由是,课题组在以往所进行的切割实验的结果表明,适当提高进给速度不会明显影响有机材料基板芯片的切割质量。

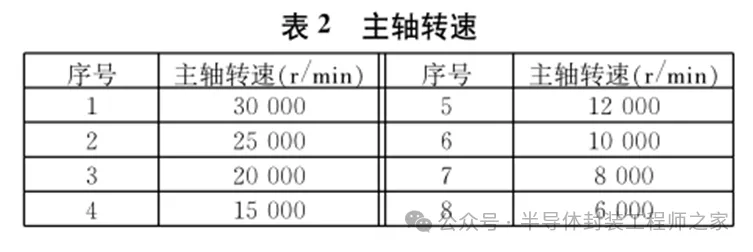

切割时所采用的主轴转速是个变数,其值如表2所示,因高速段的影响相对较小,所以实验时高速段的主轴转速间隔相对较大,而低速段的取值则较 密。由 于 所 用 的 切 割 机 的 最 高 转 速 为30000r/min,实验时所用的转速不能超过这个值。实验时因半导体基板材料的不同以表2中的主轴转速分别切割8组芯片,并对切割完的芯片逐项进行检测和分析。

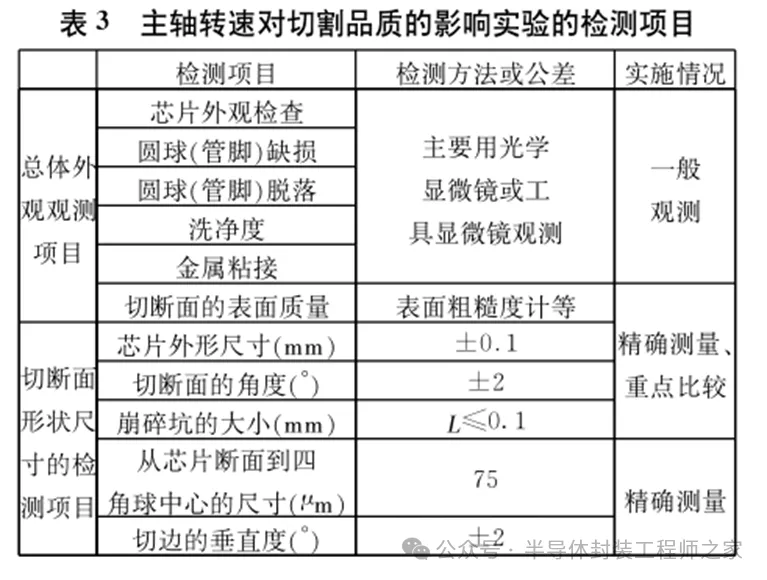

2 测试项目和评价方法

主轴转速对切割品质的影响实验的检测项目见表3。其中,芯片的总体外观观测项目中的外观检查、圆球(管脚)缺损与脱落、洗净度、金属粘结等采用工具显微镜进行观测,但因为这些项目普遍没有设定具体的数值判断指标,实际操作中受观测者的主观因素的影响较多[1],比较难以直接进行比较,本实验只把这些项目作为观察项目,而不列入重点检测与比较项目。

在芯片切断面的形状尺寸检测项目中,根据以往的实验及研究的结果[1,3,4] ,筛选出影响较为显著的几个项目,即芯片外形尺寸误差及其两端尺寸之差的值、切断面的角度误差、崩碎坑的大小,以及切断面的表面质量等为重点检测对象,对这些项目进行精确检测、重点比较和分析。而对于从芯片断面到四角球中心的尺寸,即芯片外形中心与芯片内部的电子元件部分的实际中心的偏离和切边的垂直度这两项,将对其进行精确测量,但因主轴转速的变化对这两项的影响并不显著,本实验不将其列入重点比较对象。

3 主轴转速对切割品质影响实验

3.1 主轴转速对芯片外形尺寸的影响

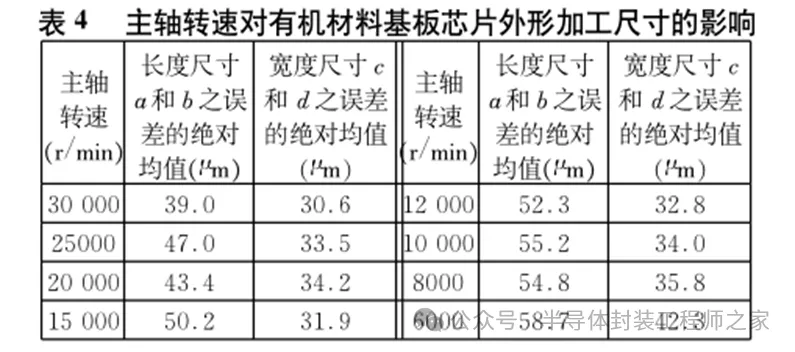

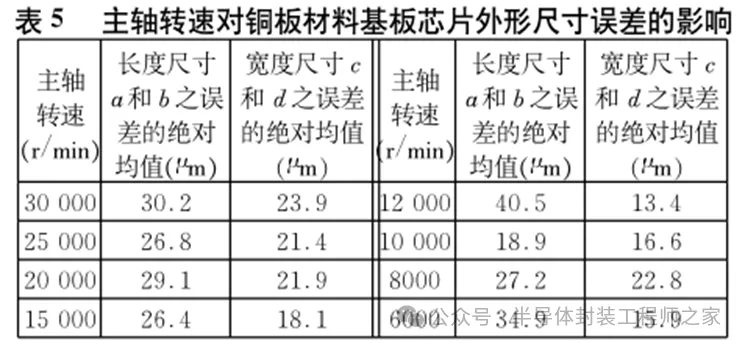

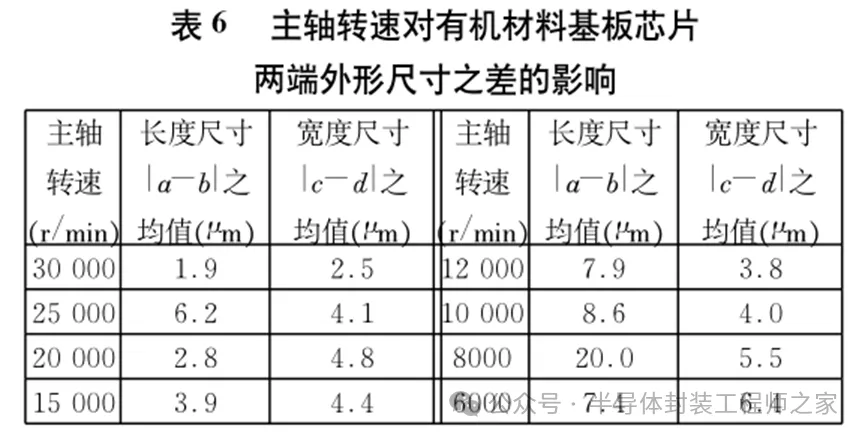

由于实际切割时有可能将芯片切成喇叭口形,因此,检测时采取对芯片的长和宽的两端均进行检测的方法,将同一芯片两端的尺寸(图1中a、b、c 和 d)都进行了检测,检测及其处理结果如表4~表6所示。

表4为以不同的主轴转速切割出来的8组有机材料基板芯片的外形尺寸误差的绝对值的平均值(绝对平均值),表中的两组数据为芯片的长和宽的尺寸误差的绝对平均值。由表4可见,随着主轴转速的降低,长和宽的尺寸误差的绝对平均值都成明显的增大趋势,说明切出来的芯片的尺寸误差随着主轴转速的降低而增大。实验结果还表明,仅仅在主轴转速为8000r/min 时查到有一个芯片的尺寸超差。

表5为8组铜板基板芯片的外形尺寸误差的绝对平均值,表中的两组数据分别为芯片的长和宽尺寸误差的绝对平均值。由表5可见,随着主轴转速的降低,长和宽的尺寸误差的绝对平均值出现不稳定的现象,实验结果未查到有尺寸不合格的芯片。

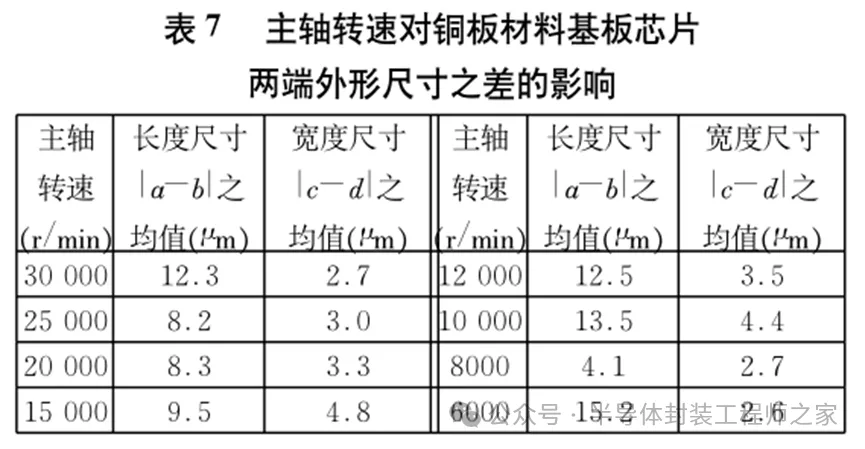

表6和表7分别为主轴转速不同时切割出来的8组有机材料基板芯片和8组铜板基板芯片两端外形尺寸之差的绝对平均值。由表6可见,随着主轴转速的降低,有机基板芯片两端外形尺寸之差的绝对平均值增大,说明芯片形状呈喇叭口的现象逐渐严重。由表7可见,主轴转速降低时铜板芯片的喇叭口现象没有有机材料基板芯片那样明显,但呈现出不稳定现象。

出现上述现象的主要原因是,主轴转速降低时每转的进给量将增大,每转切除的材料增多,切割力将增大。对于切割时进给量较大的有机材料基板芯片,切割力的增大非常显著,包括薄形砂轮、被切割基板和真空吸附工作台在内的切割系统将发生变形,明显影响到了尺寸的切割精度。而对于进给量较小的铜板基板芯片,其切割力本身较小,由每转进给量的增大而增大了的切割力仍然较小,对尺寸误差的总趋势的影响尚不明显。

实验结果表明,主轴转速在10000r/min以上时,主轴转速对有机材料基板芯片外形加工尺寸的影响均在允许范围之内,而对于铜板基板芯片,实验中所用的主轴转速均可适用,即该项目只要求主轴转速不低于10000r/min。

3.2 主轴转速对芯片切断面角度的影响

表8为主轴转速不同时切割出来的8组有机材料基板芯片和8组铜板基板芯片的切断面角度误差的平均值,以及上述各8组芯片中查出的不合格芯片的个数。从表8可以看出:对于有机材料基板芯片,随着主轴转速的降低,其切断面角度误差的平均值的绝对值呈明显增大趋势,而对于铜板基板芯片则没有有机材料基板芯片那样明显;无论是有机材料基板芯片还是铜板基板芯片,随着主轴转速的降低出现角度不合格的芯片数都将增加,但相对于铜板基板芯片,有机基板芯片的现象更为明显。

出现上述现象的主要原因是,每转进给量的增大将使切割力增大,对于进给量较大的有机材料基板芯片,增大后的切割力将使切割系统发生较为显著的变形,从而对切断面的角度精度的影响也较明显。而对于进给量较小的铜板基板芯片,增大后的切割力仍然较小,对切断面角度误差的影响尚不明显。该实验结果表明,要使切断面的角度误差全部在允许的范围之内,要求主轴转速不低于20000r/min,即使允许有少量芯片超差,其转速一般也不宜低于12000r/min。

3.3 主轴转速对芯片上的崩碎坑的影响

表9为主轴转速不同时切割出来的各组有机材料基板芯片和铜板基板芯片上出现的崩碎坑的总数,即各组中每块芯片上观察到的崩碎坑的数量之总和,以及上述各组芯片中查出的崩碎坑不合格芯片的个数。从表9可以看出:对于有机材料基板芯片,随着主轴转速的降低,其崩碎坑总数呈明显增大趋势,而对于铜板基板芯片则反而呈下降趋势;崩碎坑不合格的有机材料基板芯片始终很多,但崩碎坑不合格的铜板基板芯片则随着主轴转速的降低反而有所减少。

出现上述现象的主要原因也在于每转进给量的变化而引起的切割力的变化,其情况与前述完全相同。但至少从铜板基板芯片的实验结果中可以看出,每转的进给量并不是越小越好,可能存在着一个最佳值,这一点将在后续的实验研究中作进一步探讨。

3.4 主轴转速对芯片切断面粗糙度的影响

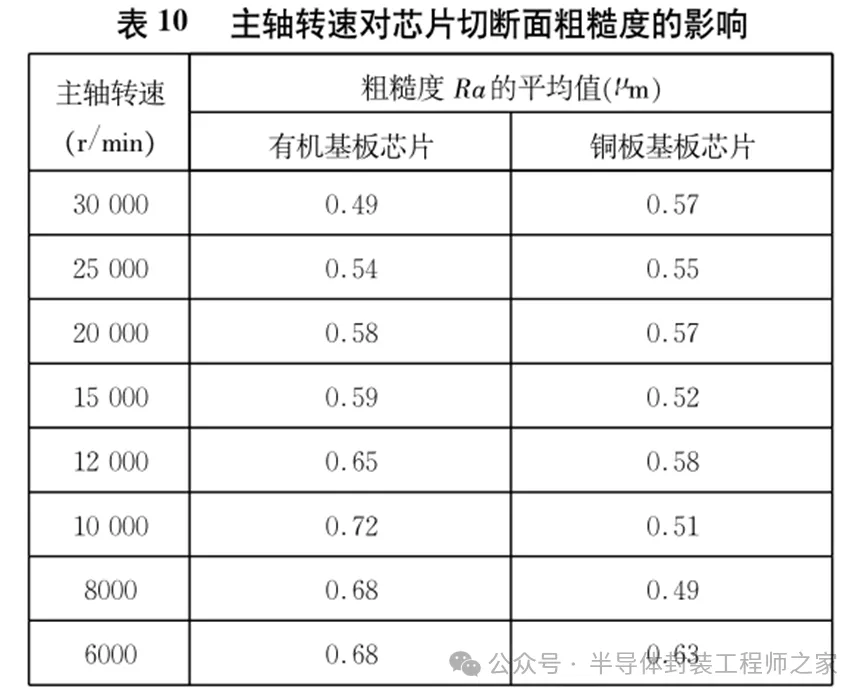

表10为主轴转速不同时切割出来的有机材料基板芯片和铜板基板芯片的切断面粗糙度 R a的平均值。由表10可见,随着主轴转速的降低,芯片切断面的粗糙度的平均值将增大,说明切断面的表面将变得更加粗糙。这一趋势对于有机材料基板芯片非常明显,而铜板基板的芯片则并不是那么明显。由于所定的粗糙度值较低,实验结果没有发现粗糙度不合格的芯片。

出现上述现象的主要原因是,每转进给量的增大使每转扫过的材料区域增多,单位面积通过的砂轮磨粒数将减少,粗糙度将增大。对于进给量较大的有机材料基板芯片,其影响较为显著,而对于进给量较小的铜板基板芯片,其影响尚不明显。

4 结论

(1)主轴转速降低时,对芯片的外形尺寸误差、芯片的喇叭口现象、切断面的角度误差、崩碎坑的数量和大小、表面粗糙度等都有不同程度的影响,且对于有机材料基板的芯片,这些影响是非常明显的,而对于铜板基板芯片,这些影响则表现出不是很明显,有出现不稳定(外形尺寸)甚至于往好的方向发展(崩碎坑)的情况。

(2)出现上述现象的主要原因是,每转进给量增大时砂轮每转扫过的材料区域增多,切割力增大,从而引起粗糙度下降,尺寸和角度的切割精度下降。但每转的进给量也并不是越小越好,可能存在着一个最佳值,这一点有待于进一步探讨。

(3)无论是有机材料基板芯片还是铜板基板芯片,出现不合格的主要是崩碎坑,且提高主轴转速也不能改善现行指标中由崩碎坑而导致的不合格率。建议在不影响半导体芯片的实际使用的情况下,适当放松崩碎坑的检测指标。

(4)在实验所用的切削条件下,主轴转速在15000r/min以上时,各项检测指标的影响都不是很明显,但转速低于这个值时,变化逐渐明显,由此可以建议,实际使用时主轴的转速不宜低于15000r/min。这一点对于相关企业制定切割工艺,或研发和设计切割机等都具有极其重要的参考价值。

0

0