八边形设计的优势:高速芯片的秘密

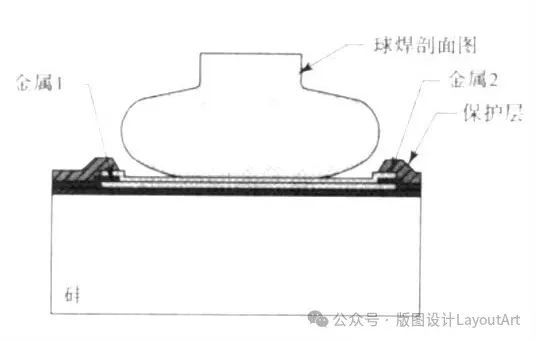

PAD,也就是焊盘,是芯片的重要组成部分。最终封装好的芯片,通过绑线把PAD与封装的PIN脚连接起来(举例是Wire Bond形式的芯片)。PAD的大小,和使用的绑线有很大关系。由于金线通过球焊的方式健合到PAD上,在压焊过程中,金线的末端的球会压变形为圆形薄饼形状,如下图。为了能够正常的打线,PAD的大小一般为绑线的2~3倍,比如绑线用1mil(25.4um,约为25um),PAD的大小为50um ~ 75um。

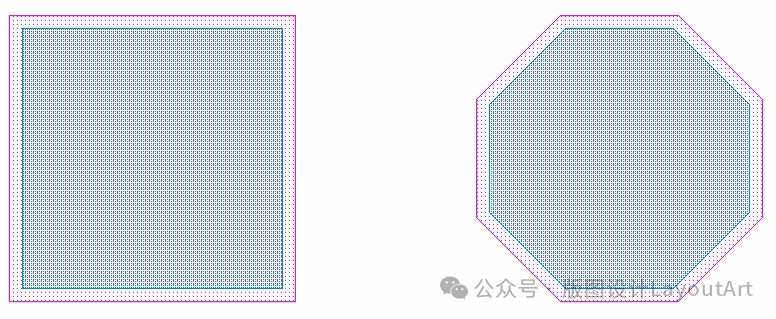

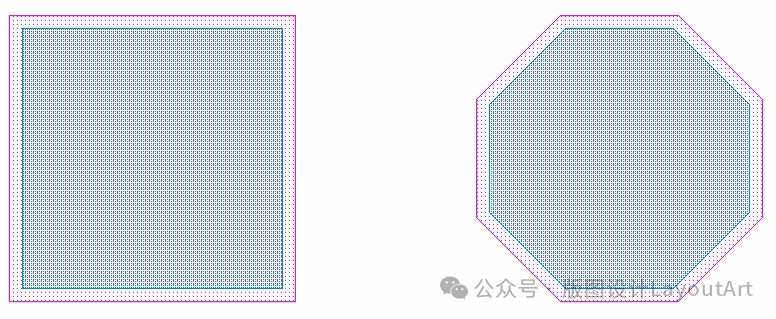

从电路设计及Layout角度看,PAD的尺寸越小越好,可以减少PAD对衬底的寄生电容,同时可以减小芯片的面积。在常见的芯片中,PAD一般设计成正方形或者长方形。为了打线时防止PAD剥落,PAD通常会用最上层金属、及次顶层金属通过VIA连接构成。对寄生没太大要求的PAD,除了最上面两层金属,还会把下面几层金属通过VIA也连上,或者只用上面两层金属,然后下面垫上几层和PAD一样大的浮空金属,可以在打线时起到缓冲作用。然而,在高速芯片设计中,多层金属结构的PAD,对衬底的寄生比较大,会影响高速性能。为此,通常只采用最顶层金属构成PAD。从可靠性角度考虑,最多采用最上面两层金属及VIA构成。在高速芯片中,经常会用到以下两种PAD,左边是正方形PAD,右边是八边形PAD。通常电源、地,低速电路用正方形PAD;高速相关的电路用八边形的PAD。

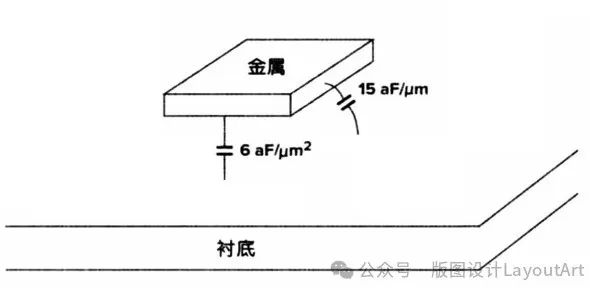

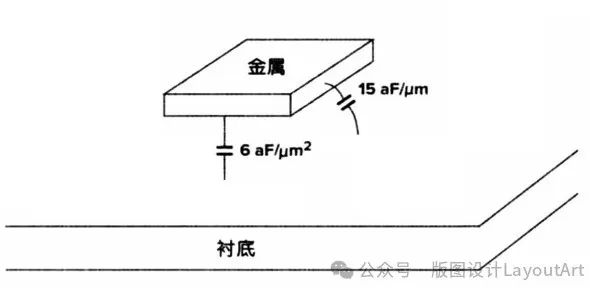

为什么连接高速电路用八边形PAD呢?根据上面PAD结构提到的,在高速芯片设计中,PAD对衬底的寄生电容,会影响高速性能。为了减少寄生,通常采用顶层金属做PAD。再根据上面PAD打线可以了解到,金线健合时会形成圆形薄饼形状。所以,为了进一步降低PAD对衬底的寄生电容,同时不影响打线,我们可以把PAD做成八边形。上面两个PAD开窗都是60um,正方形PAD的金属是66um x 66um;八边形(近似正八边形)的金属也是66um x 66um,每边大约27.3um。我们以下图寄生参数粗略计算正方形PAD、八边形PAD的寄生电容有多大。 C正方形 = 66um x 66um x 6 aF/um2 + 66um x 4 x 15 aF/um = 30.096 fFC八边形 = (27.3um x 66um/2 )/2 x 8 x 6 aF/um2 + 27.3um x 8 x 15 aF/um = 24.8976 fF从粗略计算得到的寄生电容值可知,八边形PAD的寄生电容会比正方形PAD的小17.27%。所以,高速芯片中,高速电路采用八边形的PAD,有益于高速性能。

C正方形 = 66um x 66um x 6 aF/um2 + 66um x 4 x 15 aF/um = 30.096 fFC八边形 = (27.3um x 66um/2 )/2 x 8 x 6 aF/um2 + 27.3um x 8 x 15 aF/um = 24.8976 fF从粗略计算得到的寄生电容值可知,八边形PAD的寄生电容会比正方形PAD的小17.27%。所以,高速芯片中,高速电路采用八边形的PAD,有益于高速性能。

参考资料:模拟电路版图的艺术(第二版)

声明: 本文转载自其它媒体或授权刊载,目的在于信息传递,并不代表本站赞同其观点和对其真实性负责,如有新闻稿件和图片作品的内容、版权以及其它问题的,请联系我们及时删除。(联系我们,邮箱:evan.li@aspencore.com )

-

电子工程师必看!英飞凌最新发布《高效电源转换技术白皮书》重磅揭秘:

硅基 / SiC/GaN 全技术图谱公开!一次搞懂不同场景下的最优解。

-

-

-

文介绍了三相锁相环的基本原理及其在电力系统中的应用,特别是在输入信号频率突变时的锁相效果。

-

一、LDO概述在电压转换电路中,LDO和DC-DC电路是最常用的两种方式,本篇主要介绍LDO相关内容。

-

-

图1电路在今天可能吸引力没有那么大了,因为现在有了更先进的放大器,如LTC6268,同时兼顾了低电压噪声和低输入偏置电流。但了解一下也是非常值得的,甚至在一些应用里降成本时没准可以用到,比如色谱仪。

-

下面我们通过举例介绍一个晶振的规格书参数,来和大家分享下怎么选型一个合适的晶振,以及涉及到的部分计算内容。

-

可靠性设计就是选用在最坏的使用环境下仍能保证高可靠性的元器件的过程。

-

关注回复“加群”,加入硬件电子学习交流群。本期的电路图来自ZLinear的开源数据采集板卡DL8884_RFN,是一个比较常见的电压偏置采集法(电路图已取得作者授权发文)。

-

-

-

C正方形 = 66um x 66um x 6 aF/um2 + 66um x 4 x 15 aF/um = 30.096 fFC八边形 = (27.3um x 66um/2 )/2 x 8 x 6 aF/um2 + 27.3um x 8 x 15 aF/um = 24.8976 fF从粗略计算得到的寄生电容值可知,八边形PAD的寄生电容会比正方形PAD的小17.27%。所以,高速芯片中,高速电路采用八边形的PAD,有益于高速性能。

C正方形 = 66um x 66um x 6 aF/um2 + 66um x 4 x 15 aF/um = 30.096 fFC八边形 = (27.3um x 66um/2 )/2 x 8 x 6 aF/um2 + 27.3um x 8 x 15 aF/um = 24.8976 fF从粗略计算得到的寄生电容值可知,八边形PAD的寄生电容会比正方形PAD的小17.27%。所以,高速芯片中,高速电路采用八边形的PAD,有益于高速性能。

0

0