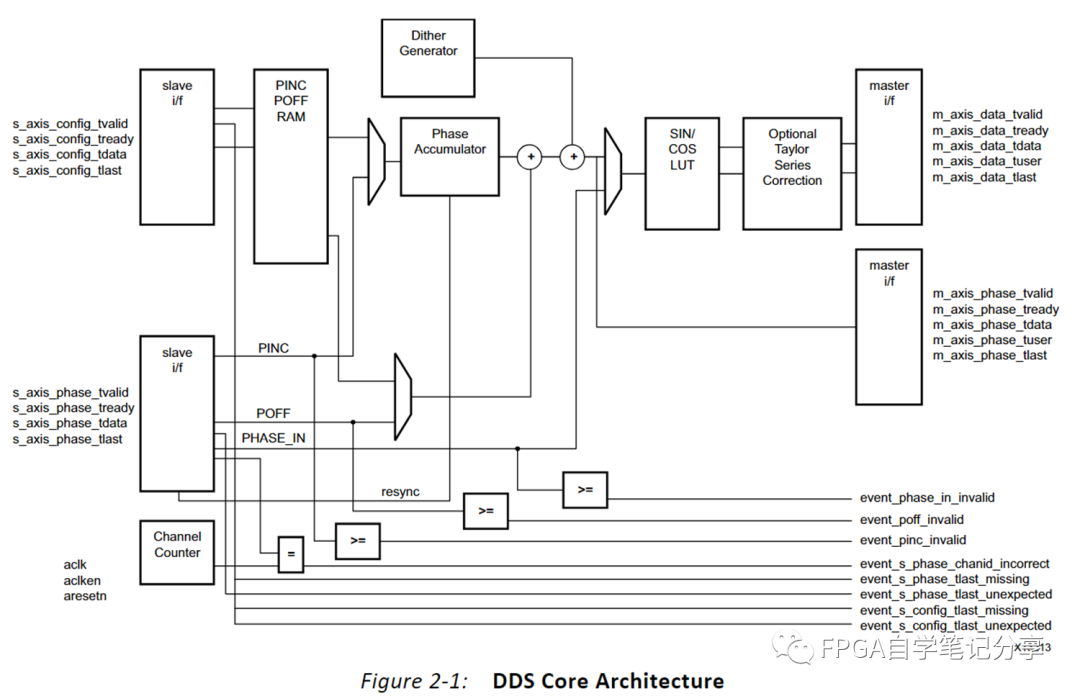

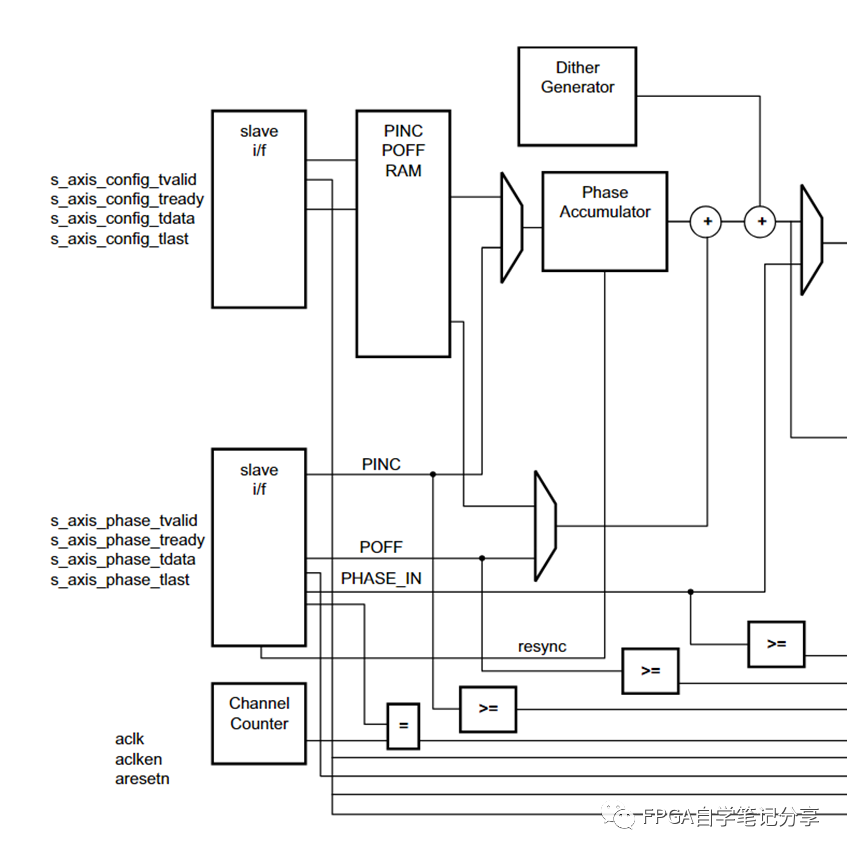

结构图如下,由两个主要部分组成,相位发生器和SIN/COS LUT,它们可以单独使用,也可以与可选的抖动发生器一起使用,以创建DDS功能。支持时分(TDM)多通道能力,具有独立配置的相位增量和偏移参数;

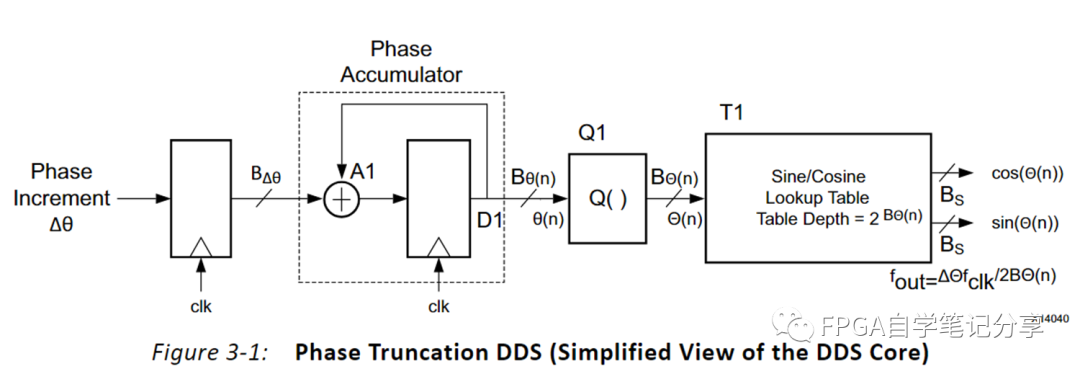

固定模式没有配置通道。当设置为可编程时,配置通道TDATA字段有一个子字段用于输入(PCIN或POFF),如果两者都被选择为可编程,则两者都有。如果PINC和POFF都没有设置为可编程,则没有配置通道。当设置为流时,输入相位通道TDATA字段有一个子字段用于所讨论的输入(PINC或POFF),如果两者都被选择为流,则两个字段都有。如果PCIN和POFF都没有设置为流,并且核心配置为具有相位发生器,则没有输入相位通道。仅配置为SIN/COS LUT时,相位发生器不被实现,PHASE_IN信号使用输入相位通道输入,并使用查找表转换为正弦和余弦输出。相位发生器与SIN/COS LUT一起使用,提供相位截断的DDS或泰勒级数校正的DDS。可以在两个块之间添加一个可选的抖动发生器,以提供相位抖动DDS。积分器(组件D1和A1)计算相位。量化器Q1只是截断,接受高精度相角,产生一个精度较低的相角,该值呈现给查找表的地址端口,查找表得到最终的SIN COS值。查找表的深度和宽度分别影响信号的相角分辨率和幅度分辨率。

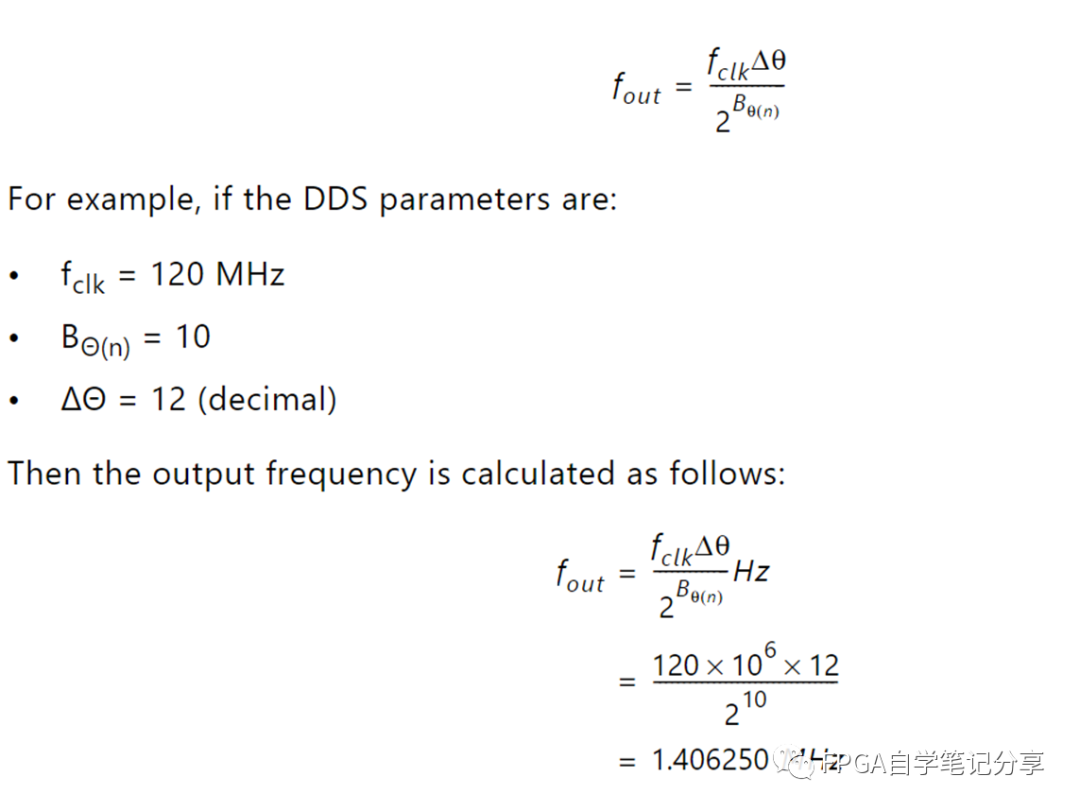

固定模式没有配置通道。当设置为可编程时,配置通道TDATA字段有一个子字段用于输入(PCIN或POFF),如果两者都被选择为可编程,则两者都有。如果PINC和POFF都没有设置为可编程,则没有配置通道。当设置为流时,输入相位通道TDATA字段有一个子字段用于所讨论的输入(PINC或POFF),如果两者都被选择为流,则两个字段都有。如果PCIN和POFF都没有设置为流,并且核心配置为具有相位发生器,则没有输入相位通道。仅配置为SIN/COS LUT时,相位发生器不被实现,PHASE_IN信号使用输入相位通道输入,并使用查找表转换为正弦和余弦输出。相位发生器与SIN/COS LUT一起使用,提供相位截断的DDS或泰勒级数校正的DDS。可以在两个块之间添加一个可选的抖动发生器,以提供相位抖动DDS。积分器(组件D1和A1)计算相位。量化器Q1只是截断,接受高精度相角,产生一个精度较低的相角,该值呈现给查找表的地址端口,查找表得到最终的SIN COS值。查找表的深度和宽度分别影响信号的相角分辨率和幅度分辨率。 标准模式输出频率的计算方式为:

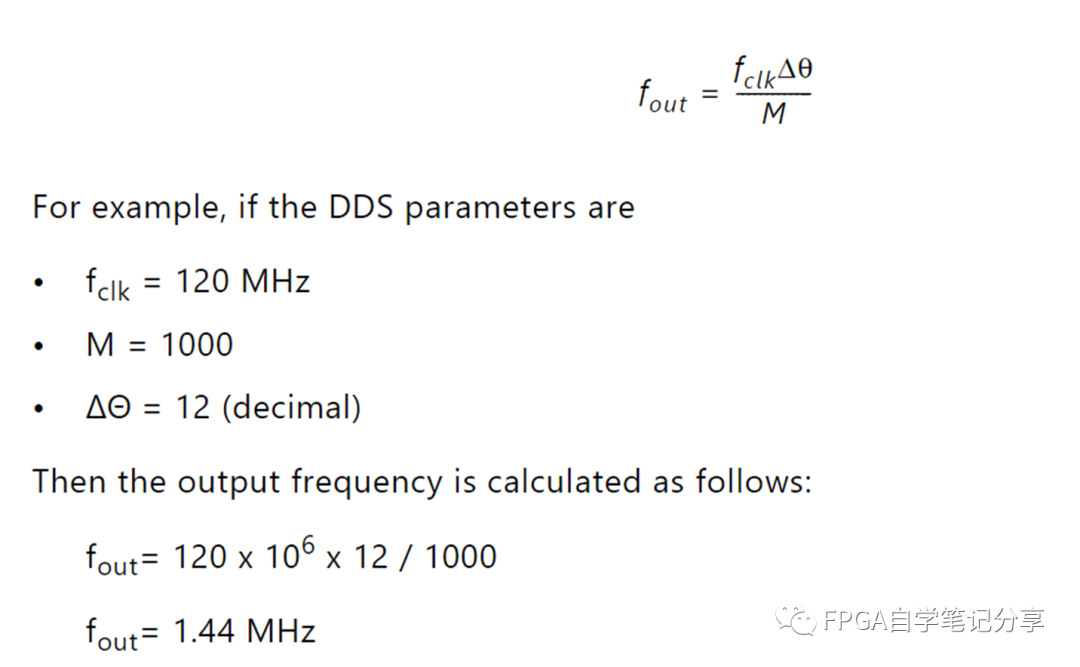

标准模式输出频率的计算方式为: 栅格化模式输出频率的计算方式为:

栅格化模式输出频率的计算方式为:

然后,我们再来看看DDS的输出精度:

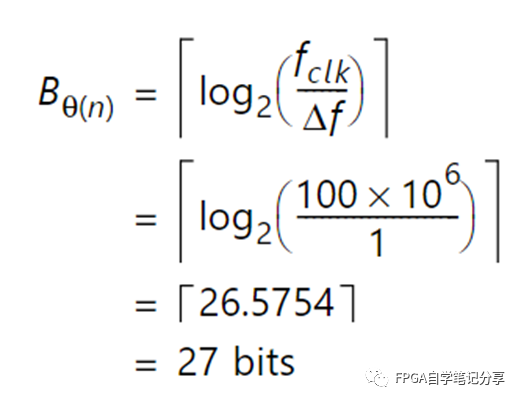

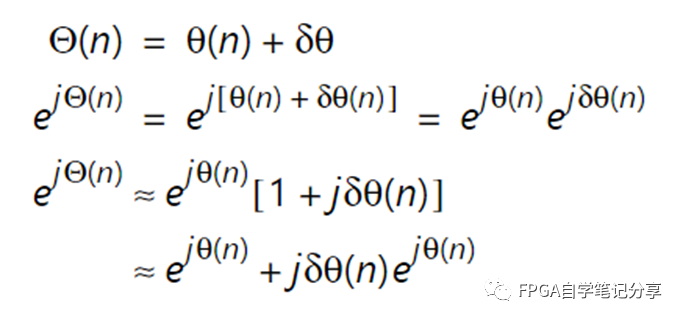

相位位宽与系统时钟频率一起决定了DDS的频率分辨率。累加器必须有足够的宽度满足系统所需的频率分辨率。在大多数实际应用中,为了满足系统的频率分辨率要求,相位累加器被分配了大量的比特。例如,如果要求的分辨率为1hz,时钟频率为100mhz,则累加器的宽度为: 为了减小LUT表格大小,量化器会对相位进行截位,抛弃高精度部分,这就会带来相位误差量化相位累加器会在输出波形中引入时基抖动。这种抖动导致与量化误差成正比的不希望的相位调制,如下所示:

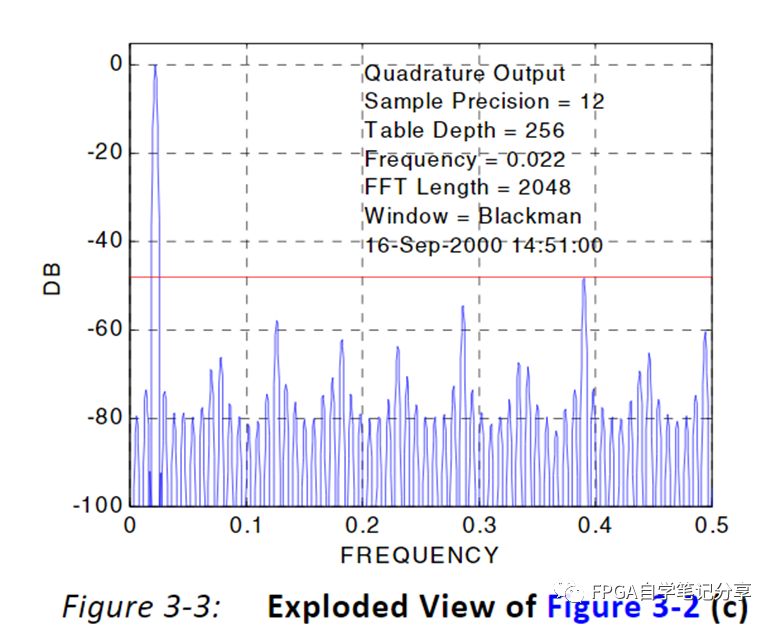

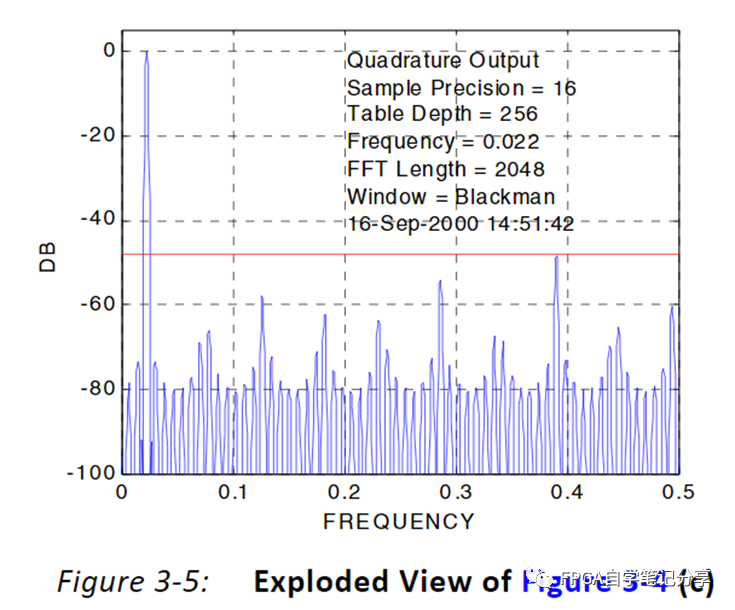

为了减小LUT表格大小,量化器会对相位进行截位,抛弃高精度部分,这就会带来相位误差量化相位累加器会在输出波形中引入时基抖动。这种抖动导致与量化误差成正比的不希望的相位调制,如下所示: 如果在输出波形中需要S dB的杂散抑制,参照0 dB主音,DDS查找表必须至少支持[S/6]地址位。例如,如果S = 70 dB,这意味着最高杂散比主信号低70 dB,那么查找表的最小地址位数是[70/6]=12位;也就是4096深的LUT表.

如果在输出波形中需要S dB的杂散抑制,参照0 dB主音,DDS查找表必须至少支持[S/6]地址位。例如,如果S = 70 dB,这意味着最高杂散比主信号低70 dB,那么查找表的最小地址位数是[70/6]=12位;也就是4096深的LUT表.

上文,参数说明中说到了噪声整形方式有:直接相位截断、相位随机抖动或泰勒级数校正,下面进行详细描述:相位抖动:通过增加性随机化信号来打破地址错误的规律性来抑制噪声。这种随机化序列称为抖动,是一种噪声序列,其方差近似等于相位累加器的最低有效整数位。在量化之前,抖动序列被Q1添加到高精度累加器输出中。与直接相位截断设计相比,抖动DDS提供了大约12 dB的无杂散动态范围(SFDR)。这是通过扩展相位误差信号的频谱能量来实现的。实现抖动序列生成器所需的额外逻辑资源很小。相位抖动模式下:如果在输出波形中需要S dB的杂散抑制,参照0 dB主音,DDS查找表必须至少支持[S/6]-2地址位。泰勒级数修正的DDS:相位抖动DDS和相位截断DDS都有一个量化器Q1,它通过丢弃高精度的分数分量来产生较低的精度。此量化步骤的原因是将查找内存的大小保持在合理的大小。代价是SFDR。随着fpga中dsp(乘法器)的逐步成熟,现在可以使用先前丢弃的小数位来计算修正查找表的输出,以产生具有非常高SFDR的输出。

0

0