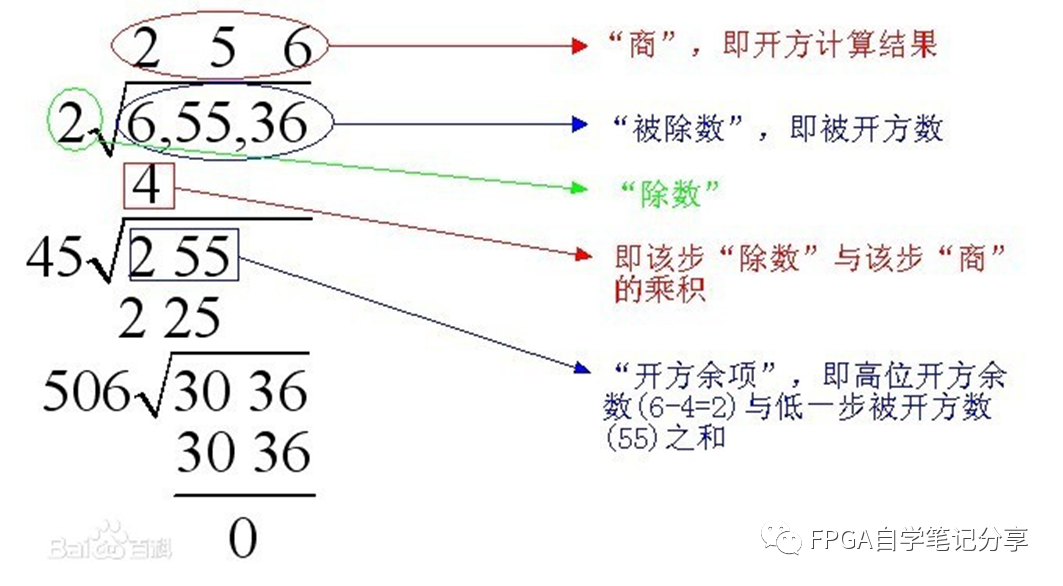

例如下边的计算:

1、将65536每两位分开,第一步找最高位的商2,余数2;2、余数2和55组成新数255,计算255=b*(2*20+b),得到b=5;3、余数为30,将30和36组合得到数据3066,计算3066 = c*(25*20+c),得到c=6.

计算过程用到的计算公式就是:

平方运算: (a+b)² = a²+2ab+b²开平方运算: (a+b)² - a² = b(2a+b)实现10进制的开根号相对复杂,对于二进制的开根号,由于数据要么是0,要么是1,所以比较好处理,可以大大简化处理流程。

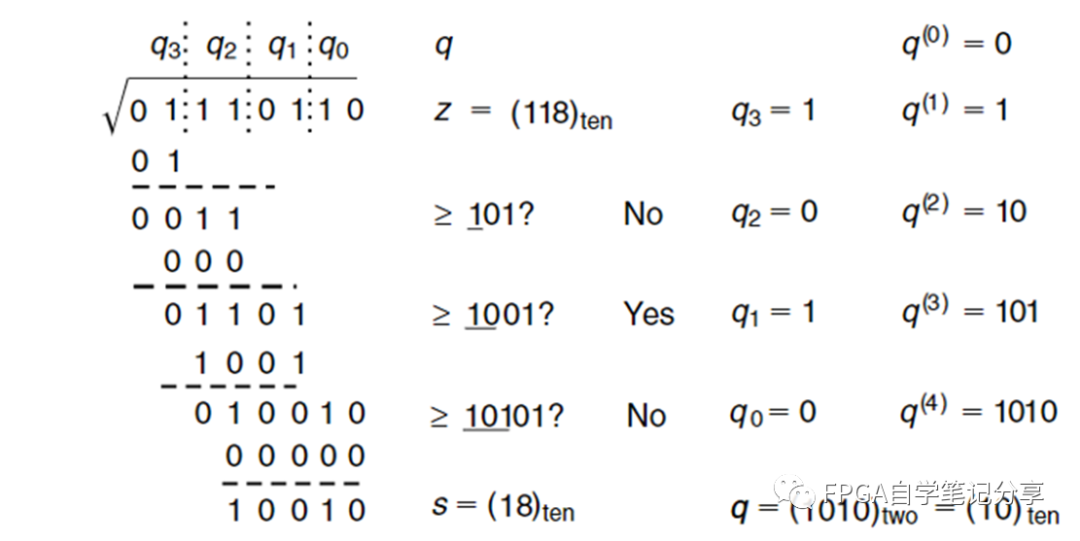

二进制开平方,由于数据全部是0或者1组成,所以二进制数据开方可以简化为:1、将被开方数向左每隔两位划为一段,分成几段,表示所求平方根是几位数;2、最高位开方: 最高两bit大于1,高位为1;3、从第一段的数减去最高位上数的平方,在它们的差的右边写上第二段数组成第一个余数;4、余数大于2a+1,第二位是1,否则是0;

如上:

1、q3为1;

2、余数为0011,小于101,q2为0

3、余数为1101,大于(2a+1) = 1001,q1为1

原理就是这样,大家可以考虑一下代码怎么实现、

0

0