★★★I2C-4---波形调试I2C★★★

撰稿:Timothy 校稿:Timothy

引言:I2C是最常见的板载通信协议之一,因为它只需要两条线:数据线(SDA)和时钟线(SCL),这些线路允许多个设备通过共享连接进行通信,但是I2C的历久弥新并不意味着它没有问题。本文将探讨常见的I2C信号问题,以及如何通过波形分析对其进行调试优化。€1.哪些问题

I2C通信问题包括:

1#:上升时间过长,上升缓慢

2#:串扰,包括SCL线上的假边缘

3#:高于预期的低电平输出电压(VOL)

4#:总线竞争和大下冲

在某些情况下,上述问题可能导致I2C通信故障和设备故障,因此了解这些问题的来源并采取适当的调试方式,如I2C波形分析,可以帮助在使用I2C时查明通信问题。

€2.上升时间过长

当上升时间太长时,可能导致信号在时间上从未达到高电平输入电压(VIH)的阈值。由于总线电容和上拉电阻直接影响上升时间,上升时间问题通常可以使用更强的上拉电阻(即电阻值较低的电阻器,有更大的上拉电流)来解决。I2C协议规定了基于所使用的最大时钟频率的最大允许上升时间,在I2C规范的2.6版本中,标准模式和快速模式的最大上升时间分别为1000ns和300ns。(传送门:I2C-2:基本协议)

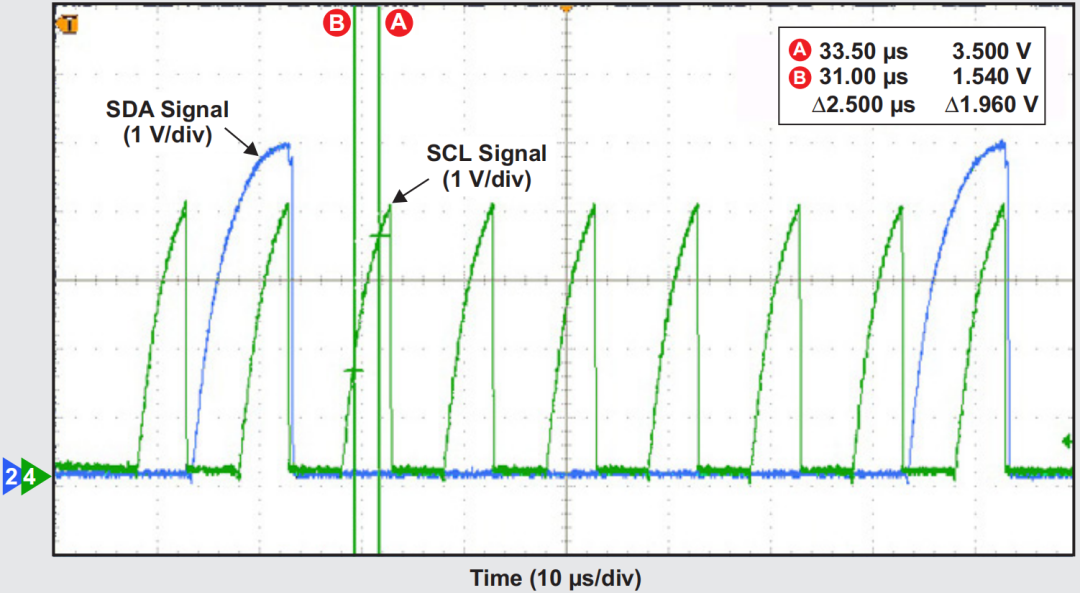

图4-1显示了与上升时间有关的I2C SCL/SDA信号,上升时间过长抢占了高周期(持续高电平)的有效时间,SCL从未达到VCC的100%,并且信号达到VCC的70%(在这种情况下为3.5V,其中VCC为5V)需要花费更长的时间。在图4-1中,上升时间(对于标准模式)过长,因为允许的最大值是1000ns,而上升时间是2500ns。一些I2C设备是边缘速率触发的,需要足够快的转换速率来检测上升脉冲,在这种情况下,缓慢的上升时间可能会影响上升沿的检测。

在极少数情况下,极快的上升/下降时间会错误地触发边缘速率触发类型I2C器件的SDA/SCL引脚上的静电放电(ESD)单元,并将SDA/SCL线锁存为低电平,直到ESD单元恢复。当额定为400KHz的I2C从设备挂载于工作频率为1MHz或更快的I2C总线上时,通常会出现这种情况。错误触发是I2C从设备放置/隔离不当的结果,所以不要在运行速度超过400KHz的I2C总线上挂载400kHz的从设备。

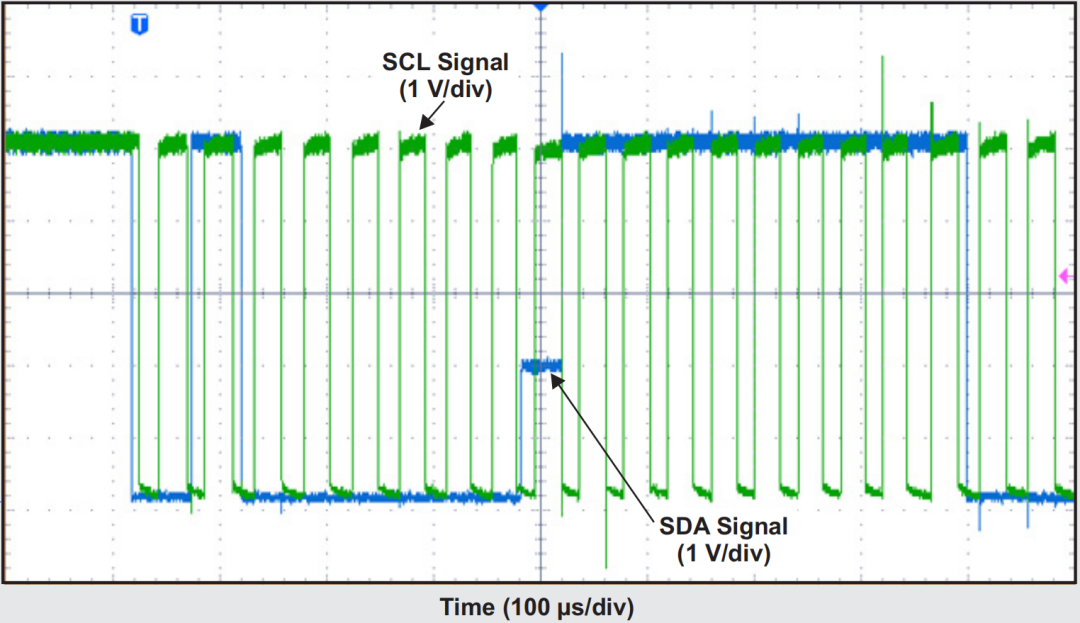

€3.串扰

串扰通常在SDA数据线上可见(尽管也可能发生在SCL线上),来源通常是SCL或SDA线上的快速上升/下降产生的高频信号耦合到SDA走线和SCL走线之间的对位电容上,耦合电容带来的耦合电压叠加到自身,拔高电平造成小尖峰毛刺。

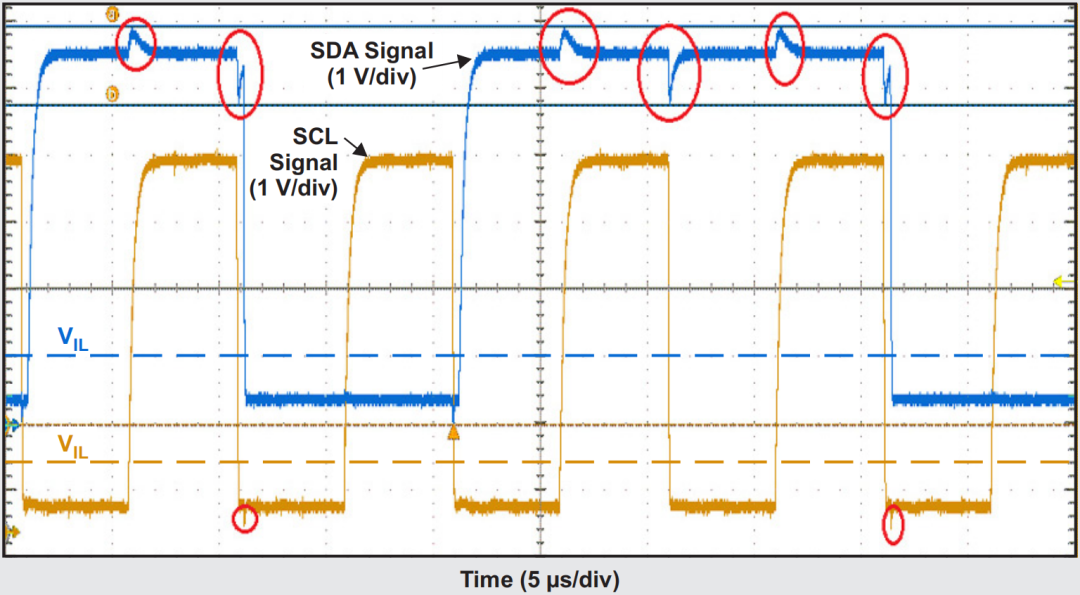

图4-2:仅轻微影响I2C信号完整性的轻微串扰示例

从图4-2中可以看到,上升沿和下降沿期间存在对位串扰,串扰不会影响整体信号完整性,因为SDA在时钟的高周期中间(当数据被实际采样时)已经保持在VIH以上或VIL以下,属于确定性电平。

如果总线上有带上升时间加速器的缓冲器/转换器,SDA/SCL上的就串扰可能会带来问题,具有上升时间加速器的器件可以在高于低电平输入电压(VIL)阈值的上升沿上触发。在I2C规范的2.6版中,VIL定义为VCC的30%,因此导致VIL以上的上升沿的任何串扰将导致接通上升时间加速器。在某些情况下,SDA线可以恢复,但SCL线最终将为从设备生成错误的上升沿,并可能导致从设备的状态机故障,出现错误数据,甚至导致总线卡滞。在SDA/SCL线路上添加额外的总线电容会有所帮助,但由于I2C规范中列出了最大电容规值,可以添加的电容值受到限制,因此解决串扰的最佳方法是在SDA/SCL线上放置小阻值串联电阻(例如10Ω、22Ω),并最小化SDA和SCL走线之间的对位总线电容。

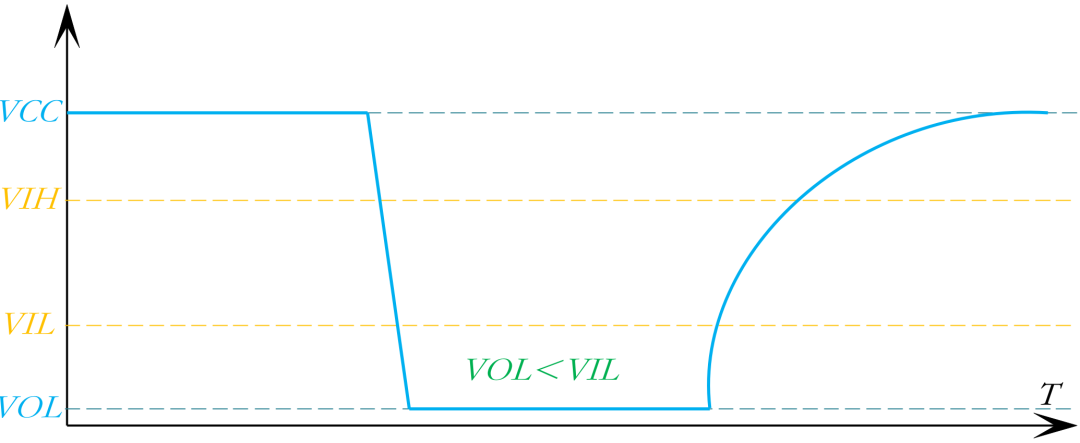

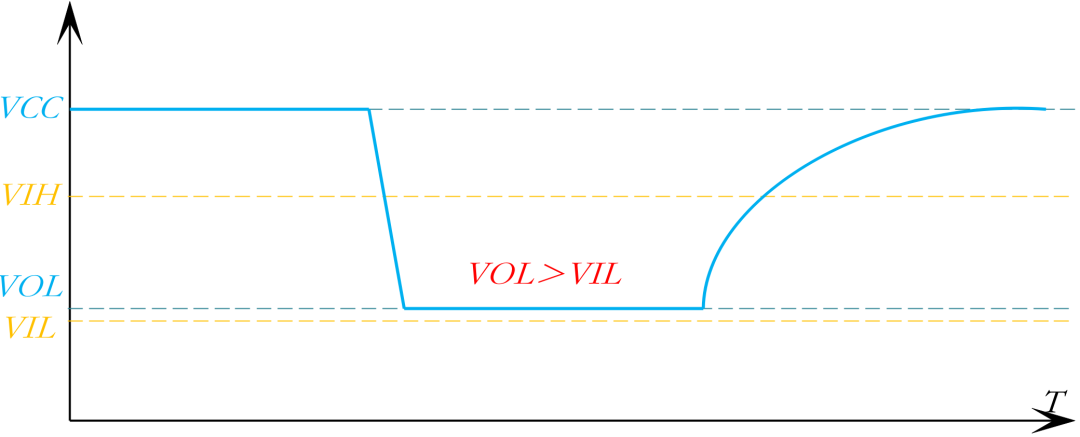

€4.VOL电平过高

较高的VOL会产生从/主设备将信号预处理为逻辑低的问题,一些I2C从设备(特别是传统器件)具有弱下拉FET,容易产生高VOL,这可能不符合VIL标准(尤其是在低VCC下,例如1.8V或1.0V逻辑)。其他时候,选择太强的上拉电阻(即值太小)可能导致VOL电平高于VIL,使线路处于未知状态。

图4-3:正确的VOL信号

图4-4:不正确的VOL信号

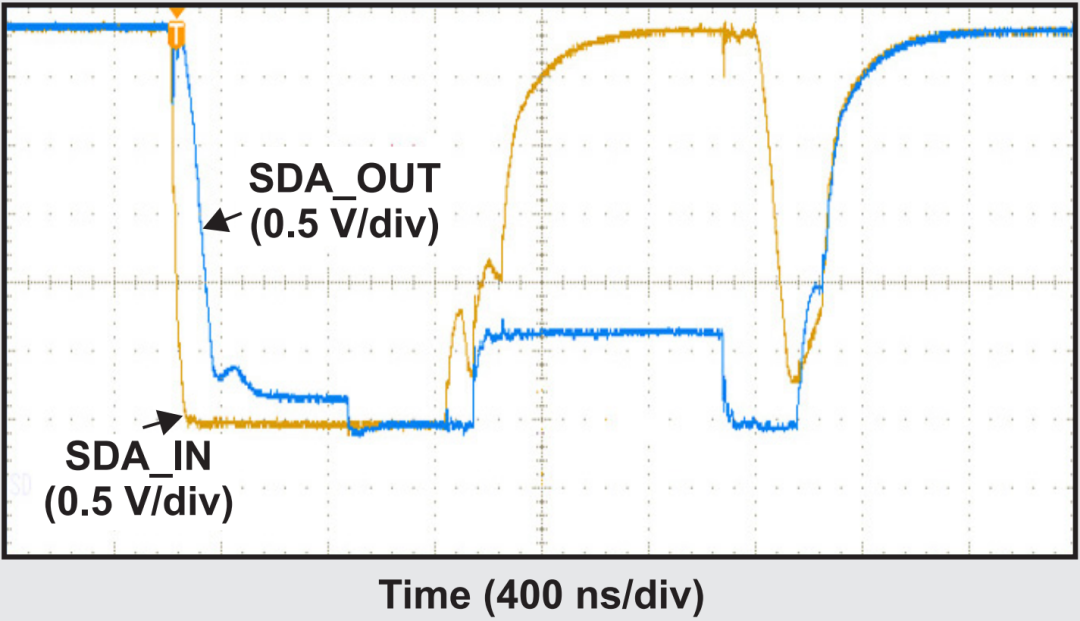

€5.意外争用

对于推挽结构的端口,当P-FET和N-FET同时导通时,会发生意外争用,一个将线路拉高,另一个拉低,这会导致非常高的VOL,其值通常落在数字逻辑的灰色区域之间(VIL和VIH之间)。在大多数系统中,不会发生意外争,因为主设备是开漏结构,因此无法生成这种争用状态。但是一些设计人员没有将I2C总线设计为开漏结构,而是使用推挽输出级,由于P-FET的强上拉,示波器上的SDA和SCL线将显示为方波,因此很容易发生意外争用。

图4-5:推挽式设计中出现的争用

在图4-5中,主机使用一个推挽驱动器,该驱动器产生具有快速上升沿的SDA信号。当从设备转到ACK时,主设备的P-FET与从设备的N-FET相反,导致产生高VOL和IOL的争用状态。高IOL足以损坏P-FET和N-FET,因为它们通常不会吸收/提供过多电流,因此,推挽式架构不能在没有仔细考虑的情况下连接到双向开放漏极从设备。其他时候,当上升时间加速器的P-FET和主/从设备的N-FET同时打开时,也会发生意外争用。

在图4-6中,上升时间加速器被接合,这意味着P-FET正在主动地将线路驱动到高电平,而从设备确认(N-FET驱动到低电平),这会导致上升时间加速器的P-FET和从设备的N-FET之间的意外争用,当加速器断开时,争用结束。

图4-6:具有上升时间加速器的缓冲区导致I2C总线上的争用

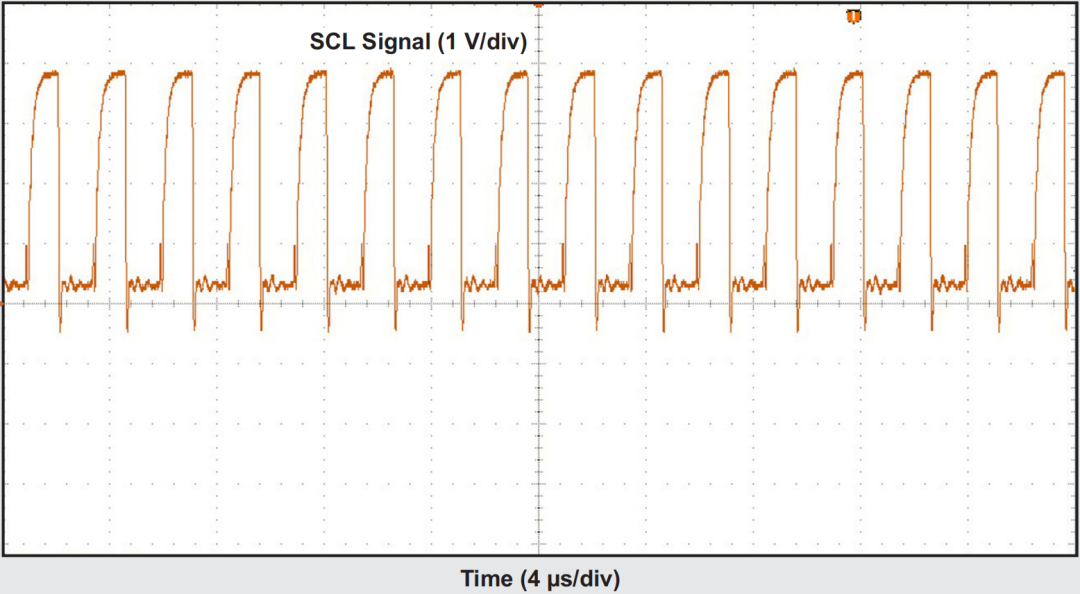

€6.下冲

除了快速下降时间外,当线路上存在大量寄生电感时,可能会出现较大的下冲(下冲来自寄生电感的反射)。这在电缆传输中更为常见,但偶尔也会在PCB走线中看到。下冲带来的问题是:如果下冲足够大,它可能会违反引脚上允许的绝对最大电压值(如设备数据表中的规定值),并导致设备故障,在许多情况下,该设备不会立即失效,即使在数千次下冲后仍能继续工作。

图4-7:SCL线上发生下冲

在图4-7中,下冲摆动至–0.5V,该电压超过了设备允许的绝对最大值,该值的绝对最大允许阈值为–0.3V,这样的大下冲会随着时间的推移对设备造成损坏,需要进行校正。

在下冲的情况下,如果下降时间不能减慢到足以防止下冲发生(串联小电阻),并且如果不能进一步最小化寄生电感,则需要箝位二极管(例如肖特基二极管)来最小化下冲,使其在数据规格范围之内。

€7.总结

对于I2C的信号完整性问题,例如高于预期的VOL电压、串扰和缓慢上升时间,通常导致I2C总线不会出现接收确认(ACK)指示信号,一般很容易发现。严重的是那些不会立即导致失效的隐形问题,此类问题可能是总线上的意外争用或大的下冲导致的,使设备随着时间的推移而发生故障,所以在这些I2C问题最终出现在用户的产品中之前,能够识别并解决它们非常重要。注:本节I2C的这些问题分析同样适用于UART、SPI等信号。

0

0