虽然并行接口在许多领域曾经广泛使用,但随着信号完整性要求的提高和传输速率的提升,许多并行接口逐步被高速串行接口(如 PCIe、SATA、以太网等)取代。然而,并行接口仍在一些嵌入式系统和专用场景中保留了优势,如 DDR 内存,仍然不可或缺。

一、并行接口的没落

在计算机和电子设备的发展历史中,并行接口曾一度占据主导地位。并行接口通过多条数据线同时传输多个比特位的数据,具备较高的带宽性能。然而,随着技术的发展,并行接口逐渐被串行接口所取代。这一转变的主要原因在于并行接口固有的一些缺陷:

-

信号干扰:并行接口需要多条信号线,这些线之间的电磁干扰会限制信号完整性,特别是在高频率下。

-

布线复杂度:并行接口的信号线数量多,PCB布线复杂,容易增加成本和设计难度。

-

同步难度:在高频情况下,保持所有信号线同步(即数据到达的时间一致)变得极具挑战性。

常见的并行接口

以下是一些经典的并行接口:

-

IDE (Integrated Drive Electronics):用于连接硬盘和主板,后来被串行接口SATA取代。

-

PCI (Peripheral Component Interconnect):并行的计算机总线标准,逐步被PCI Express(串行接口)替代。

-

Centronics:用于连接打印机,逐步被USB取代。

-

并行端口(Parallel Port):主要用于外设连接,例如打印机和扫描仪,也已逐渐淘汰。

串行接口相对并行接口的优势

串行接口通过一条或少量几条数据线传输数据,相较于并行接口,具有以下优势:

-

减少干扰:减少信号线数量降低了线间干扰,提高了信号完整性。

-

简化布线:减少引脚和PCB布线复杂性,降低了制造成本。

-

更高的频率:串行接口的点对点传输设计允许更高的传输速率。

-

同步简化:在串行接口中,通常只需同步一条数据线和一条时钟线(或者通过嵌入时钟的方法实现同步)。

-

适应性强:串行接口可以支持更长的传输距离,同时减少衰减。

二、串行接口的关键技术

串行接口的实现在芯片原理上涉及多个核心技术,包括数据的串/并转换、异步和同步通信的处理、时钟管理及恢复等。以下将详细探讨这些关键点:

1. 数据的串/并转换

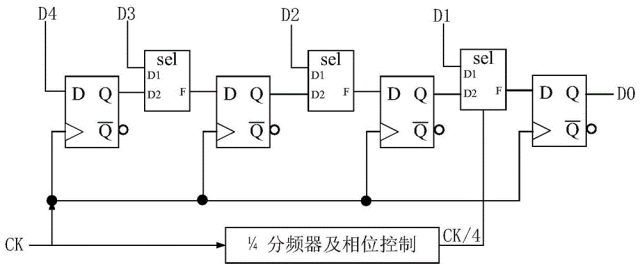

(1) 并行到串行转换 (Parallel-to-Serial Conversion)

在串行接口中,数据通常由宽并行总线(如8位或16位)转换为单比特流传输。关键步骤:

-

移位寄存器 (Shift Register):

-

并行数据写入寄存器,时钟信号控制每次移位一位,将数据按位输出为串行流。

-

例如:8位数据10110011在 8 个时钟周期内输出每一位。

串行到并行的过程比较好理解,实现方法也比较多,下图只是实例帮助理解,具体一般都是用Verilog或者VHDL语言描述。

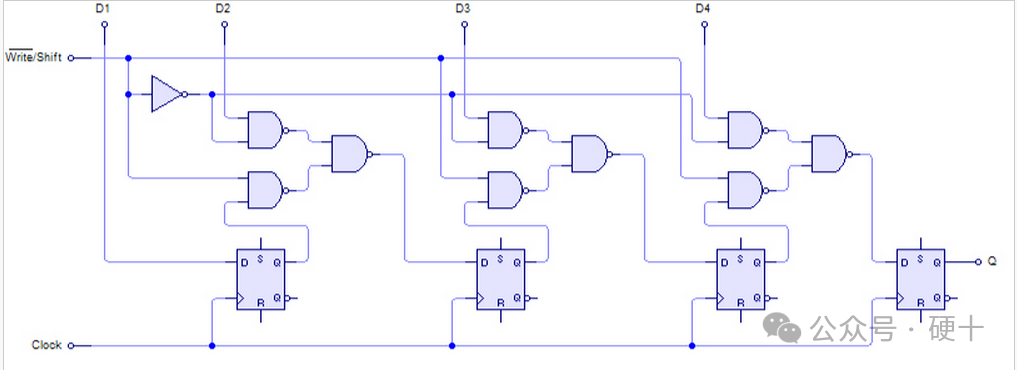

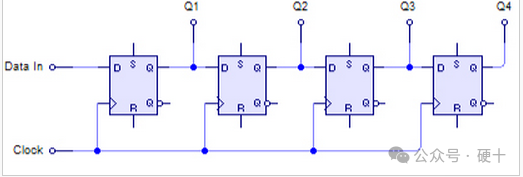

(2) 串行到并行转换 (Serial-to-Parallel Conversion)

接收端需将串行数据重组为并行数据:

-

移位寄存器:

-

数据通过串行输入端逐位移入寄存器。

-

当寄存器满后(如8位),输出并行数据给处理单元。

(3) 双缓冲机制:

为提高吞吐量,通常采用双缓冲机制,允许数据转换和传输同时进行。

2. 异步和同步通信

串行接口的关键在于如何保持数据收发双方同步

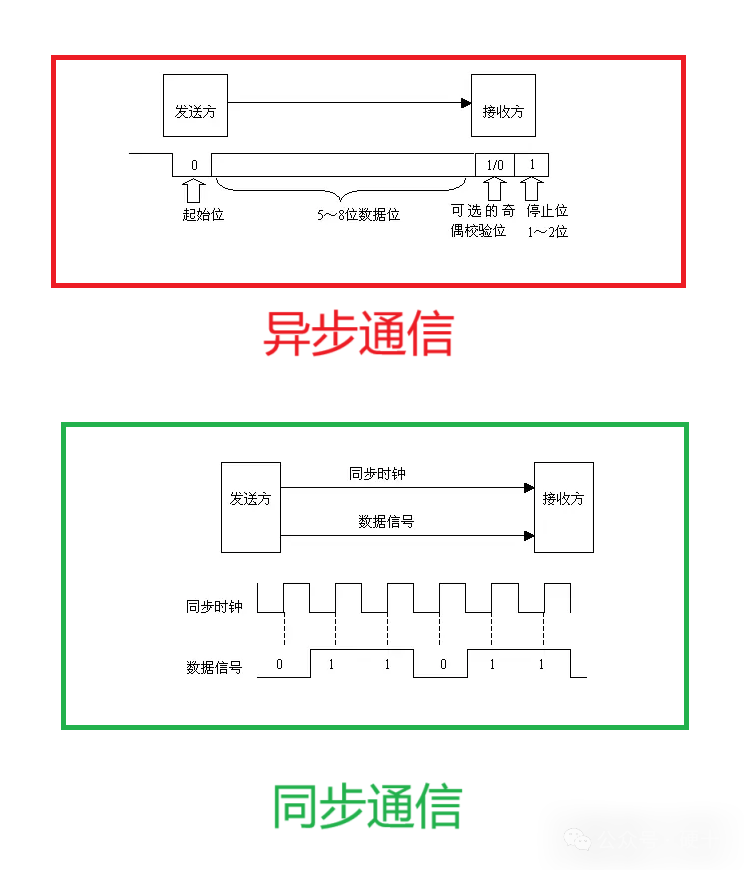

(1) 异步通信 (Asynchronous Communication)

-

**定义:**数据传输中发送端和接收端的时钟无直接关联。

-

帧结构:

-

起始位 (Start Bit):标志传输开始。

-

数据位 (Data Bits):实际传输的内容,通常为 8 位或其他配置值。

-

校验位 (Parity Bit):用于简单错误检测。

-

停止位 (Stop Bit):标志帧结束,提供接收端时间校准。

-

实现要点:

-

**波特率 (Baud Rate):**发送端和接收端必须配置一致。

-

**采样定时器:**接收端通过内部采样时钟检测起始位并锁定数据位。

(2) 同步通信 (Synchronous Communication)

-

**定义:**发送端和接收端共享同一个时钟。

-

时钟传输:

-

**独立时钟线:**如 SPI 协议,通过SCLK提供同步时钟信号。

-

**嵌入时钟:**如 Manchester 编码,时钟嵌入数据流中,接收端需恢复时钟。

-

实现要点:

-

主设备控制时钟,数据按时钟边沿采样。

-

接收端无需校准波特率,减少时序偏移问题。

3. 时钟处理

(1) 同步时钟的生成与分配

-

片上时钟生成器 (Clock Generator):通过晶振和锁相环 (PLL) 生成稳定时钟信号。

-

分频器:根据协议要求,生成合适频率的通信时钟。

(2) 异步时钟的采样与校准

-

采样率:通常为波特率的 16 倍或更高,确保高精度采样。

-

起始位检测:利用采样点检测电平变化,以锁定起始位位置。

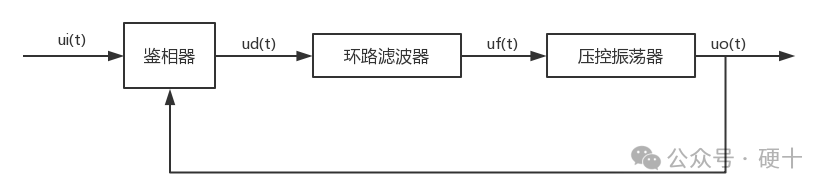

4. 时钟恢复

在某些协议中,接收端需从数据流中恢复时钟信号。

(1) 从异步数据流恢复时钟

-

边沿检测:通过检测信号的上升沿或下降沿,重新生成采样时钟。

-

数字锁相环 (DPLL):用于动态调整时钟频率,以匹配发送端时钟。

-

(2) 嵌入时钟的提取

-

编码机制:如 Manchester 编码或 8b/10b 编码,时钟信号与数据流同时传输。

-

相位对齐:通过解码模块将时钟从数据中提取并对齐。

三、常见的串行接口

串行接口按照速率可分为低速和高速接口:

低速串行接口

-

UART (Universal Asynchronous Receiver Transmitter):

-

一种异步接口,常用于短距离通信。

-

应用:嵌入式设备、传感器通信等。

I²C (Inter-Integrated Circuit):

-

一种双线的同步串行通信接口,适合主从架构。

-

应用:芯片间通信(如MCU和EEPROM之间)。

SPI (Serial Peripheral Interface):

-

高速的全双工同步通信协议,适合主从设备。

-

应用:外设通信,如显示屏、传感器。

高速串行接口

-

USB (Universal Serial Bus):

-

从USB 1.0到USB 4的演变提供了逐步提升的带宽和兼容性。

-

应用:几乎所有的外设连接。

SATA (Serial ATA):

-

替代了并行ATA,用于硬盘连接。

-

特点:点对点连接,传输速率高。

PCIe (Peripheral Component Interconnect Express):

-

串行接口,用于计算机内部高速设备互连,如显卡和固态硬盘。

-

特点:支持多通道(x1、x4、x8等)并行。

Thunderbolt:

-

高速通用接口,支持数据、视频和电源的复用。

-

应用:高性能设备连接。

MIPI DSI/CSI:

-

针对移动设备的高速接口,用于显示(DSI)和摄像头(CSI)。

四、串行接口的发展趋势与技术挑战

高速接口的实现(如 PCI、PCIe、SATA、以太网和 SERDES)涉及更复杂的技术,因为数据传输速率更高,通常达到数 Gbps 或更高。以下是这些高速接口的关键原理和实现方法:

1. 串行高速接口的核心特性

-

高速数据传输:每秒传输数 Gbps 或更高,需要优化物理层和协议层设计。

-

差分信号:高速接口通常使用差分信号(如 PCIe 的 TX+/TX-),增强抗干扰能力并减少电磁辐射 (EMI)。

-

嵌入时钟:时钟和数据在同一信号中传输(如 PCIe 和 SATA),减少引脚数量,简化连接。并且有一系列优化SI的手段。

-

多通道:支持多通道并行传输(如 PCIe 的 x1、x4、x8 通道配置)。

2. 高速接口的关键技术

(1) 串并转换(SerDes)

-

串行器/解串器 (SerDes):

高速接口中,SerDes 是数据串行化和解串行化的核心模块。 -

解串器从接收的串行数据流中提取时钟。

-

根据时钟信号将串行数据重新转换为并行数据。

-

并行数据经并行总线输入串行器。

-

使用高速移位寄存器将数据按位输出,同时嵌入时钟信号。

-

发送端:

-

接收端:

-

SerDes 的速率匹配:通常采用片上锁相环 (PLL) 精确控制数据传输速率。

(2) 时钟嵌入与恢复

-

嵌入时钟:

-

在高速传输中,通过编码技术(如 8b/10b 或 64b/66b 编码)将时钟信号嵌入数据流,简化布线并提高可靠性。

-

时钟恢复:

-

接收端通过锁相环 (PLL) 或时钟数据恢复 (CDR) 技术提取嵌入的时钟信号。

-

相位对齐:利用数据的过零点调整时钟相位,确保数据采样正确。

(3) 差分信号传输

-

双端传输:高速接口采用差分对(如 PCIe 的 TX+/TX-),两个信号电平相反,增强抗干扰能力。

-

优点:

-

抵消电磁干扰 (EMI)。

-

提高信号完整性,尤其在高频信号中减少串扰。

3. 典型高速接口的实现

(1) PCI 到 PCIe

-

PCI(并行总线):

-

使用共享时钟信号,所有设备按总线仲裁机制轮流访问总线。

-

存在时钟偏差和信号完整性问题,限制了传输速率。

-

PCIe(点对点串行总线):

-

物理层:SerDes 负责数据串行化和解串行化。

-

数据链路层:处理数据包分组和错误校验。

-

事务层:支持高层协议(如内存读写请求)。

-

点对点链路:每个设备有独立的通信链路,消除总线仲裁延迟。

-

多通道配置:x1、x4、x8 等通道配置,多个通道可并行传输,提高带宽。

-

分层架构:

(2) SATA(串行ATA)

-

架构:

-

由并行 ATA 演变而来,采用全双工串行通信。

-

使用 8b/10b 编码,嵌入时钟,支持数据速率高达 6 Gbps(SATA 3.0)。

-

工作原理:

-

主机通过 SerDes 发送串行数据流,存储设备解码后处理。

-

双向链路实现读写操作,同时保持高信号完整性。

(3) 以太网(Ethernet)

-

低速到高速的演变:

-

从最早的 10 Mbps 发展到 10 Gbps、25 Gbps,甚至 400 Gbps。

-

关键技术:

-

物理层:使用差分对传输,支持长距离传输。

-

编码:如 PAM4 编码,通过每个符号携带更多比特,提高带宽利用率。

-

时钟恢复:在接收端使用 CDR 技术精确提取时钟。

4. SerDes 在高速接口中的角色

SerDes 是所有高速接口的核心,实现以下功能:

-

发送端:

-

将并行数据以高频率转换为串行数据流。

-

嵌入时钟,减少额外的时钟线。

接收端:

-

从串行数据中恢复时钟信号。

-

对串行数据解码并重新组合成并行数据。

时序管理:

-

使用锁相环 (PLL) 控制高速信号的相位和频率。

-

减少抖动 (Jitter),确保数据完整性。

5. 信号完整性和高速设计

高速接口面临的主要挑战是信号完整性,设计中需重点考虑:

-

抖动 (Jitter):时钟或数据信号的随机偏移。需优化 PLL 和 SerDes 的设计以减少抖动。

-

眼图 (Eye Diagram):用于分析信号质量,良好的眼图表示高信号完整性。

-

阻抗匹配:差分对的阻抗需匹配 PCB 走线设计,避免信号反射。

-

去均衡 (De-Emphasis):在发送端对高频成分增加衰减,减少长距离传输中的信号失真。

五、为什么并行接口线多,却速率不如串行总线。

-

无需独立时钟信号,噪声干扰更少

高速串口通过编码技术(如8b/10b编码)将时钟信息嵌入数据流中,而不需要单独传输时钟信号。数据流本身经过加扰,避免了长串相同的比特(如连续超过5个0或1),确保时钟恢复的稳定性,同时消除了周期性变化,避免频谱集中。这种设计通过数据沿变使用PLL恢复时钟,进而采集数据流。省去独立时钟的传输不仅显著降低了功耗,还减少了由时钟信号引入的噪声干扰。 -

差分传输增强抗干扰能力

高速串口采用差分信号传输,当外界噪声同时作用于两条差分线时,接收端通过相减可以有效抵消干扰。差分设计对外界噪声有很强的抵抗能力,确保数据传输的稳定性。 -

无时钟偏移问题

由于高速串口不依赖同步时钟,不存在时钟与数据对齐的问题。只需保证差分信号线的长度匹配即可,这相对容易实现。差分信号的两条线总是保持相反状态且高度相关,即便发生延时变化,也可以通过简单的延时补偿实现对齐。而在并行总线中,由于多根独立信号线的无相关性,不同信号线的跳变时间容易受布线、阻抗和噪声的影响,从而产生时钟偏移问题,导致数据传输错误。 -

线少、干扰低

并行传输通常需要32或64条信号线,线间的电磁干扰显著,尤其在高频下,可能导致数据篡改或误码。相比之下,串行传输仅需4条线(如Rx和Tx的两对差分线)。差分信号在线路跳变时会产生相反的干扰,从而互相抵消,确保总噪声趋于零,避免内部噪声问题。

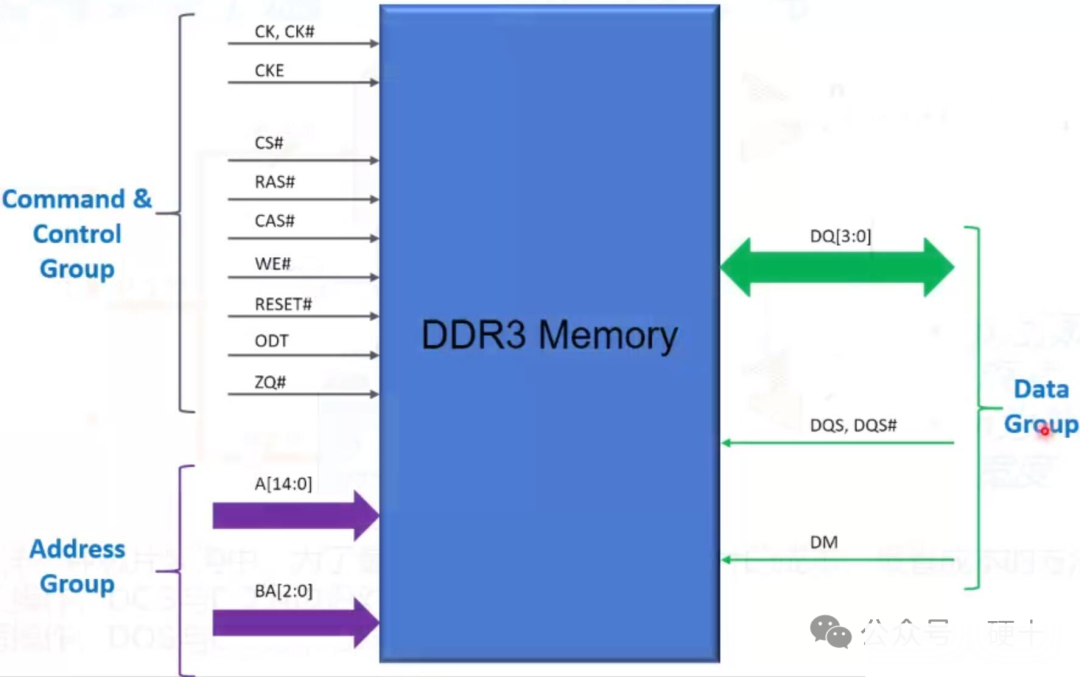

六、DDR接口为什么还保留并行,没有演进成串行总线?

DDR接口保持并行传输而没有被串行总线替代,主要是因为其特定的应用需求和技术特点,使并行传输在这一场景中更具优势:

1. 延迟要求苛刻,串行传输不具备优势

-

并行总线延迟更低:DDR存储器的一个核心需求是低延迟。串行总线需要经过数据序列化和解序列化(SerDes)过程,这会引入额外的延迟,而DDR接口直接传输多条并行数据线,延迟更小,更适合需要实时响应的存储访问。

-

内存带宽与时延的平衡:DDR接口通过宽度(多条数据线并行传输)和频率的结合来提供高带宽,而串行接口在达到相同带宽时会牺牲一些时延。

2. 高带宽需求与物理距离限制

-

内存与控制器距离较短:DDR接口设计用于处理器和内存之间的短距离高带宽通信。在这种场景下,并行总线可以通过多条线同时传输数据,高效地利用接口带宽,而无需像串行总线那样依赖高频率来提升速率。

-

更高的带宽扩展性:并行总线通过增加数据位宽(如64位、128位)简单直观地扩展带宽,而串行接口受限于单通道的速率提升,需要更复杂的设计。

3. 成本与功耗的平衡

-

节约SerDes资源:串行总线需要SerDes模块来实现高速序列化和解序列化,这增加了成本、功耗和设计复杂性。而并行DDR接口无需额外的SerDes硬件,整体系统功耗更低。

-

控制信号复用困难:DDR接口中控制信号(如行列选通、地址信号等)和数据是分离的,适合并行总线的传输方式。而串行总线需要更复杂的协议和逻辑来处理这些信号,可能带来额外的开销。

4. 设计和兼容性考虑

-

长期成熟的生态系统:DDR技术经过多年优化,已经形成了高度成熟的标准和广泛的支持生态,包括芯片设计、PCB布线、信号完整性工具等。大规模切换到串行总线需要对整个生态进行重构,成本高昂且技术风险较大。

-

布线难度可控:尽管并行总线存在时钟偏移问题,但通过技术手段(如飞线对齐、信号校正等)可以有效解决。而串行总线的高速信号布线要求更高,可能反而在PCB设计中增加复杂度。

5. 适用场景的差异

串行总线(如PCIe、SATA)通常用于长距离、高速、点对点通信场景,而DDR接口的核心应用场景是短距离、低延迟的存储访问。这两种场景需求截然不同,导致串行总线的优势在DDR应用中并不显著。

虽然串行总线在许多领域表现优异,但DDR接口之所以继续采用并行架构,是因为它能更好地满足内存访问对低延迟、高带宽和成本控制的需求。同时,DDR技术已经发展得非常成熟,切换到串行总线需要巨大的技术和生态变革,因此并行传输依然是DDR接口的最优解。

0

0