74LS74系列设备包含两个独立的D型正边触发触发器。预设或清除输入的低电平设置或重置输出,而与其他输入的电平无关。当预置和清除不活跃(高)时,D输入中满足设置时间要求的数据被转移到时钟脉冲正向边缘的输出。时钟触发发生在一个电压水平,并不是直接相关的上升时间的时钟脉冲。根据保持时间间隔,D输入处的数据可以在不影响输出处的电平的情况下进行更改。

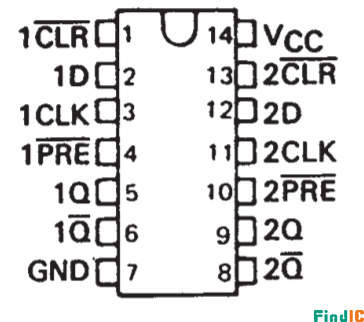

74LS74系列引脚图及引脚说明:

1CLR(1): 复位信号

1D(2): 触发信号

1CLK(3): 时钟信号

1-PRE(4): 控制

1Q(5): 同相位输山

1-Q(6): 反相位输出

GND(7): 地

2-Q(8): 反相位输出

2Q(9): 同相位输出

2-PRE(10): 控制

2CLK(11): 时计信号

2D(12): 触发信号

2-CLR (13): 复位信号

Vcc(14): 电源电压

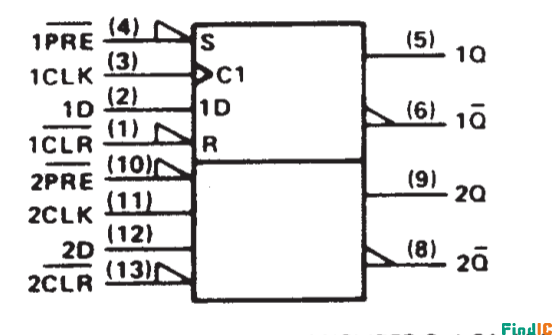

74LS74系列逻辑符号图及活性逻辑图:

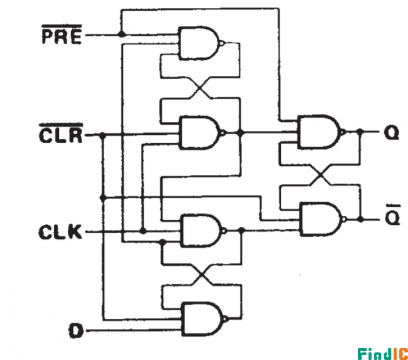

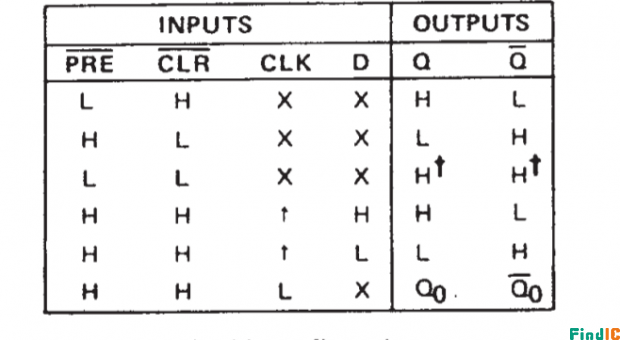

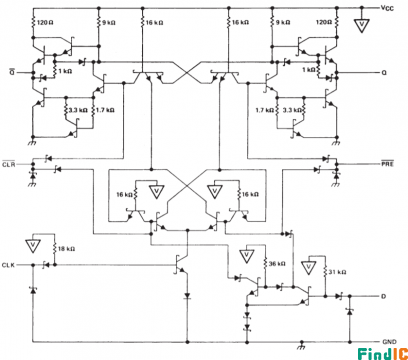

74LS74系列真值表及原理图:

SN74LS74AN核心参数:

商标: Texas Instruments

逻辑系列: LS

输入/出类型: TTL

传播延迟时间: 40ns

高电平输出电流: -0.4mA

低电平输出电流: 8mA

电源电压-最小: 4.75V

电源电压-最大: 5.25V

工作温度范围: 0°C~+70°C

封装: PDIP-14

电路数量: 2

通道数量: 2

输入线路数量: 3

输出线路数量: 1

工作电源电压: 5 V

高度: 4.57 mm

长度: 19.3 mm

宽度: 6.35 mm

单位重量: 1 g

0

0