中断系统的使用极大的提高了CPU的利用率。

中断是一种机制,这种机制实现的过程可分为请求-->响应-->服务-->返回。

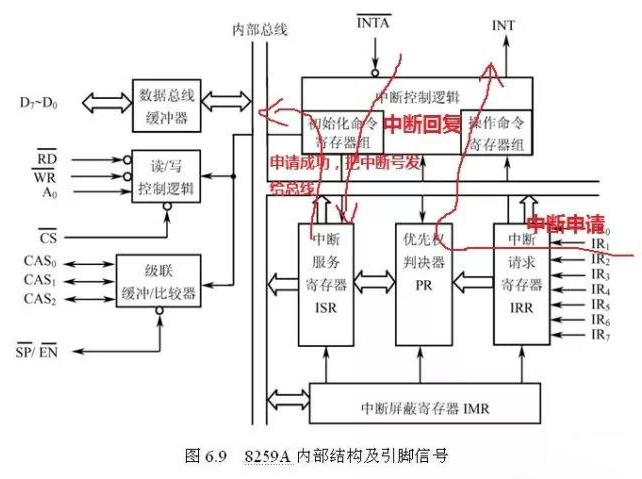

可编程中断控制器8259A是Intel公司专为80x86 CPU控制外部中断而设计开发的芯片。其内部结构及引脚图如下:

中断申请的过程可大概描述为:中断源发生-----》(此中断未被屏蔽)中断优先级判定(高于正在服务的中断则打断)------》向cpu发送中断请求-----》cpu回复一个inta告诉中断申请成功------》中断服务寄存器相应的位置位,表示这个中断正在被执行---------》当收到cpu的第二个inta的时候,中断逻辑单元把中断号发给cpu,cpu调用相应的中断程序执行------》发送中断号时,将ISR的相应位复位(利用完了就复位,主要是把中断号拿出来。如果不复位,则每次逻辑电路放在总线上的中断号就会出错),表示执行完毕。

其内部涉及的关键型寄存器有:中断请求寄存器,中断屏蔽寄存器,中断优先级判别寄存器,中断服务寄存器。

对于8259A的各个模块的“官方”描述如下:

(1)数据总线缓冲器

数据总线缓冲器为三态、双向、8位寄存器,数据线D7~D0与CPU系统总线连接,构成CPU与8259A之间信息传送的通道。

(2)读/写控制逻辑

读/写控制逻辑用来接收CPU系统总线的读/写控制信号和端口地址选择信号,用于控制8259A内部寄存器的读/写操作。

(3)级联缓冲/比较器

8259A既可以工作于单片方式,也可以工作于多片级联方式,级联方式硬件连接如图6.10所示。级联缓冲/比较器提供多片8259A的管理和选择功能,其中一片为主片,其余为从片。

(4)中断控制逻辑

中断控制逻辑按照编程设定的工作方式管理中断,负责向片内各部件发送控制信号,向CPU发送中断请求信号INT和接收CPU回送的中断响应信号,控制8259A进入中断管理状态。

(5)中断请求寄存器(interrupt request register,IRR)

IRR是一个8位寄存器,用于记录外部中断请求。其中D7~D0分别与外部中断请求信号IR7~IR0相对应,当IRi(i=0~7)有请求(电平或边沿触发)时,IRR中的相应位Di置1,在中断响应信号有效时,Di被清除。

(6)中断服务寄存器(interrupt service register,ISR)

ISR是一个8位寄存器,用于记录CPU当前正在服务的中断标志。当外部中断IRi(i=0~7)的请求得到CPU响应进入服务时,由CPU发来的第一个中断响应脉冲将ISR中的相应位Di(i=0~7)置1,而ISR的复位则由8259A中断结束方式决定。若定义为自动结束方式,则由CPU发来的第二个中断响应脉冲的后沿将Di复位为0;若定义为非自动结束方式,则由CPU发送来的中断结束命令将其复位。

(7)中断屏蔽寄存器(interrupt mask register,IMR)

IMR是一个8位寄存器,用来存放IR7~IR0的中断屏蔽标志。它的8个屏蔽位D7~D0与外部中断请求IR7~IR0相对应,用于控制IRi的请求是否允许进入。当IMR中的Di位为1时,对应的IRi请求被禁止;当IMR中的Di位为0时,则允许对应的中断请求进入。它可以由软件设置或清除,通过编程设定屏蔽字,可以改变原来的优先级别。

(8)优先权判决器(priority register,PR)

优先权判决器对IRR中记录的内容与当前ISR中记录的内容进行比较,并对它们进行排队判优,以便选出当前优先级最高级的中断请求。如果IRR中记录的中断请求的优先级高于ISR中记录的中断请求的优先级,则由中断控制逻辑向CPU发出中断请求信号INT,中止当前的中断服务,进行中断嵌套。如果IRR中记录的中断请求的优先级低于ISR中记录的中断请求的优先级,则CPU继续执行当前的中断服务程序。

0

0