电路中的 MOS 管

衡丽

498浏览

0评论

0点赞

2023-06-05

eg:

N-channel-JFET:

P-channel JFET:

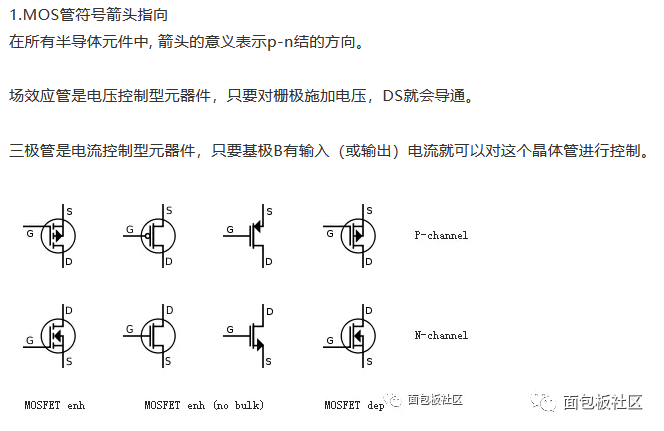

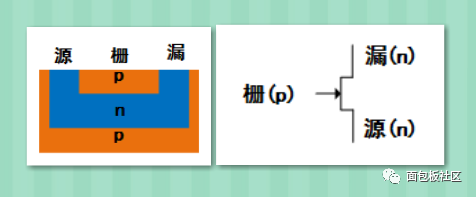

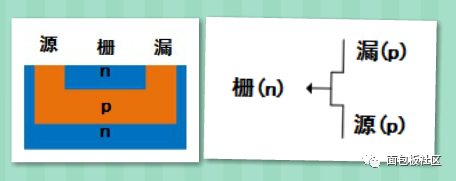

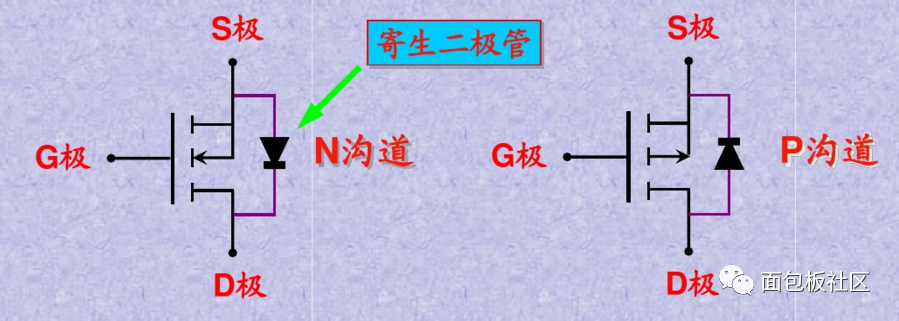

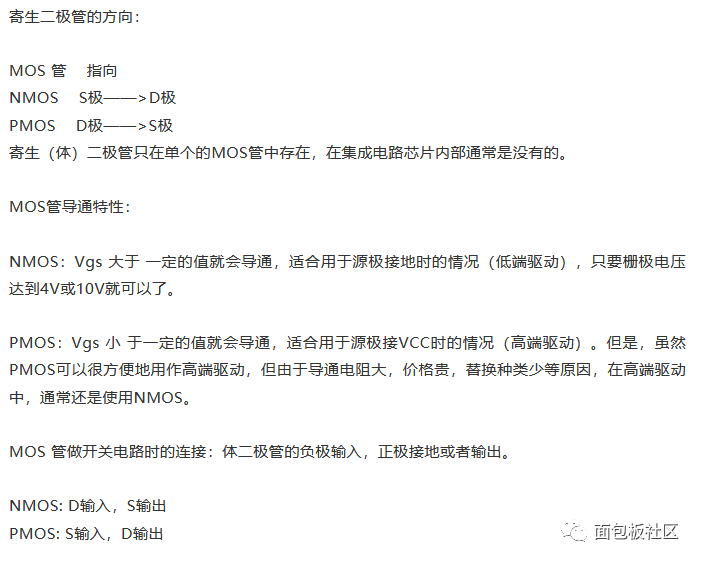

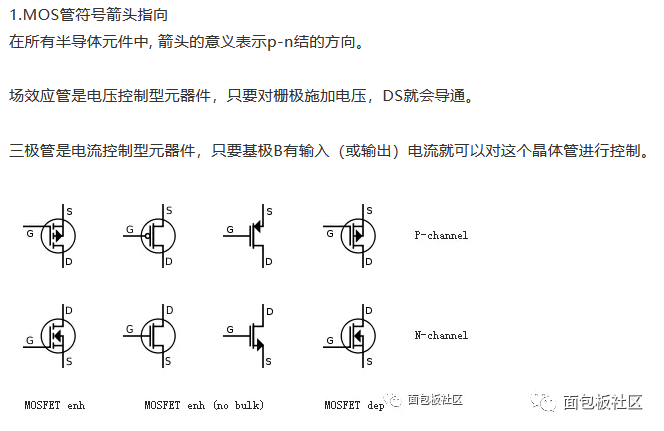

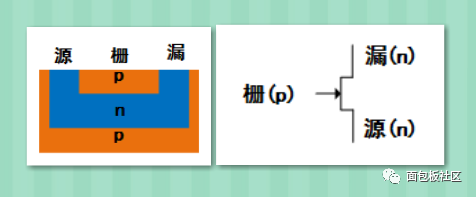

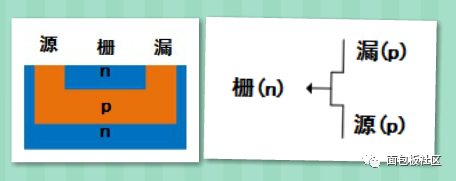

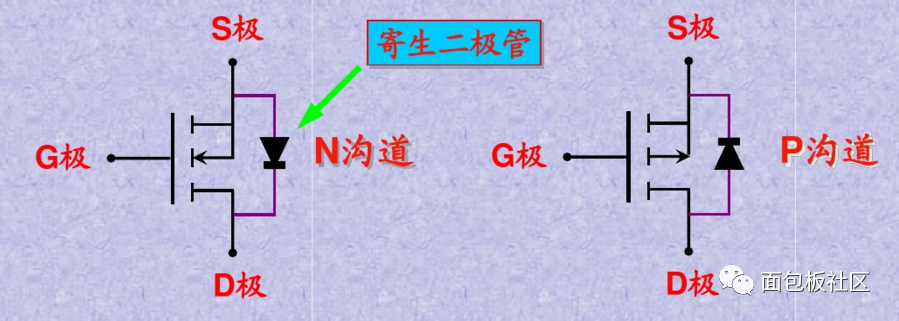

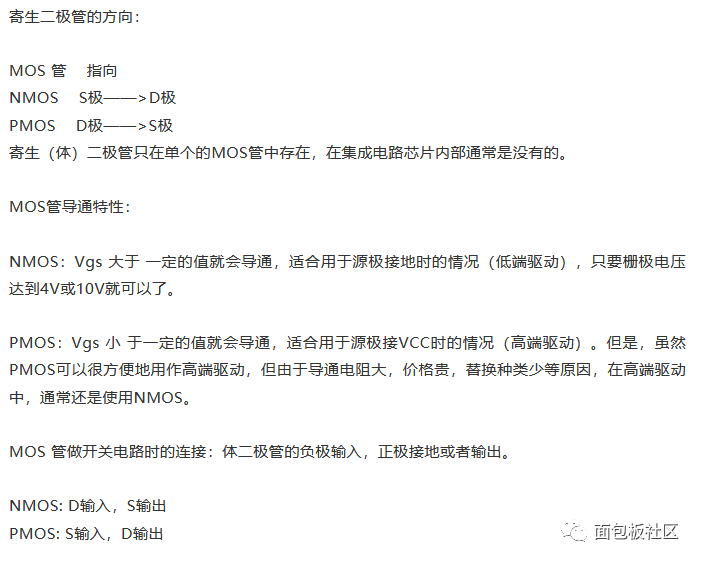

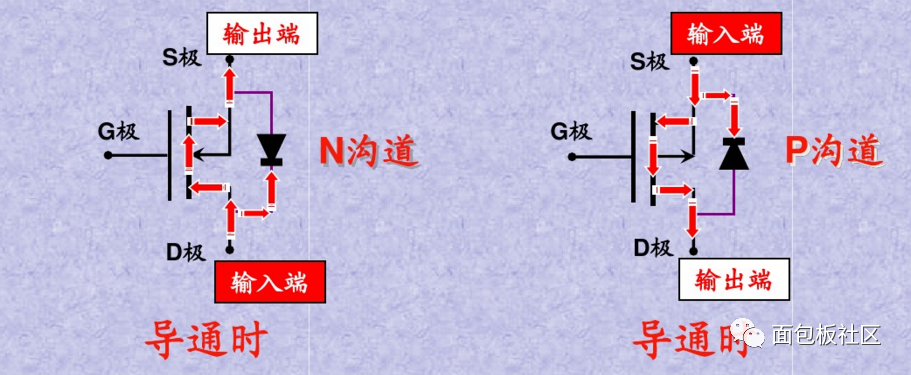

电路中的 MOS 管符号:

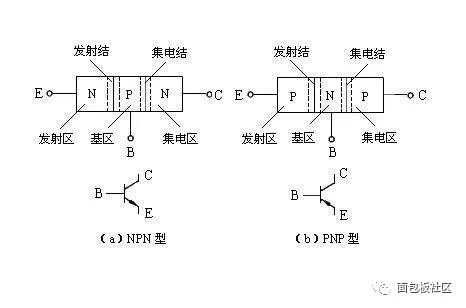

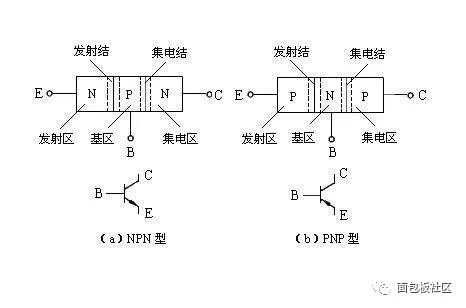

电路中的三极管符号:

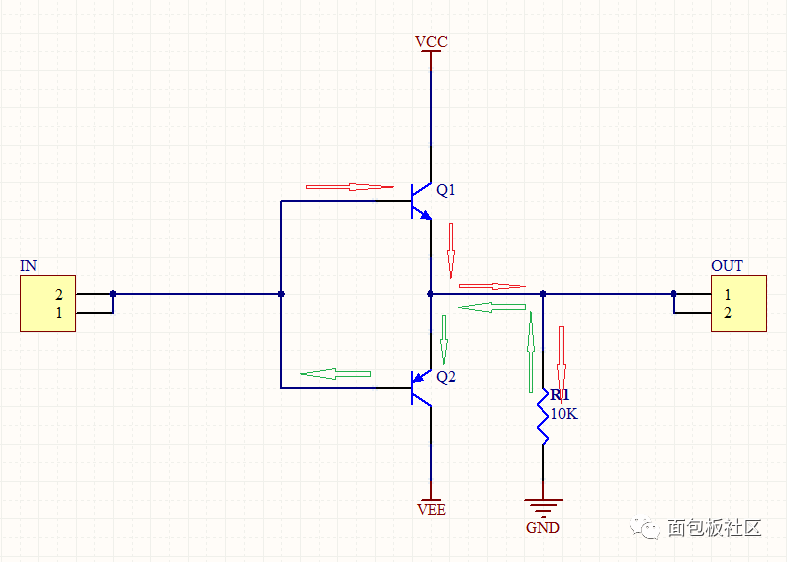

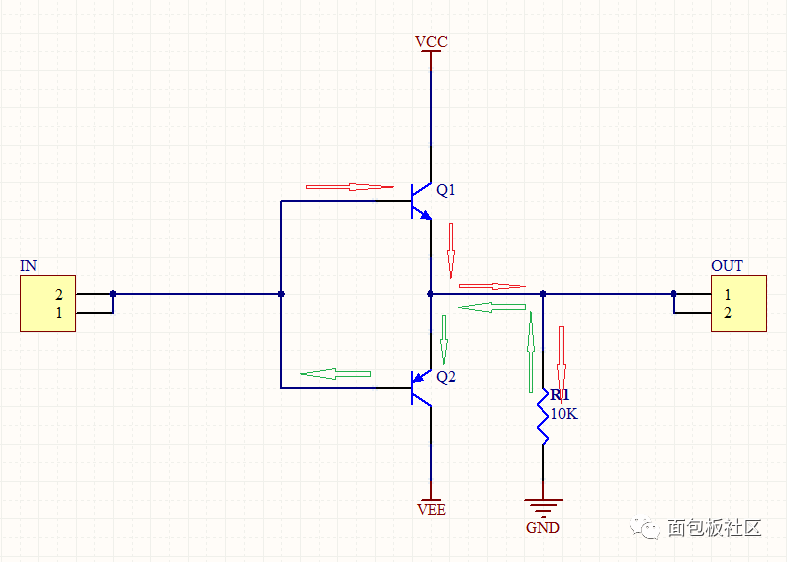

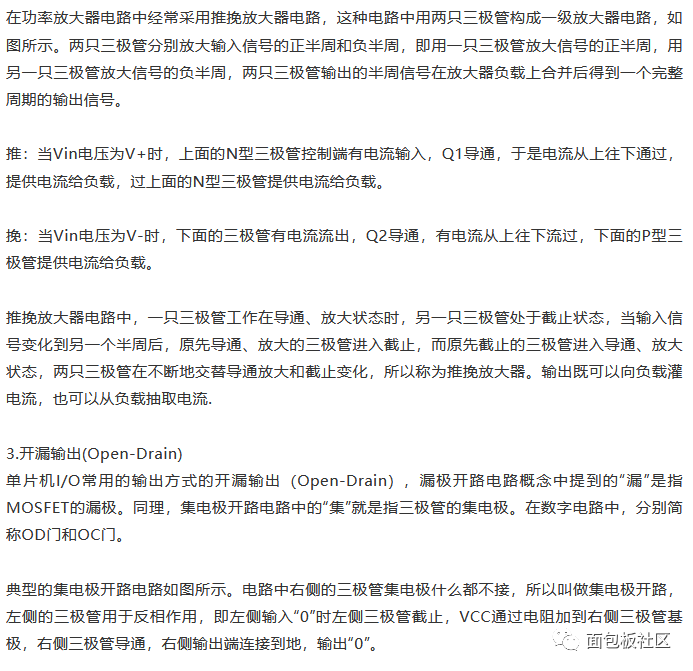

2.推挽输出(Push-Pull)

推挽输出是用两个晶体管或者场效应管构成的推挽电路,电路的特点就是输出电阻小。可以输出高,低电平,连接数字器件。push-pull 高低电平由IC的电源低定,不能简单的做逻辑操作等。push-pull是现在CMOS电路里面用得最多的输出级设计方式。

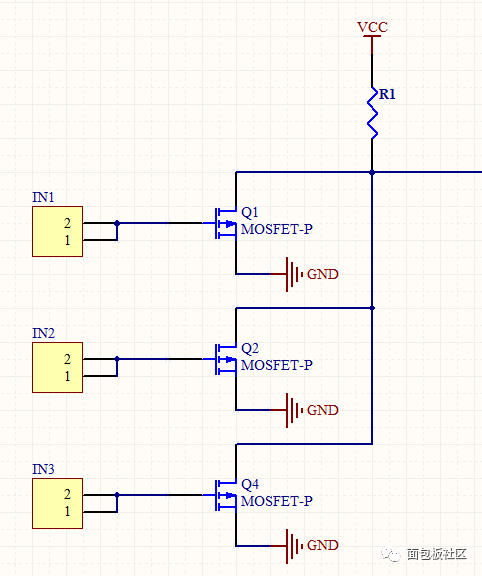

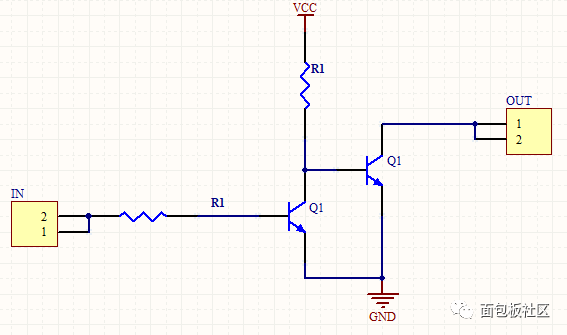

从图中电路可以看出集电极开路是无法输出高电平的,输出端悬空时变为高阻态,这时电平状态未知(对于经典的51单片机的P0口而言,要想做输入输出功能必须加外部上拉电阻,否则无法输出高电平逻辑),如果要想输出高电平可以在输出端加上上拉电阻。因此集电极开路输出可以用做电平转换,通过上拉电阻上拉至不同的电压,来实现不同的电平转换。

集电极开路输出除了可以实现多门的线与逻辑关系外,通过使用大功率的三极管还可用于直接驱动较大电流的负载,如继电器、脉冲变压器、指示灯等。由于现在MOS管用普遍,而且性能要比晶体管要好,所以很多开漏输出电路和推挽输出电路都用MOS管实现。

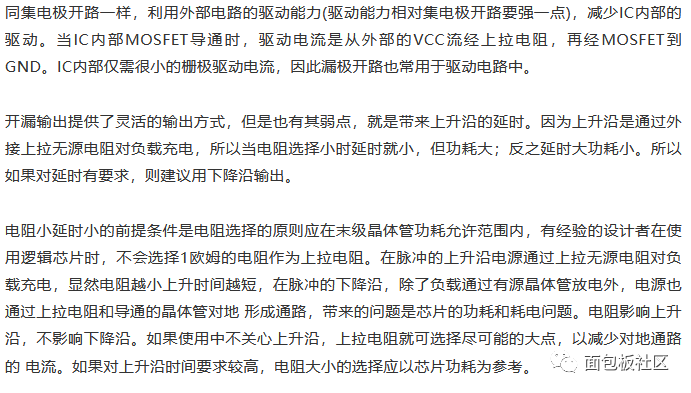

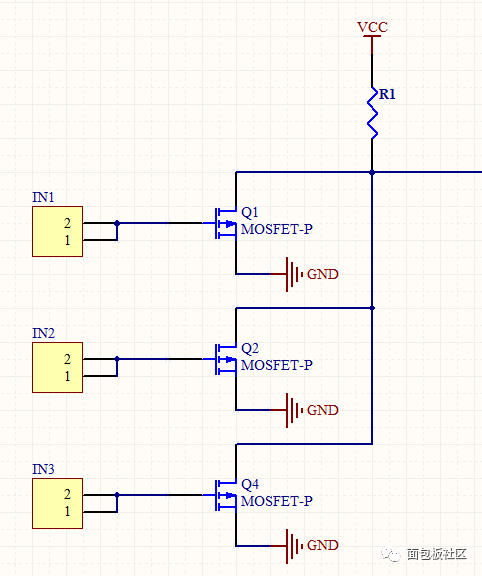

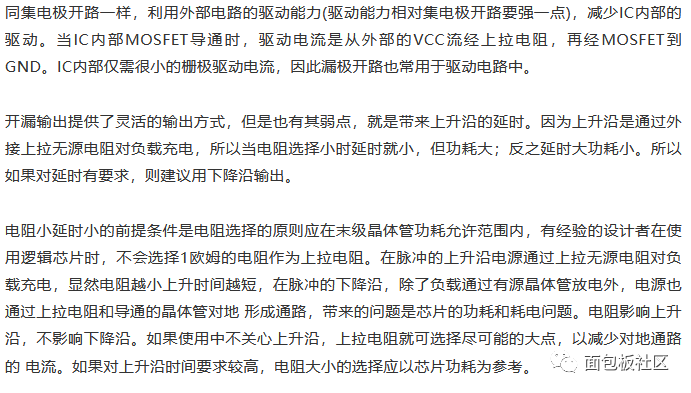

完整的开漏电路应由开漏器件和开漏上拉电阻组成。这里的上拉电阻R的阻值决定了逻辑电平转换的上升/下降沿的速度。阻值越大,速度越低,功耗越小。因此在选择上拉电阻时要兼顾功耗和速度。标准的开漏脚一般只有输出的能力。添加其它的判断电路,才能具备双向输入、输出的能力。

开漏电路做驱动器时,由于OC门电路的输出管的集电极悬空,使用时需外接一个上拉电阻R到电源VCC。OC门使用上拉电阻以输出高电平,此外为了加大输出引脚的驱动能力。上拉电阻阻值的选择原则:从降低功耗及芯片的灌电流能力考虑应当足够大;从确保足够的驱动电流考虑应当足够小。

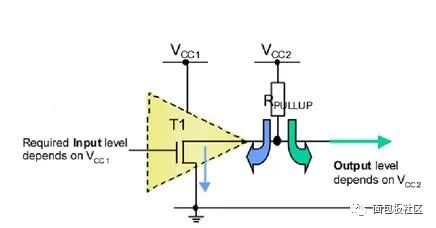

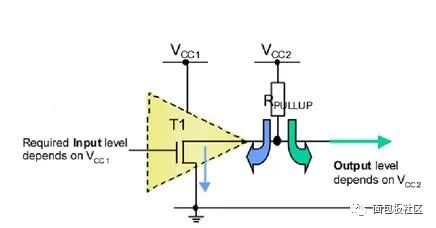

可以利用改变上拉电源的电压,改变传输电平。如上图, IC的逻辑电平由电源Vcc1决定,而输出高电平则由Vcc2(上拉电阻的电源电压)决定。这样我们就可以用低电平逻辑控制输出高电平逻辑了(这样就可以进行任意电平的转换)。(例如加上上拉电阻就可以提供TTL/CMOS电平输出等。)

将OC门输出连在一起时,再通过一个电阻接外电源,可以实现**“线与”**逻辑关系。只要电阻的阻值和外电源电压的数值选择得当,就能做到既保证输出的高、低电平符合要求,而且输出三极管的负载电流又不至于过大。当这些引脚的任一路变为逻辑0后,开漏线上的逻辑就为0了。在I2C等接口总线中就用此法判断总线占用状态。

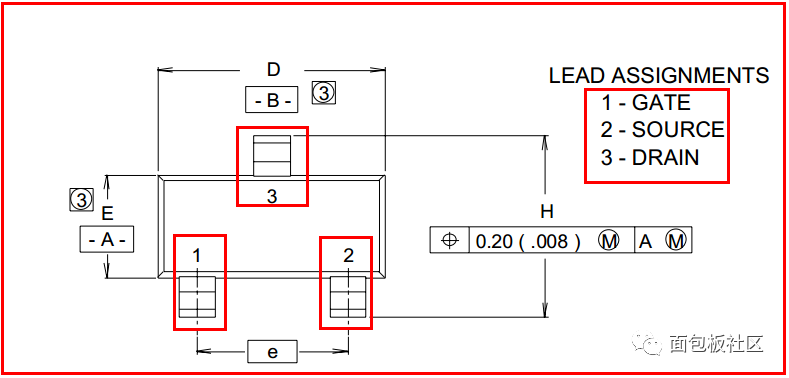

4.器件引脚排布

声明: 本文转载自其它媒体或授权刊载,目的在于信息传递,并不代表本站赞同其观点和对其真实性负责,如有新闻稿件和图片作品的内容、版权以及其它问题的,请联系我们及时删除。(联系我们,邮箱:evan.li@aspencore.com )

-

本次2025全球 MCU及嵌入式技术论坛,旨在汇聚行业精英,共同探讨MCU的最新技术、市场趋势和应用前景,为参会者提供全面而深入的行业洞察。国际电机驱动与控制技术论坛将聚焦于展示和探讨电机驱动与控制技术的最新进展及其在多个领域的应用,汇集全球知名企业和专家学者,为电机行业的未来发展提供宝贵的见解和方向。同期举行:国际AI+IoT生态发展高峰论坛,暨2025年度AIoT创新奖颁奖典礼。立即报名>>>

-

电感器是由电线线圈组成的设备,包裹在磁性材料上...

-

滤波器的使用,使得特定频率的信号能够被过滤掉。在上篇滤波器文章中,小编对滤波器的主要参数有所阐述。为增进大家对滤波器的认识,本文将对滤波器的主要分类,以及滤波器的使用注意事项予以介绍。如果你对滤波器...

-

ups电源是生活中的常用电源类型之一,对于ups电源,很多朋友其实都有所了解。为增进大家对ups电源的认识,本文将基于两点介绍ups电源:1.ups电源使用注意事项,2.ups电源维修技巧。如果你对ups电源具有兴趣,不妨继...

-

光耦,也就是光耦合器,在电路中应用广泛。上篇文章中,小编介绍了光耦的技术参数,但这只是理论部分。如果想要掌握光耦的应用,还需自己动手尝试。为增进大家对光耦的认识,本文将介绍光耦的实用技巧。如果你对光...

-

逆变器无疑是工业应用中常用的转换器之一了,对于逆变器,我们或多或少具备一定的了解。为增进大家对逆变器的了解,本文将对影响逆变器寿命的因素予以介绍。如果你对逆变器相关内容具有兴趣,不妨同小编一起继续往...

-

信息时代的到来极大地改变了人类社会的生产、生活、工作和学习方式。射频功率放大器不仅在通讯系统中得到广泛应用,还逐渐被应用于其他领域内。本文为一种新型射频导热治疗仪所设计的大功率射频放大器电路,满足工...

-

DHT11为 4 针单排引脚封装,如下图,采用单线制串行接口,只需加适当的上拉电阻,信号传输距离可达20米以上,使其成为各类应用甚至最为苛刻的应用场合的最佳选则。 二.传感器参数 1.DHT11电气参数如下: 型号 测量...

-

压力变送器作为测量仪器,是工业中最常用的传感器之一。上篇文章中,小编对压力变送器的种类有所阐述。为增进大家对压力变送器的认识,本文将对绝对压力变送器、绝对压力变送器的原理以及选型予以介绍。如果你对压...

-

继电器,虽是老生常谈的话题,但是却耐人寻味。本文中,小编将对继电器、继电器的主要作用予以阐述。此外,小编还将介绍高频继电器的工作原理、高频继电器的特点和高频继电器的结构。如果你对继电器具有兴趣,不妨...

-

CMOS在电路中具有重要作用,大家对于CMOS通常较为耳熟。但是,大家对于CMOS却未必十分了解。为增进大家对CMOS的认识,本文将对CMOS相关知识予以详细介绍。如果你对本文内容具有兴趣,不妨继续往下阅读哦。 CMOS(Co...

-

-

0

0