理解图腾柱TCM中负电流幅度和延时时间:优化数据存储与传输的关键技术!

电路一点通

400浏览

0评论

0点赞

2023-09-19

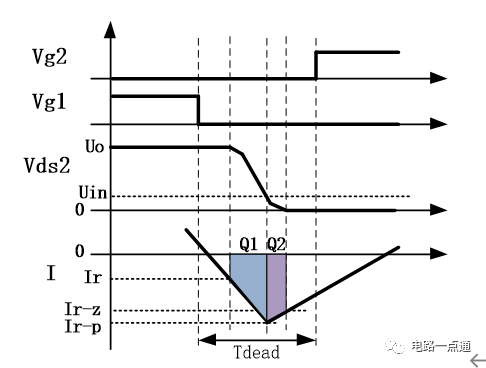

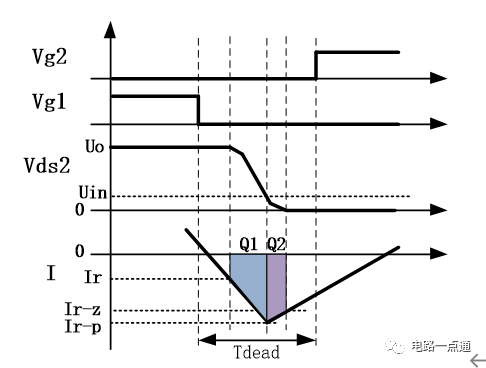

根据理论分析,不同的交流输入电压时,可以实现ZVS的最小负电流幅度是不同的。当输入电压小于输出母线电压的一半(Uin <1/2Uo)时。由于电感电流上升和下降的斜率配合,即使没有负电流(Ineg=0),仍然可以实现主功率管的ZVS。如下图1所示。 图 1输入电压小于母线电压一半的情况下

图 1输入电压小于母线电压一半的情况下

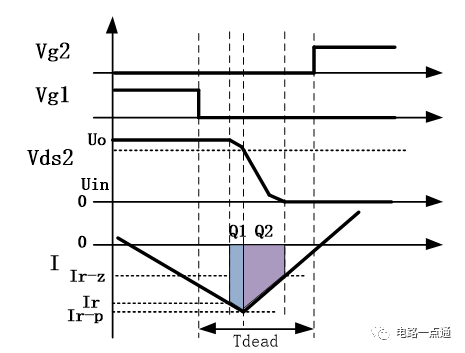

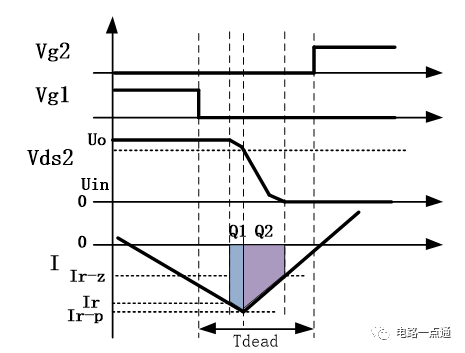

当输入电压大于输出母线电压的一半(Uin >1/2Uo)时。由于电感电流上升和下降斜率的不同,实现ZVS的最小负电流是变化的。如下图2所示。 图 2 输入电压大于母线电压一半的情况下

图 2 输入电压大于母线电压一半的情况下

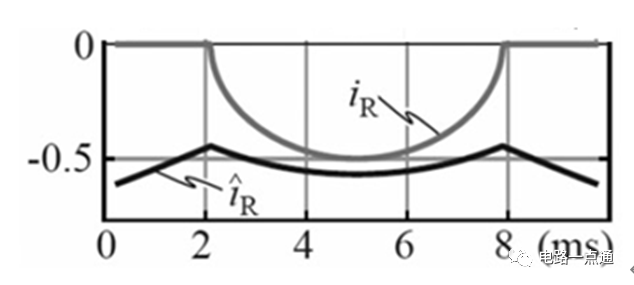

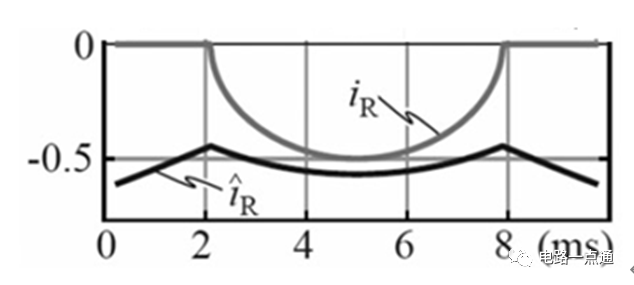

根据Kolar的文献,其实现ZVS的最小负电流满足下图3所示的曲线。 图3 实现ZVS的最小负电流的曲线

图3 实现ZVS的最小负电流的曲线

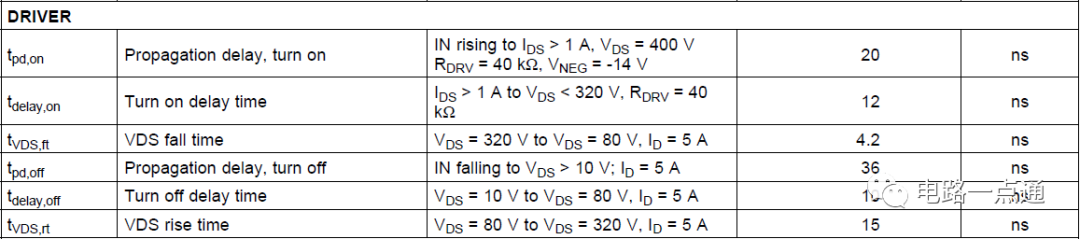

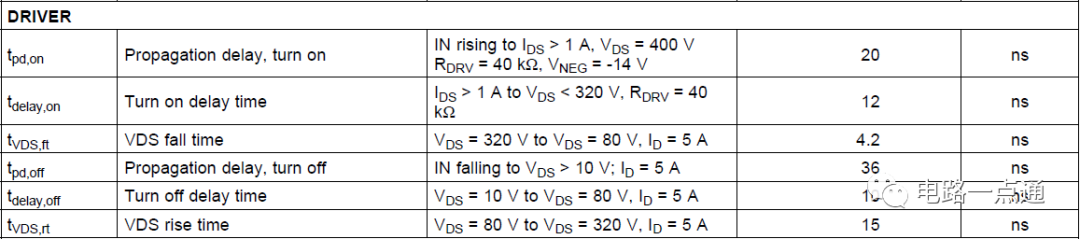

但实际工程处理,需要简化此控制策略。目前的实际工程样机的调试过程中,是采用固定负电流幅度的方法,可以设置为-1.5A~-2.5A都可以较好的ZVS效果。缩小电路的相应延迟时间TCM控制的工作原理决定了其硬件电路的触发信号及DSP控制响应不能有太长的时间延迟,太长的响应延时会导致Tr过长,从而导致负电流过大问题,降低PFC工作效率及控制问题。因此,对于电感电流采样电路、电感电流ZCD电路及DSP响应时间都有很严格时间要求。A、为了满足CCM控制情况下的控制效果,分流器采集的电流信号经过一级高速运放放大,此运放选用了TI的45MHz高速运放OPA2211。考虑到目前电流采样通路采用的48Khz的低通滤波器,后续降成本可以优化该器件。B、过零信号的比较器也需要选用高速的,目前选用的是TI的两通道高速比较器TLV3502。其延迟时间为小于10ns。C、如高频管使用MOSFET,驱动IC选用低延迟时间的SI8233,其延迟时间也不超过100ns。而使用TI GAN器件LMG3410RWHR,其内部驱动延时也非常的低。

D、降低DSP的响应延迟时间。DSP的响应速度在进行ZCD及Tr控制时非常关键.

@电路一点通

声明: 本文转载自其它媒体或授权刊载,目的在于信息传递,并不代表本站赞同其观点和对其真实性负责,如有新闻稿件和图片作品的内容、版权以及其它问题的,请联系我们及时删除。(联系我们,邮箱:evan.li@aspencore.com )

-

在线直播意法半导体“在中国,为中国”战略,STM32最新产品、应用及生态;

STM32线上训练营带您玩转机械手直播:边缘AI及GUI软硬件开发特训,ST资深专家在线互动答疑。

-

-

目录电流采样方式低侧电流采样高侧电流采样高侧电流电路设计示例TI:40V~

-

-

-

-

文介绍了三相锁相环的基本原理及其在电力系统中的应用,特别是在输入信号频率突变时的锁相效果。

-

一、LDO概述在电压转换电路中,LDO和DC-DC电路是最常用的两种方式,本篇主要介绍LDO相关内容。

-

-

图1电路在今天可能吸引力没有那么大了,因为现在有了更先进的放大器,如LTC6268,同时兼顾了低电压噪声和低输入偏置电流。但了解一下也是非常值得的,甚至在一些应用里降成本时没准可以用到,比如色谱仪。

-

下面我们通过举例介绍一个晶振的规格书参数,来和大家分享下怎么选型一个合适的晶振,以及涉及到的部分计算内容。

-

可靠性设计就是选用在最坏的使用环境下仍能保证高可靠性的元器件的过程。

-

关注回复“加群”,加入硬件电子学习交流群。本期的电路图来自ZLinear的开源数据采集板卡DL8884_RFN,是一个比较常见的电压偏置采集法(电路图已取得作者授权发文)。

图 1输入电压小于母线电压一半的情况下

图 1输入电压小于母线电压一半的情况下 图 2 输入电压大于母线电压一半的情况下

图 2 输入电压大于母线电压一半的情况下 图3 实现ZVS的最小负电流的曲线

图3 实现ZVS的最小负电流的曲线

0

0