1、综合读写模块(无FIFO)

我们对SDRAM的各个功能进行了模块划分,学会了初始化操作、自动刷新操作、写操作、读操作与仲裁操作,结合这几个功能模块就能简单地实现SDRAM的读写功能了(突发方式)。

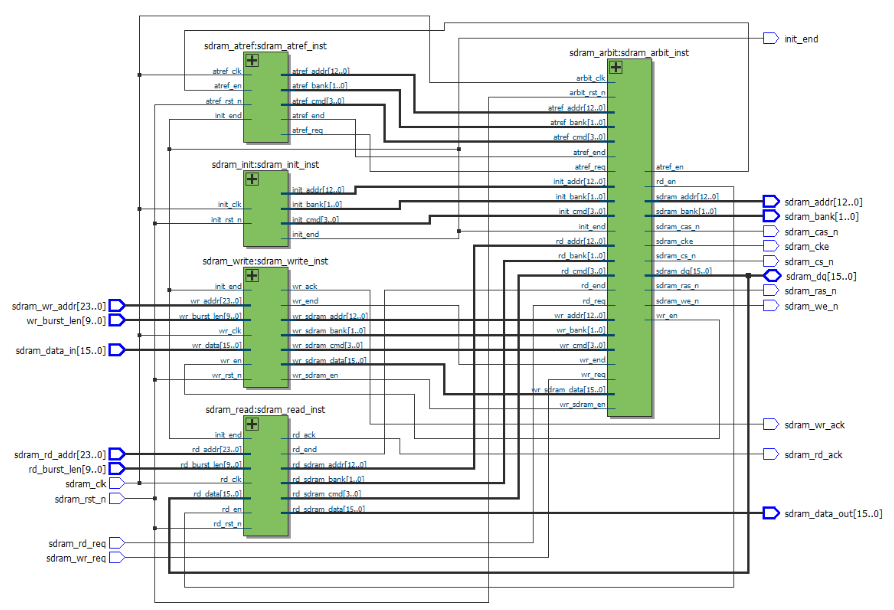

综合读写模块(无FIFO)的功能框图如下:

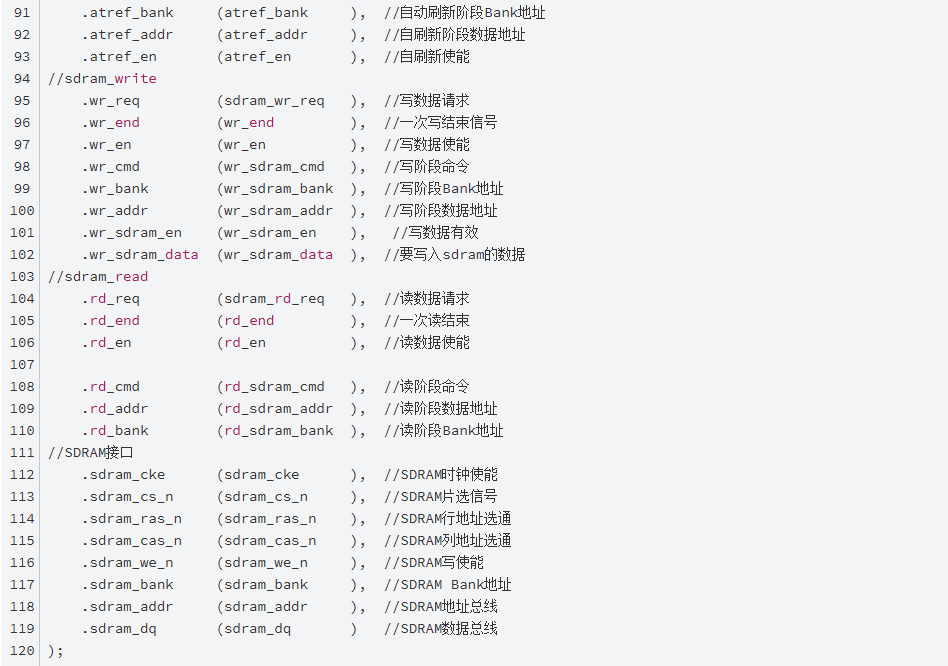

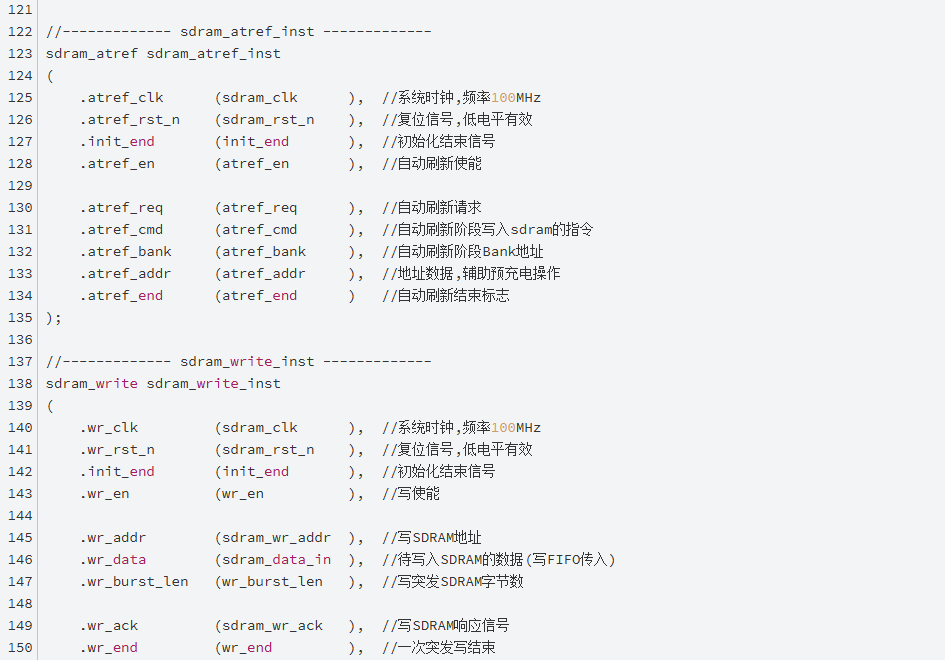

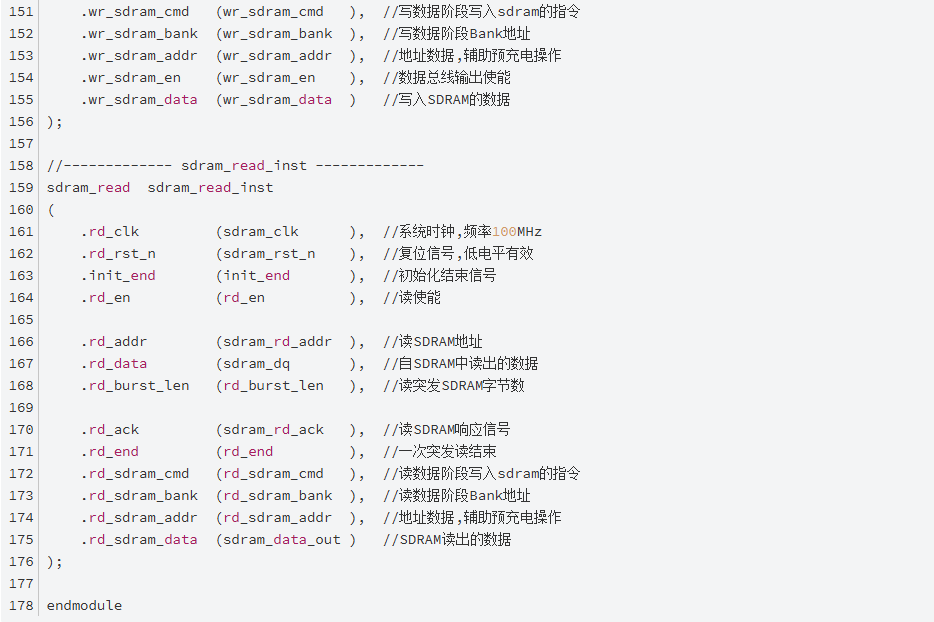

可以看到综合读写模块(无FIFO)sdram_ctrl就是例化了之前的几个功能模块。

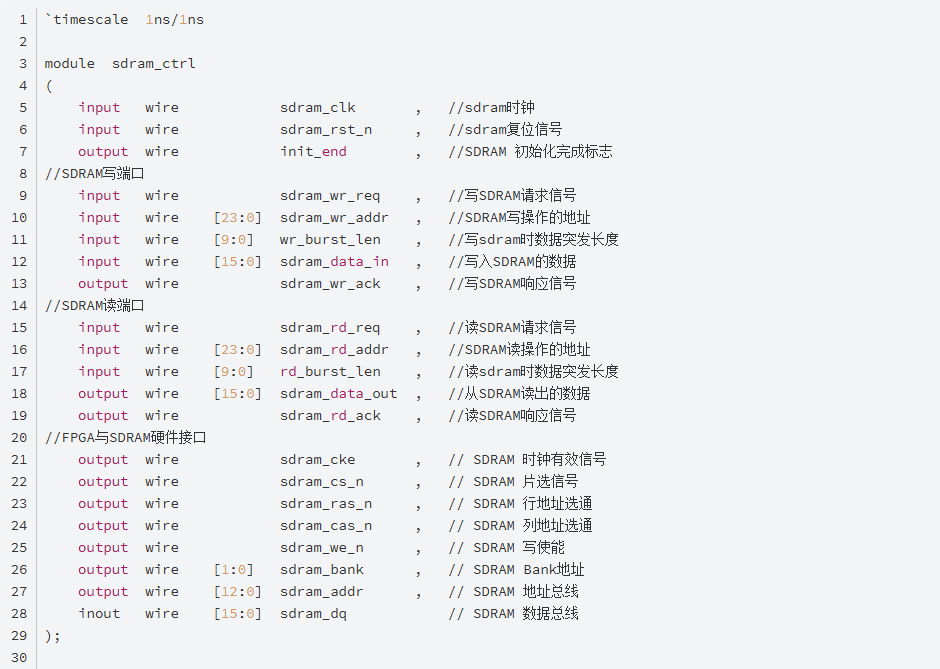

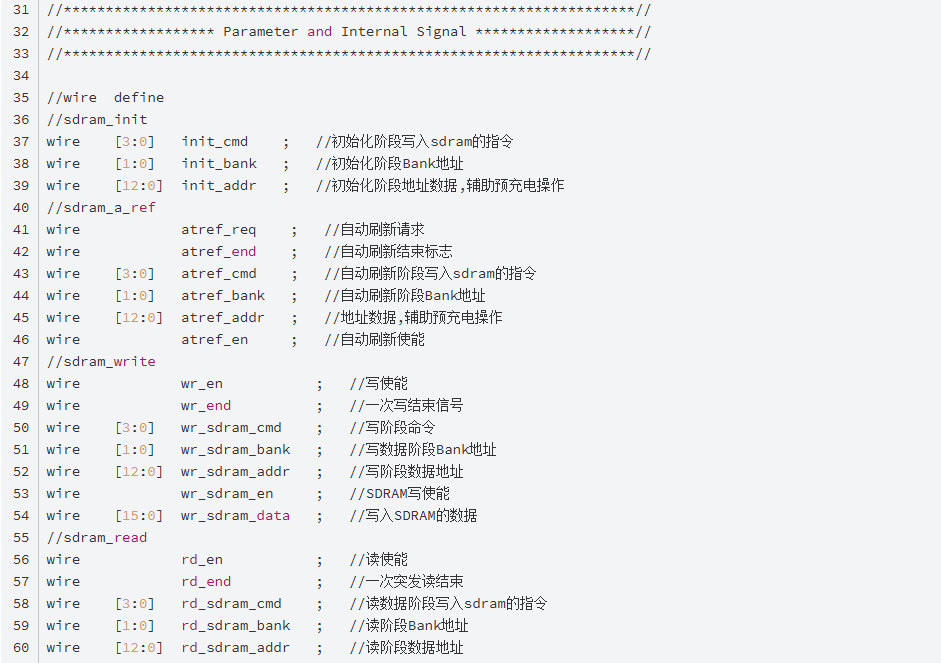

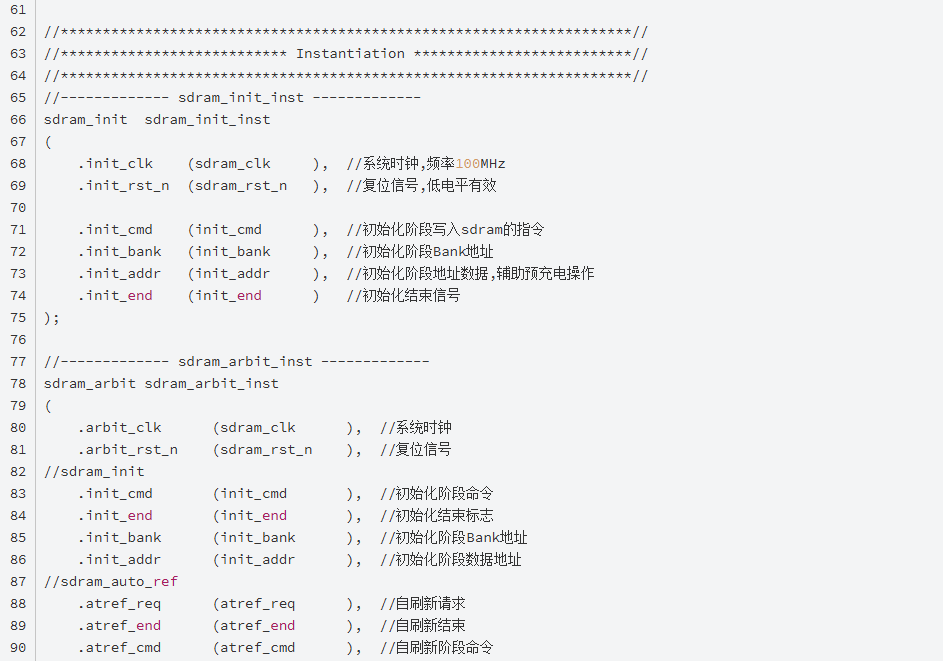

2、Verilog代码

根据上图的功能框图对功能子模块进行例化即可,如下(仅列出顶层模块,子功能模块请见该系列的其他博文):

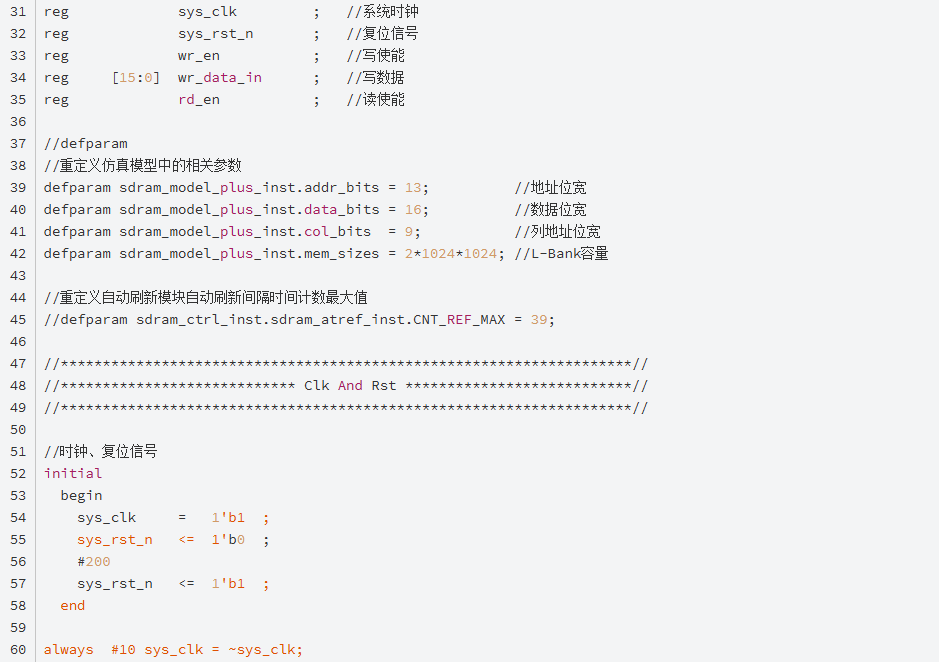

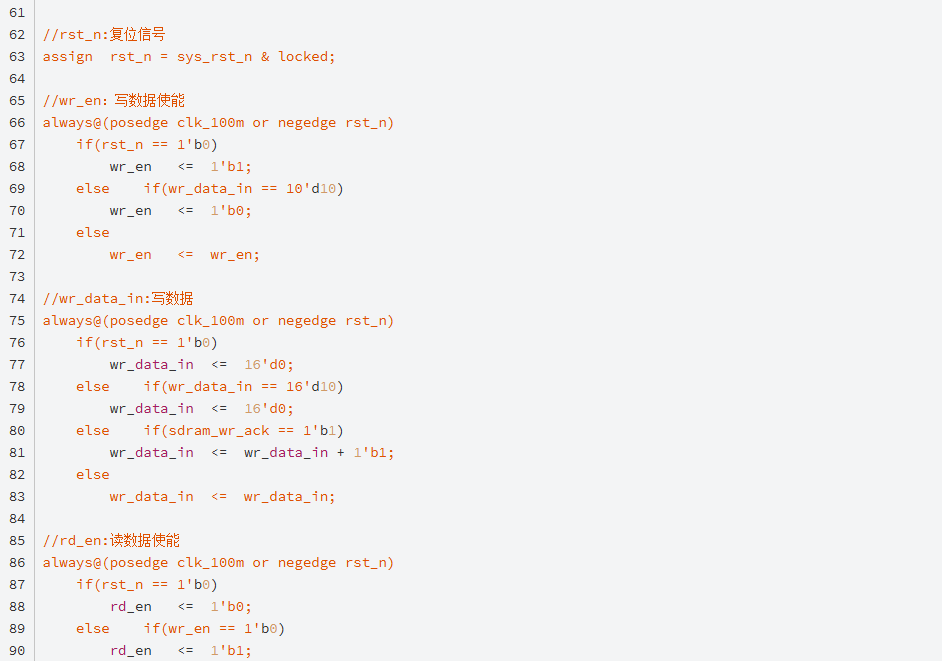

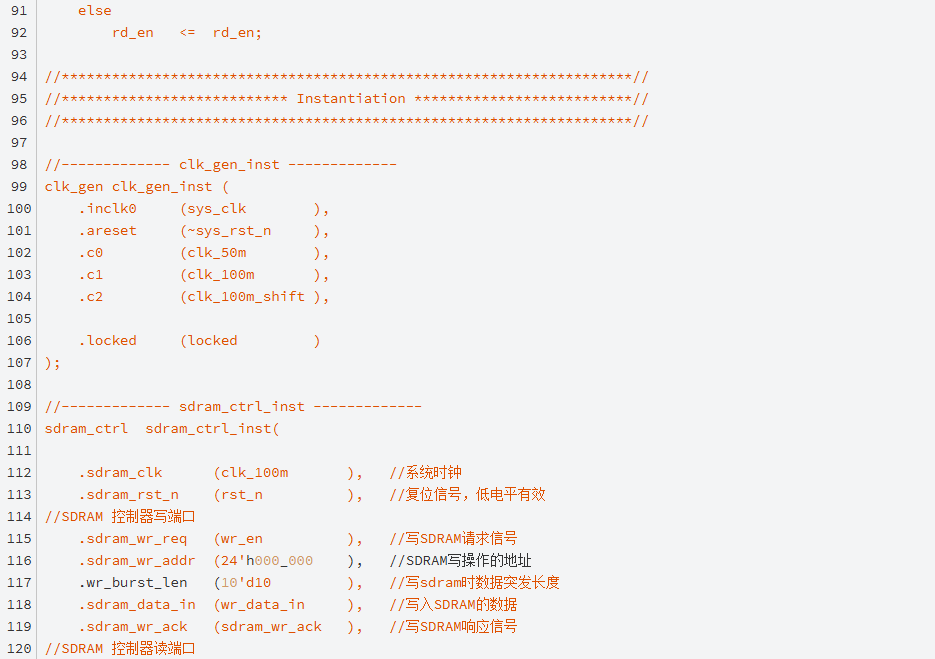

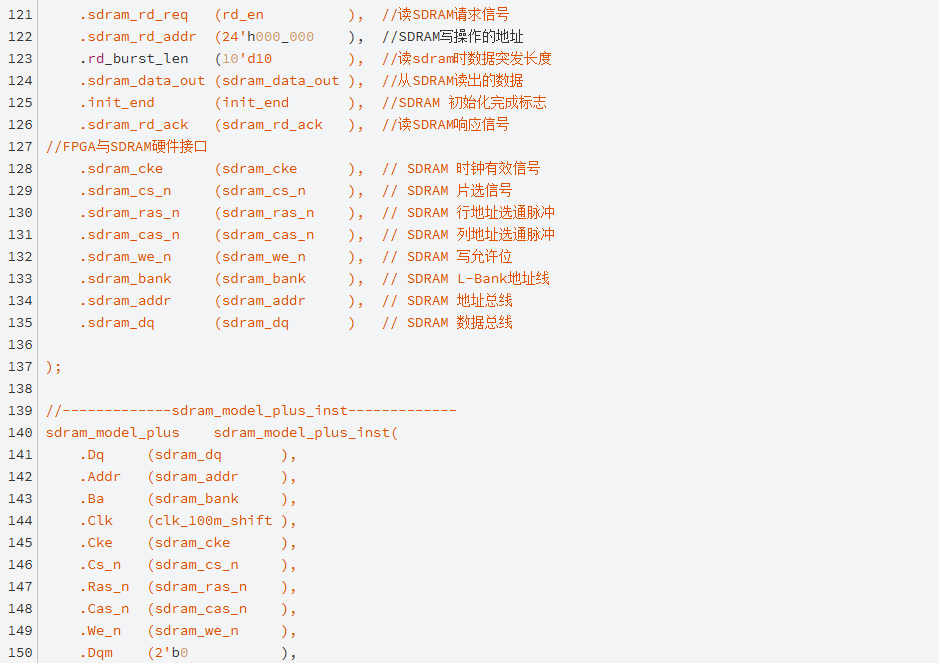

3、Testbench

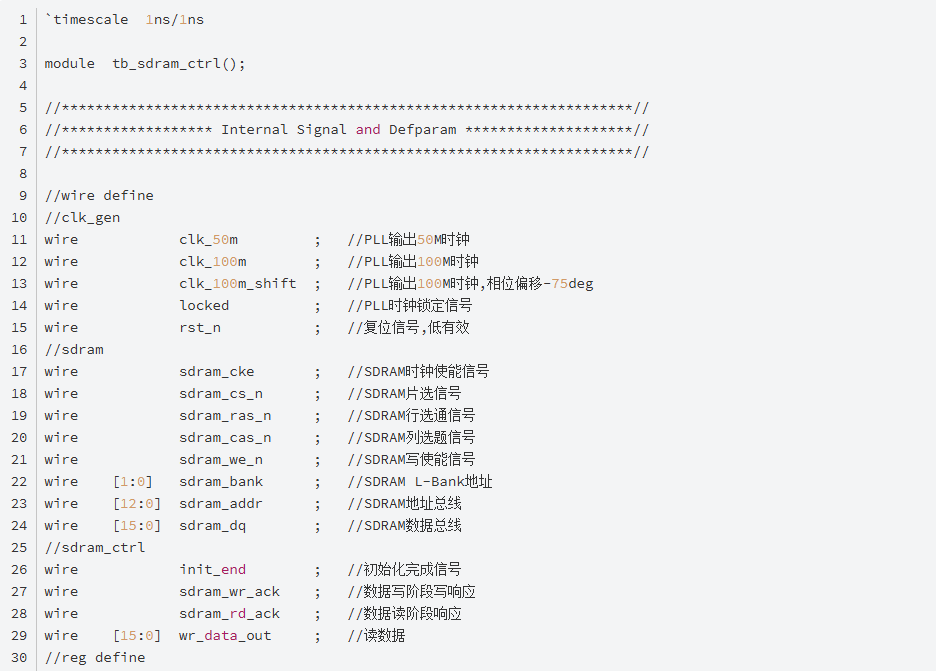

Testbench除了例化了之前编写的子功能模块外,还例化了一个PLL模块,分别输出50M、100M和相位偏移-30°的100M时钟信号。

该Testbench预期实现的功能为:

-

例化一个综合读写模块:突发读写,突发长度10,初始操作地址为24'h000_000

-

先从初始地址开始往SDRAM中写入10个数据,分别为1~10

-

然后一直对SDRAM的地址(24'h000_000~24'h000_009)这10个地址进行数据读取

该Testbench如下:

4、仿真结果

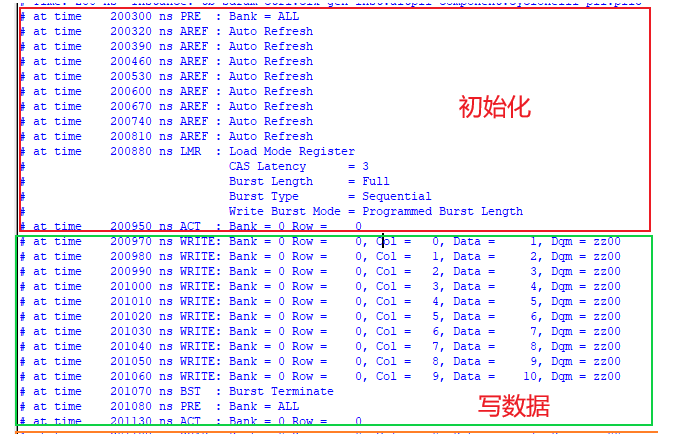

SDRAM 仿真模型打印信息如下:

-

首先进行了初始化操作

-

然后对地址0-9的10个存储单位分别写入数据1-10

-

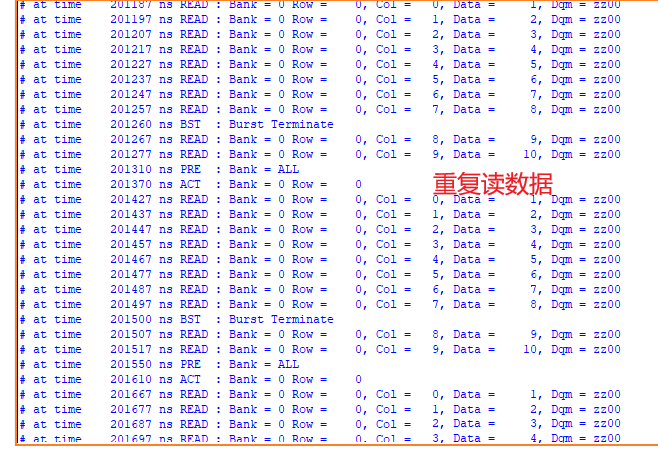

随后重复读取上一步写入的10个数据

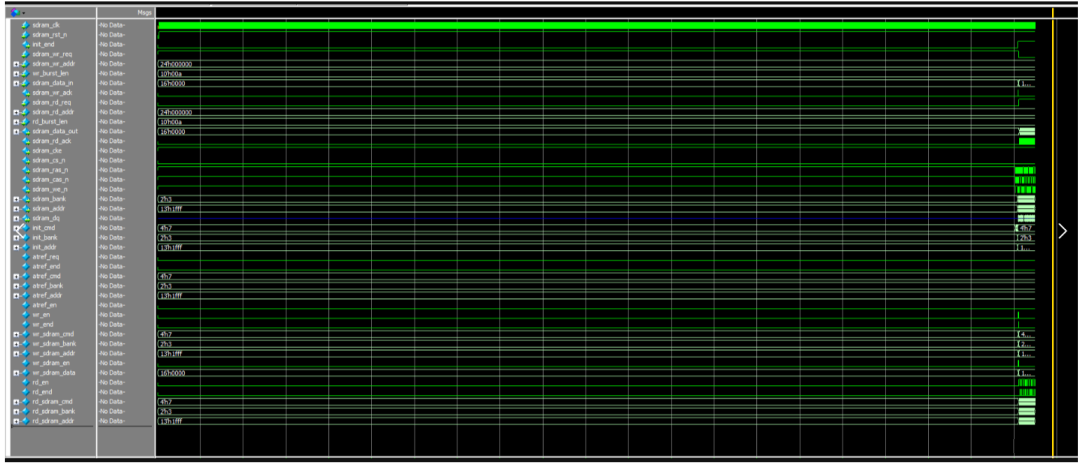

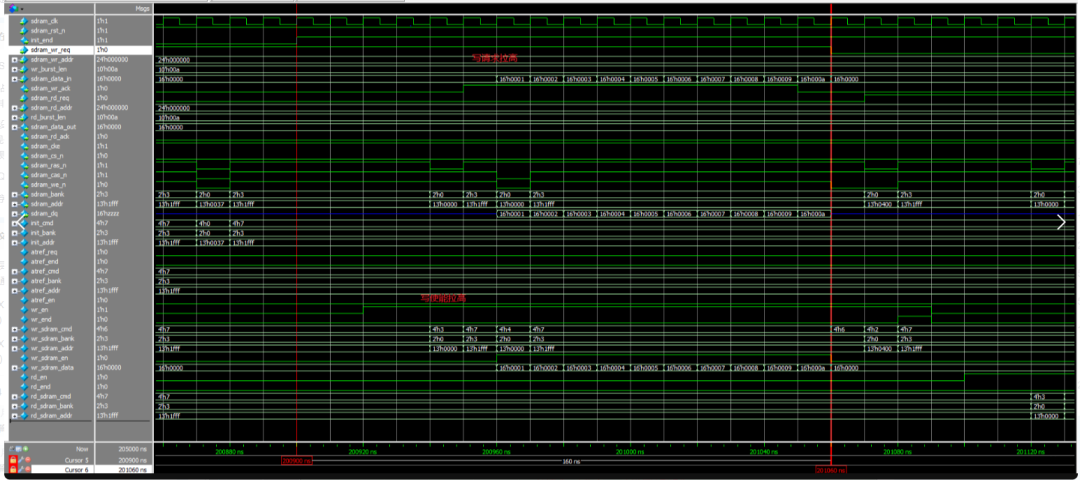

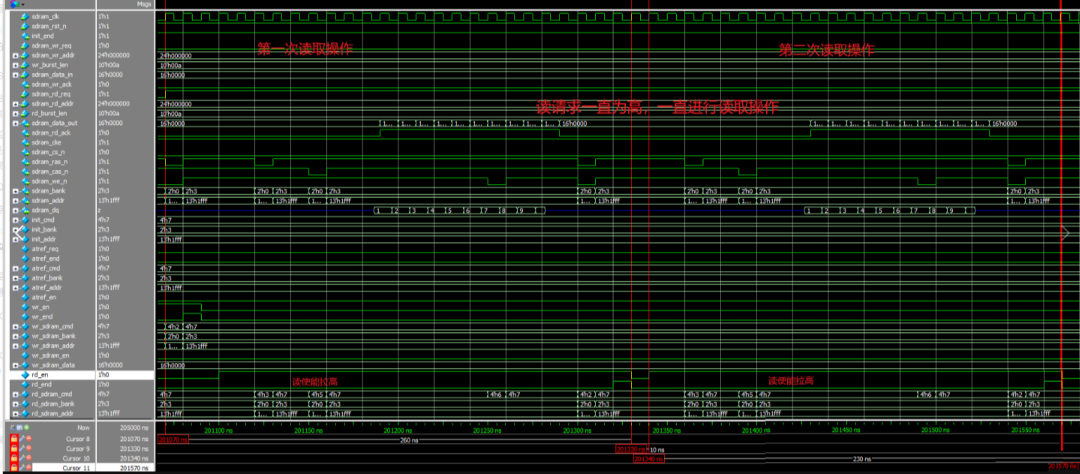

仿真结果如下图:

仿真结果截图的图较长,将其分解讲解:

上图各信号基本不变,且init_end信号(初始化完成信号)最后拉高,说明此阶段为初始化阶段。

上图已经完成了初始化,先拉高了写请求信号,2个周期后写使能信号拉高,开始往SDRAM写了数据。从数据线sdram_dq上可以看到写入的数据分别为1-10。

上图中读请求信号一直为高,代表在重复进行读取操作,而我们也捕捉到了两次读取操作(限于篇幅,后续读取操作不截图);当读请求为高且写请求为低时,仲裁模块响应了读取操作,拉高了读使能,对SDRAM进行读取操作,从数据线sdram_dq上可以看到读取的数据分别为1-10。

5、其他

上文成功实现了SDRAM综合读写模块(无FIFO),我们在仿真验证时通过对SDRAM写入10个数据,并将其读出,比对读写数据是否一致来验证SDRAM综合读写模块(无FIFO)是否能实现预期功能。

该模块虽然能实现预期功能,但是同时存在以下不足需要解决:

-

调用该模块的其他模块必须与此模块时钟同步,否则将引入跨时钟域传输的问题

-

虽然仲裁模块可以解决读写请求、刷新请求的冲突,但是在存在冲突时,无法将冲突数据缓存会造成数据丢失(例如写操作、刷新操作冲突。则必定会执行刷新操作后再执行写操作,而在等待刷新操作完成的这段时间可能会将原来要写入的数据覆盖)

XNM-6VP高速存储卡

新品推荐

XNM-6VP 是一款基于KU115高性能FPGA的高速存储模块。支持高速缓存 16GB DDR4 SDRAM, 容量最高可达32TB的固态硬盘存储。支持RAID5/6/10,读写速率最高可达10GBps,支持专门为高速实时记录而设计的自定义文件系统。

该模块基于NVME固态硬盘,主要用于高速实时数据流的存储和回放,主要用于雷达、通信、电子、卫星等领域,包括高速ADC数据采样实时记录、DAC数据回放、基于光纤或者Rapid IO的高速数据记录等场景。

• 标准6U VPX架构模块;

• 最多支持8块NVME SSD;

• 支持8TB/16TB/32TB 三种规格;

• 支持标准文件系统;

• ExFAT标准文件系统;

• 实时记录功能;

• 文件在线管理;

• 自检与故障检测;

• 持续稳定记录带宽 ≥8GB/s;

• 持续稳定读取带宽 ≥8GB/s

0

0