1、介绍

IBUFDS原语、OBUFDS原语以及IOBUFDS都是差分信号缓冲器,用于不同电平接口之间的缓冲和转换。IBUFDS 用于差分输入,OBUFDS用于差分输出,IOBUFDS用于三态形式的差分信号。

那什么是差分信号呢?简单来说,差分信号就是用两根线来传输信号,二者极性相反,但是赋值相同,信号接收端比较这两个电压的差值来判断发送端发送的逻辑状态。差分信号最大的特点就是抗干扰能力强,假如传输过程有干扰,那么干扰也会同时存在于两条信号线上,因为信号结果来自于两条线的差值,所以这个扰动就会被抵消掉。

一些高速接口都是采用的差分信号的形式,比如USB,HDMI,以太网,LVDS等等。

2、IBUFDS

2.1、理论

IBUFDS是差分输入缓冲器,支持低压差分信号(如LVCMOS、LVDS等)。在IBUFDS中,一个电平接口用两个独特的电平接口(I和IB)表示。一个可以认为是主信号,另一个可以认为是从信号。两个端口的信号极性必须相反才能正常工作,输出端O将输入的差分信号转换为单端信号输出。

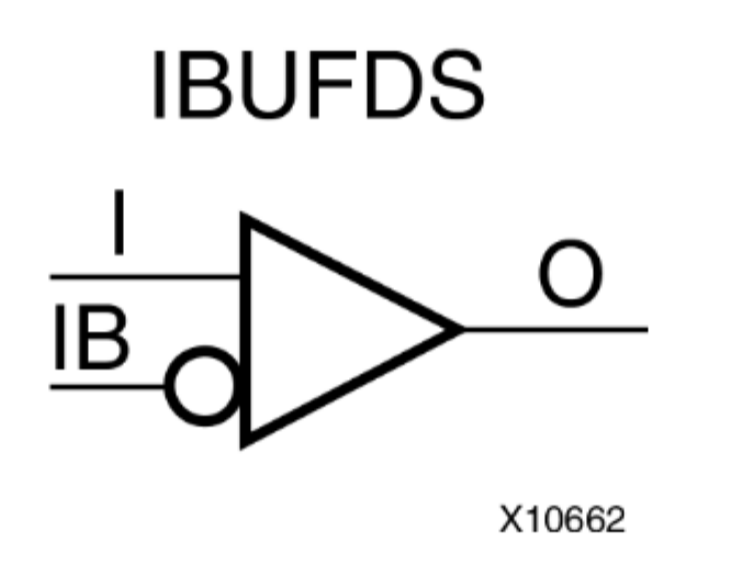

IBUFDS原语示意图如下所示:

端口说明如下表:

信号真值表如下:

2.2、仿真

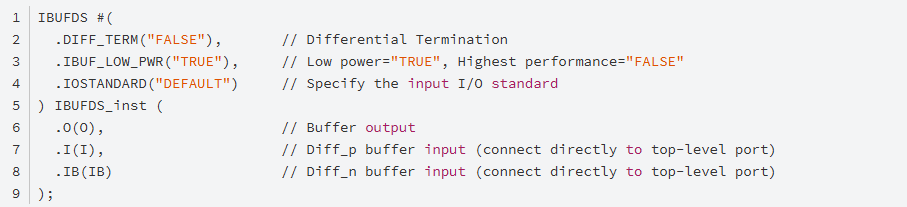

打开VIvado--Tools--Language Templates,搜索“IBUFDS”,可以找到Xilinx提供的模板,如下所示:

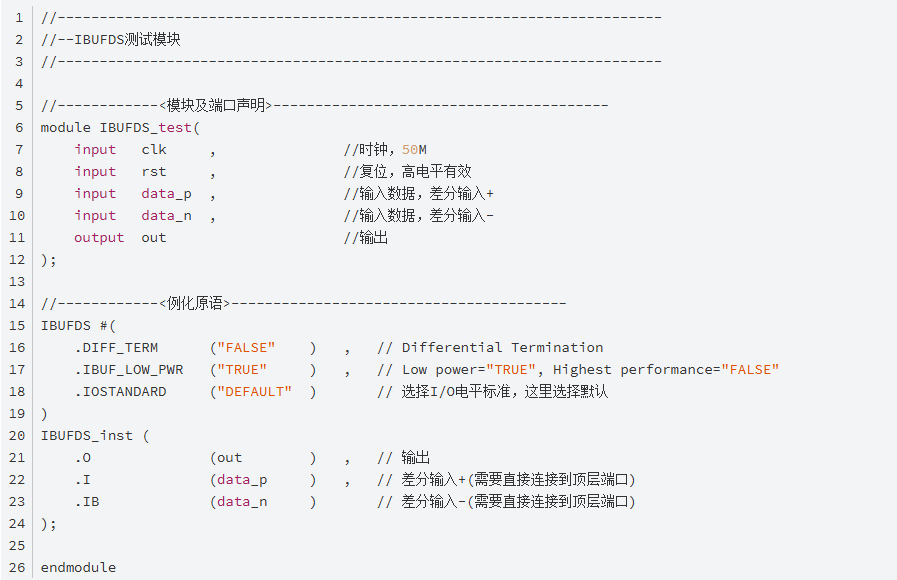

DIFF_TERM、IBUF_LOW_PWR分别指定差分终端和性能模式,IOSTANDARD指定你需要输出的电平标准。接下来例化一个IBUFDS原语进行测试,Verilog代码如下:

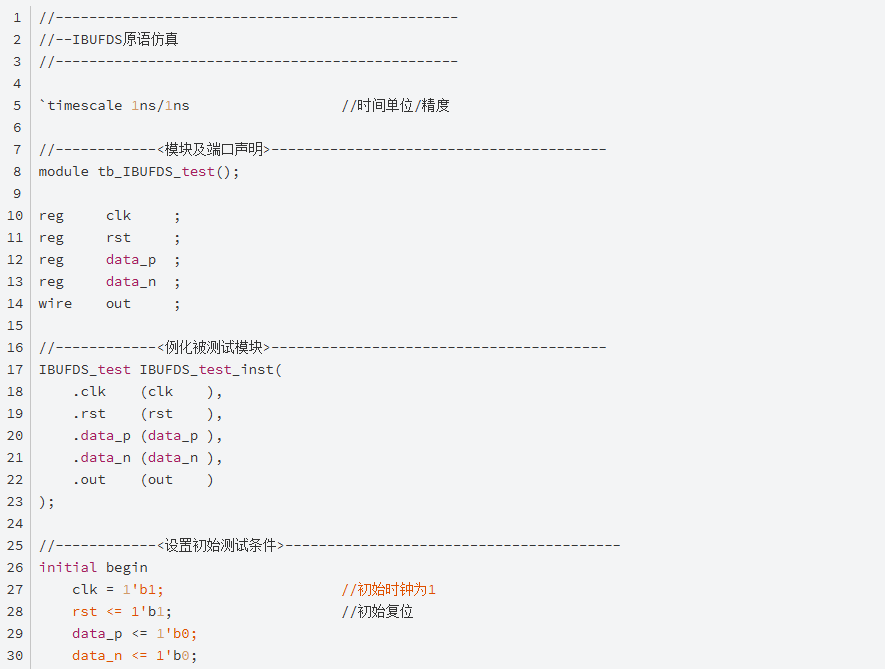

每隔20ns分别随机生成2个1位2进制数据作为差分输入,观察输出,Testbench如下:

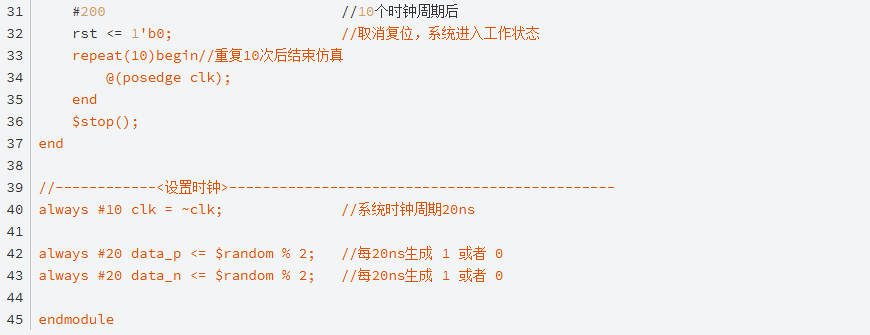

仿真结果如下:

每隔20ns,2个差分输入端口分别随机生成2个1位2进制数据,输出输入符合上述的真值表。

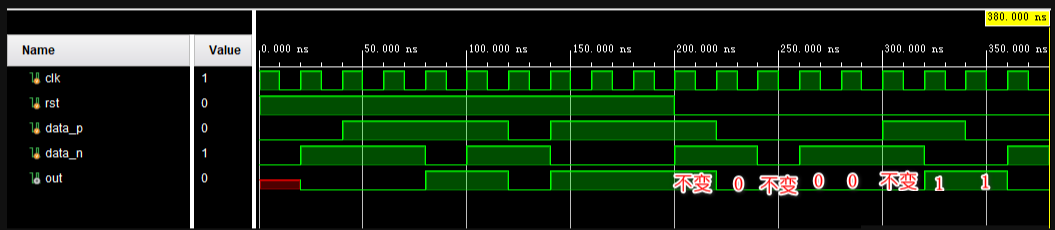

通过仿真可以知道逻辑实现,但是FPGA是如何实现差分输入和输出的呢?将上述工程综合、实现,查看信号在芯片中的走线及布局。

可以看到,相邻的两个管脚R6、R7分别是差分输入的+端和-端,两个差分信号进来FPGA后,通过IBUFDS转换成了单端信号。R6、R7这两个相邻的管脚即可以单独使用,也可以配置成差分信号一起使用,从PACKAGE界面也可以看出来,R6/R7是一对差分管脚:

3、OBUFDS

3.1、理论

OBUFDS 是差分输出缓冲器,用于将来自 FPGA 内部逻辑的信号转换成差分信号输出,支持 TMDS、LVDS等电平标准。它的输出用O和OB两个独立接口表示。一个可以认为是主信号,另一个可以认为是从信号。

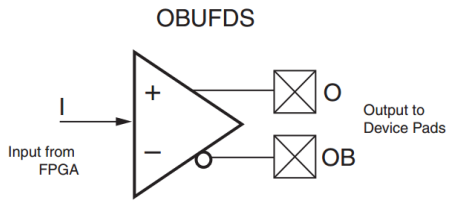

OBUFDS原语示意图如下所示:

端口说明如下表:

信号真值表如下:

可以看出,输出+端与输入一致,输出-端与输入相反。

3.2、仿真

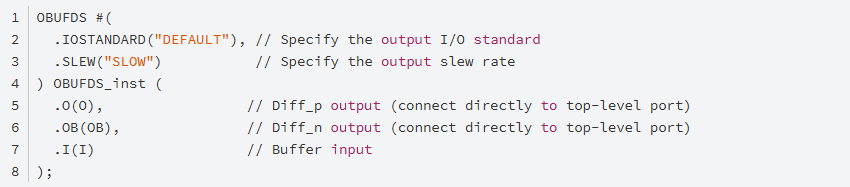

打开VIvado--Tools--Language Templates,搜索“OBUFDS”,可以找到Xilinx提供的模板,如下所示:

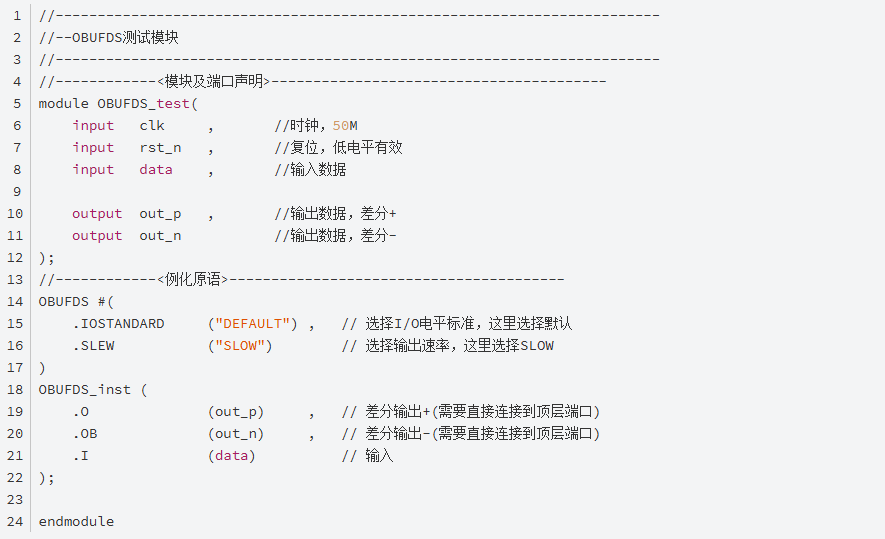

其中IOSTANDARD指定你需要输出的差分电平标准,SLEW根据你的要求输出FAST或者SLOW。接下来例化一个OBUFDS原语进行测试,Verilog代码如下:

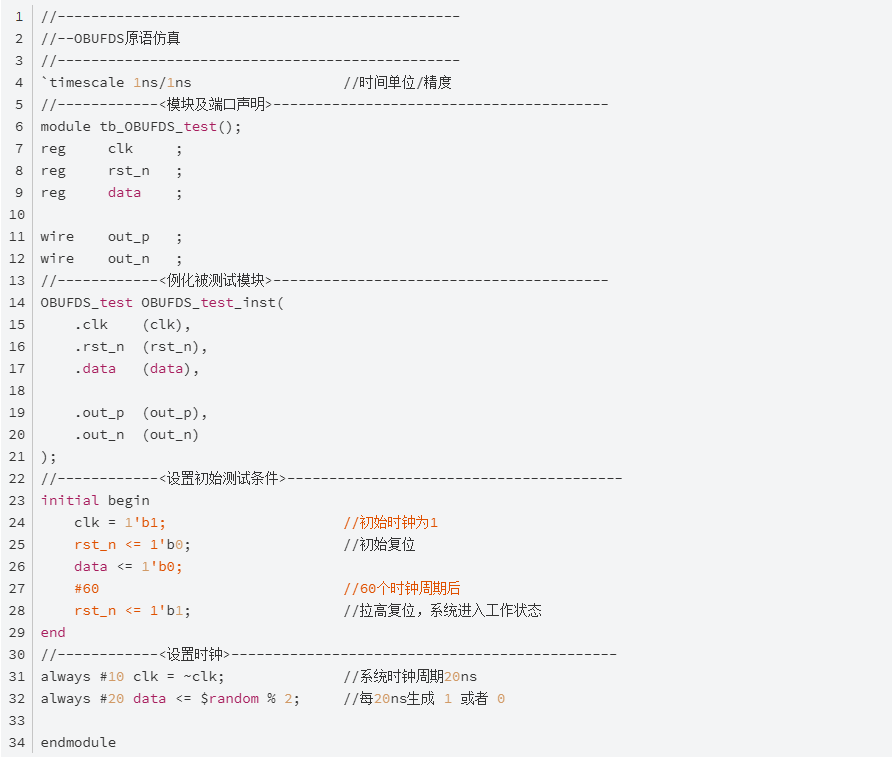

每隔20ns随机生成一个1位2进制数据,观察差分输出,Testbench如下:

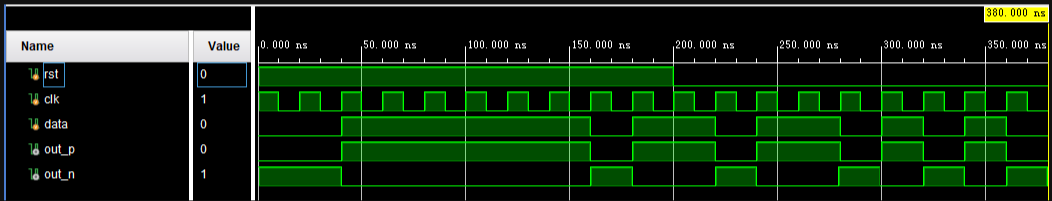

仿真结果如下:

每隔20ns,data随机生成0或者1,out_p与输入一致,out_n与输入相反,差分输出信号符合上述的真值表。

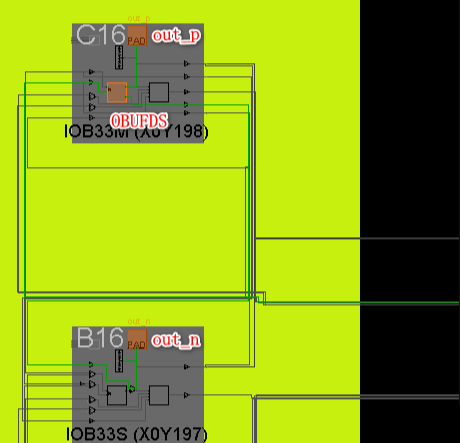

将上述工程综合、实现,查看信号在芯片中的走线及布局:

可以看到,相邻的两个管脚C16/B16分别是差分输出的+端和-端,信号从FPGA通过OBUFDS以差分形式输出到外部,转换成了差分信号。

4、IOBUFDS

4.1、理论

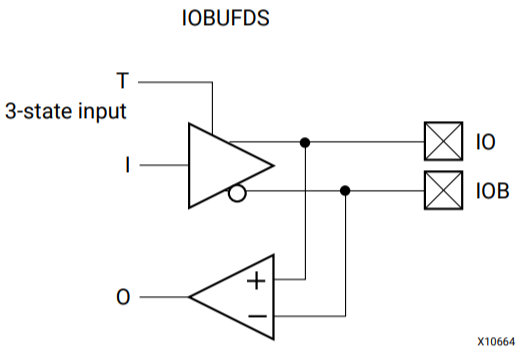

除了单向的差分信号外,也可以利用三态差分转换器件IOBUFDS实现双向差分转换,对应的框图如下所示,T是三态的使能信号,低电平有效。T为低电平时,I作为FPGA输出的单端信号,IO和IOB作为转换后的差分输出引脚。当T为高电平时,三态门关闭,此时IO作为差分输入的正极,IOB作为差分输入的负极,O作为差分输入转换后的单端输入信号。

端口说明如下表:

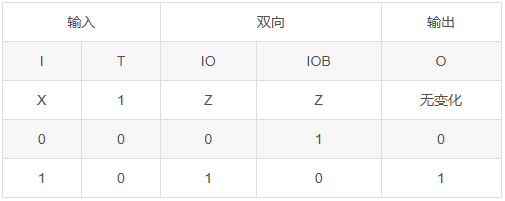

信号真值表如下:

4.2、仿真

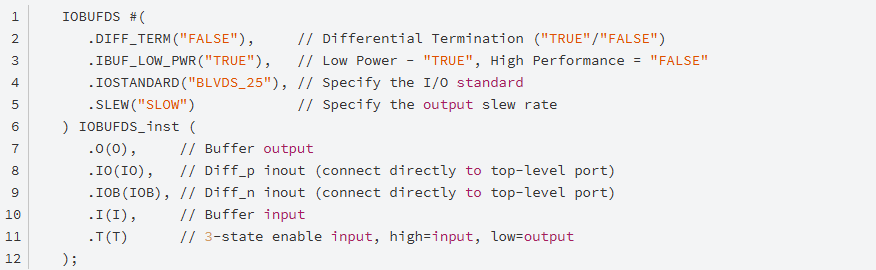

打开VIvado--Tools--Language Templates,搜索 “IOBUFDS”,可以找到Xilinx提供的模板,如下所示:

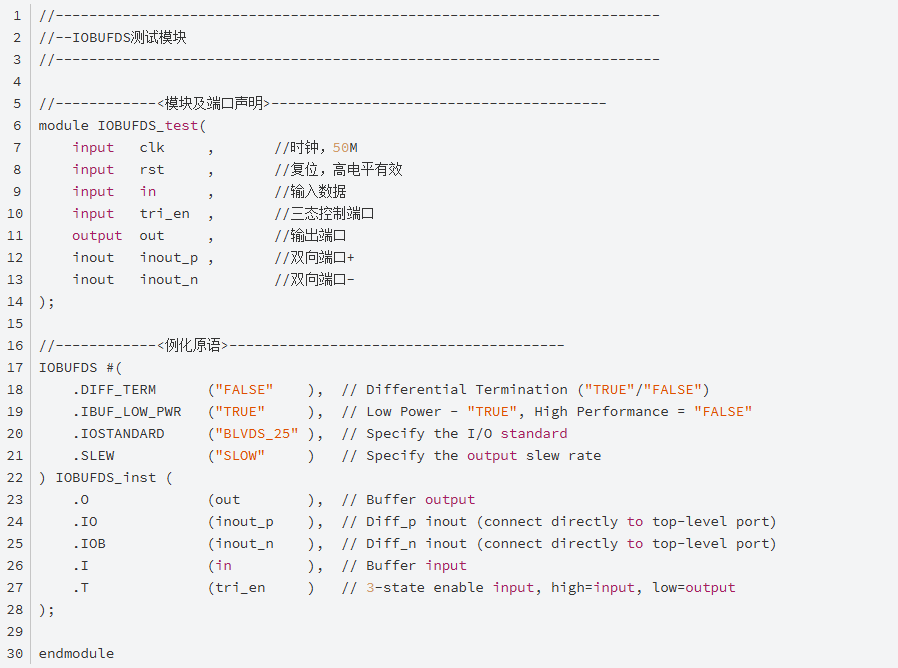

接下来例化一个OBUFDS原语进行测试,Verilog代码如下:

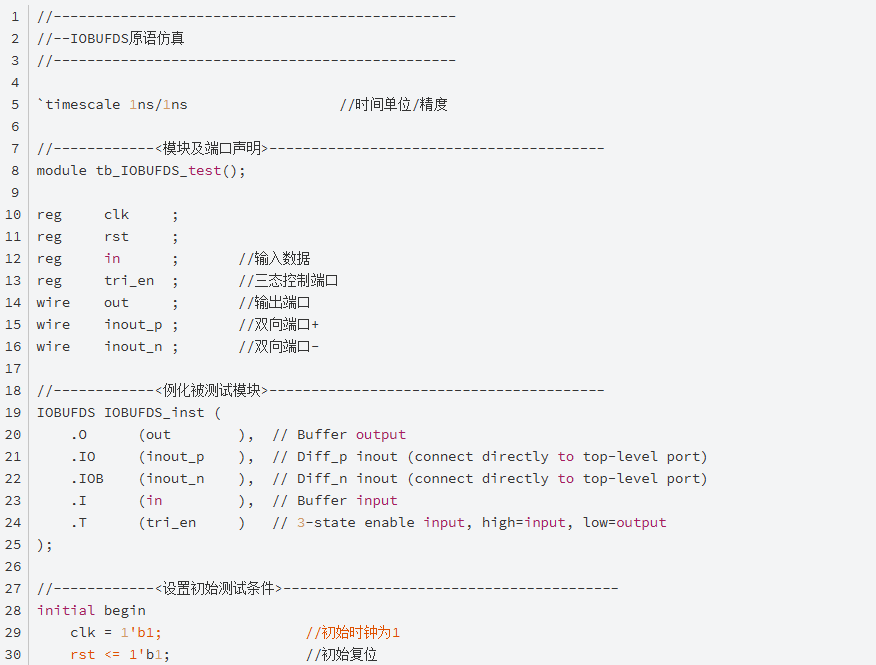

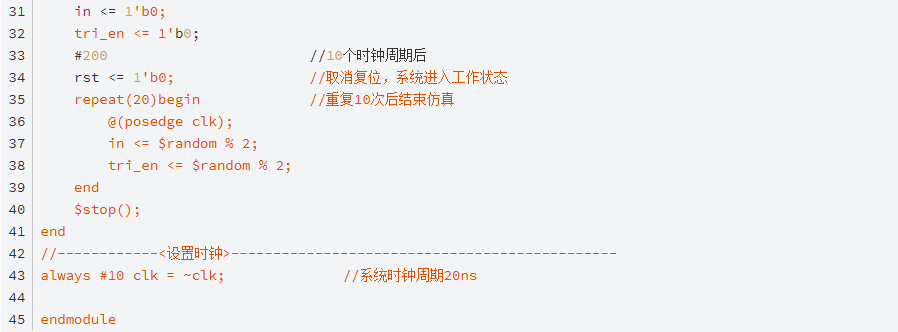

每隔20ns随机生成三态控制信号和输入信号,观察输出,Testbench如下:

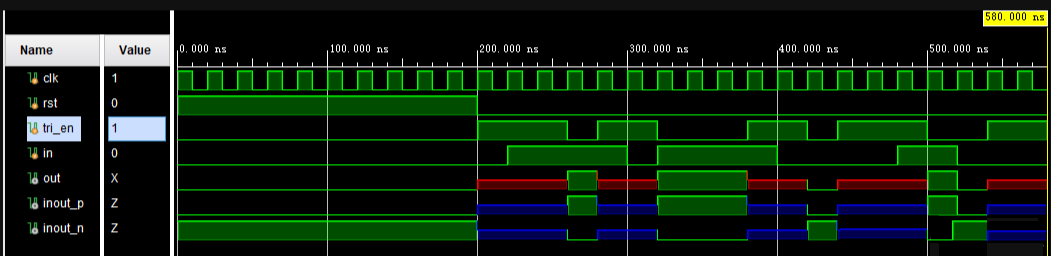

仿真结果如下:

当三态控制位高电平时,此时输出为高阻态;当三态控制位低电平时,此时输出等于输入,更准确地说,是p端和输入一致,n端和输出相反。将上述工程综合、实现,查看信号在芯片中的走线及布局:

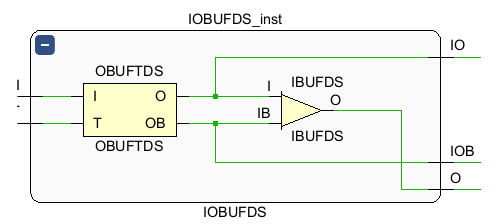

实际上IOBUFDS是由两部分组成:OBUFTDS+IBUFDS,其中的OBUFTDS实现输入高阻功能,IBUFDS把两个差分信号组成成输出O。

0

0