LUT,全称Look Up Table,查找表。目前主流FPGA实现的是6输入查找表。这里我们以4输入查找表为例,解释一下FPGA如何使用LUT表实现组合逻辑。

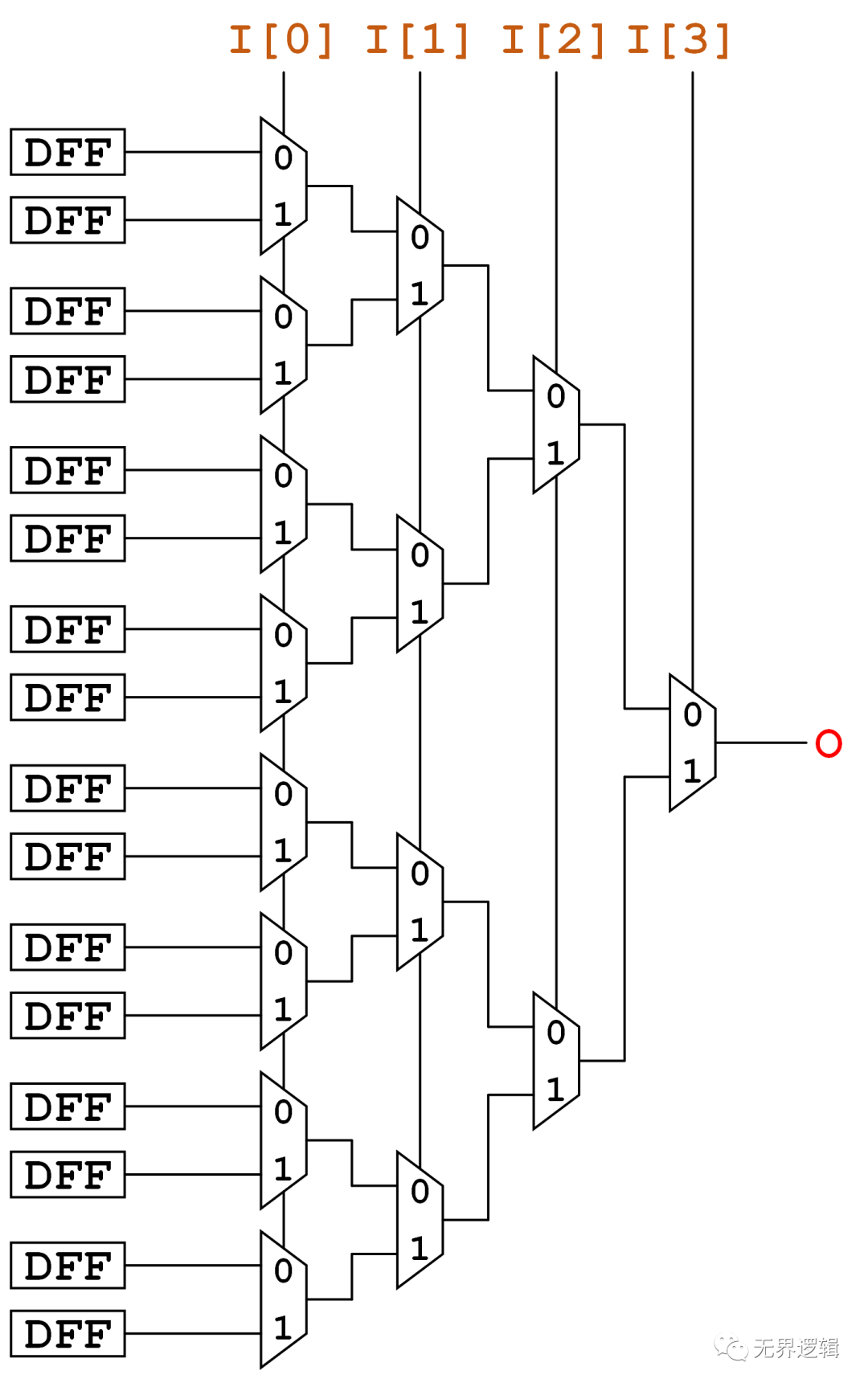

如上图所示,4输入查找表,包含4个输入端口I[3:0],包含一个输出端口O,还包含存储初始值的16个DFF触发器。

可以看到四个输入信号,实际上是4级选择器。每个输入位会控制一列选择器的选择。如I[0]值为0,则选通,第一级选择器的上通路。如I[0]值为1,则选通,第一级选择器的下通路。

I是4bit的二进制,其构成的输入的值一共有16种情况。这里每个输入值,对应一个DFF。我们提前把值对应的输出值初始化在DFF内。这样就构建了一张16X1的表格。根据输入值,选择某个DFF输出到O端。进而实现了4输入的所有逻辑组合。

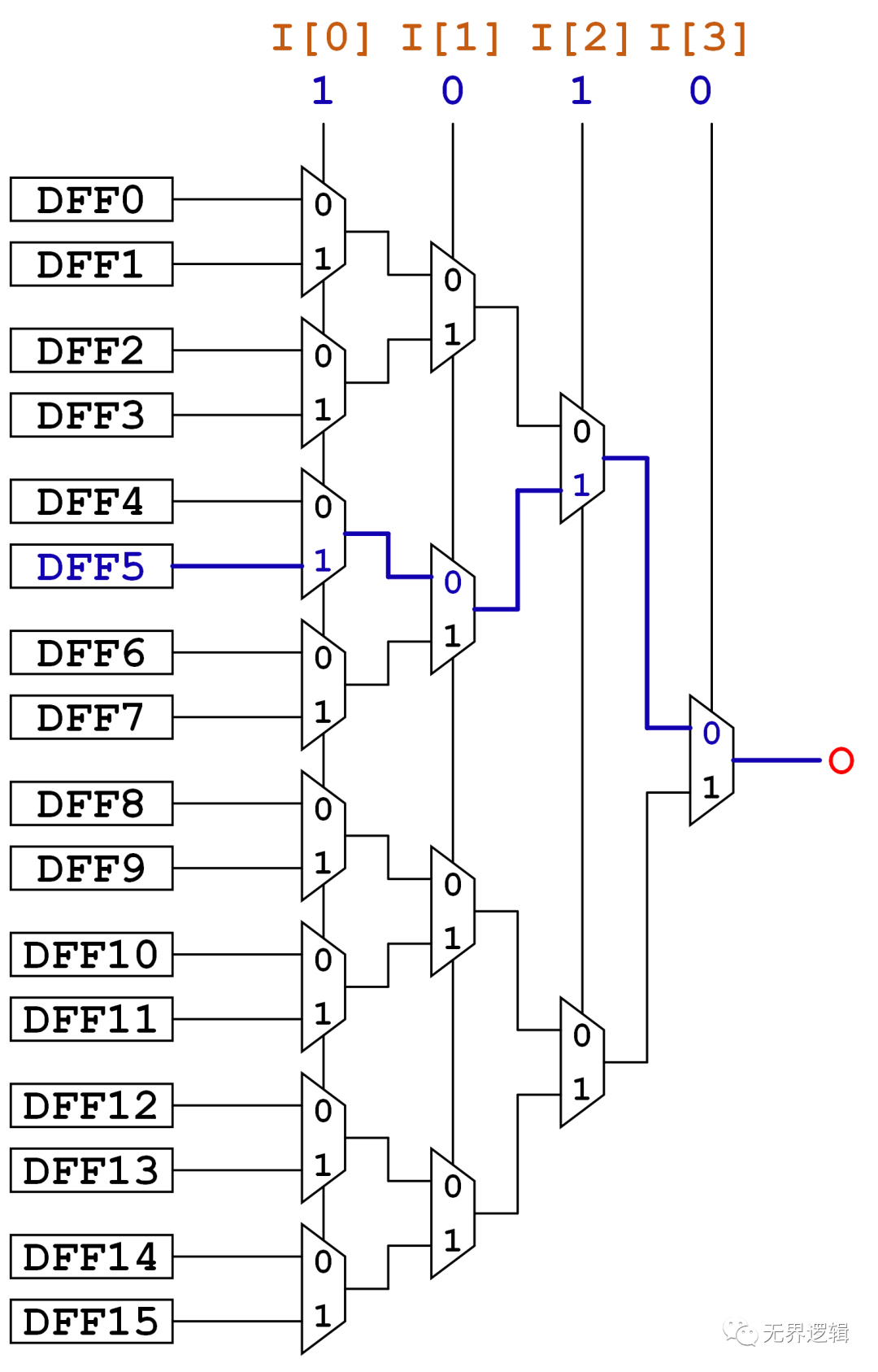

举例:I[3:0]=4'b0101,其对应的选择通路为:

我们可以直接使用Verilog语言描述LUT表。代码片段来自:Vivado Design Suite 7 Series FPGA and Zynq 7000 SoC Libraries Guide (UG953)。四输入LUT表的verilog实例化模板:

// LUT4: 4-input Look-Up Table with general output (Mapped to a LUT6)// 7 Series// Xilinx HDL Language Template, version 2023.1 LUT4 .INIT(16'h0000) // Specify LUT Contents) LUT4_inst ( .O(O), // LUT general output .I0(I0), // LUT input .I1(I1), // LUT input .I2(I2), // LUT input .I3(I3) // LUT input); // End of LUT4_inst instantiation

如果需要实现一个4输入的与逻辑;

O = I[3] & I[2] & I[1] & I[0];

实例化代码为:

// LUT4: 4-input Look-Up Table with general output (Mapped to a LUT6)// 7 Series// Xilinx HDL Language Template, version 2023.1 LUT4 .INIT(16'h8000) // Specify LUT Contents) LUT4_inst ( .O(O), // LUT general output .I0(I0), // LUT input .I1(I1), // LUT input .I2(I2), // LUT input .I3(I3) // LUT input); // End of LUT4_inst instantiation

是不是很简单,你学会了吗?

如有疑问,请联系作者。

0

0