1、什么是亚稳态?

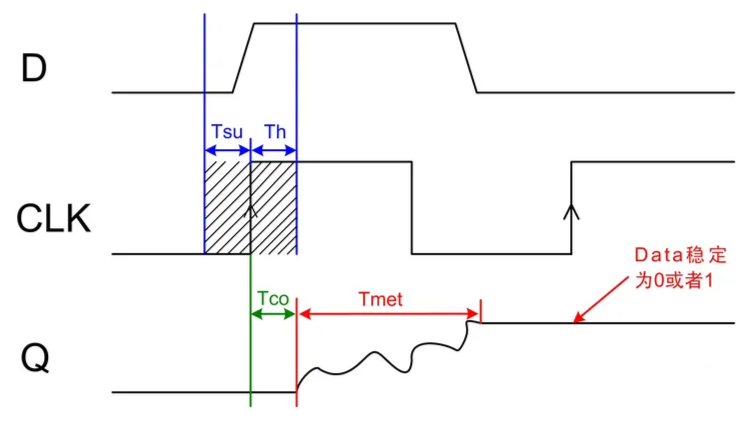

在数字电路中,如果数据传输时不满足触发器FF的建立时间要求Tsu和保持时间要求Th,就可能产生亚稳态(Metastability),此时触发器的输出端(Q端)在有效时钟沿之后比较长的一段时间都会处于不确定的状态(在0和1之间振荡),而不是等于数据输入端(D端)的值。这个时间称为决断时间Tmet(resolution time)。决断时间之后输出端将稳定到0或1上,具体是0还是1是随机的,与输入没有必然的关系。

亚稳态发生的根本原因是寄存器的建立时间要求和保持时间要求没有被满足,这两个时间要求是寄存器的固定属性,一般只和寄存器本身的工艺相关。

不同FPGA的采样时间要求是不同的,工艺越好越高级的FPGA,它们的时间要求越短。也就是说,寄存器采样时更容易满足这两个时间要求,因为它们的时间短,自然落在这个区间的概率也更小。

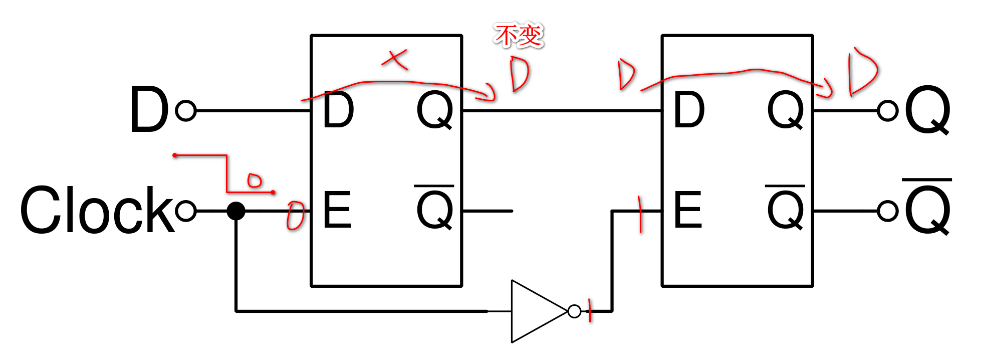

至于为什么寄存器会有建立时间要求和保持时间要求,就要从它们更底层的电路结构来分析了。下图是一个典型的寄存器电路结构:

它由两个锁存器LATCH组成,构成 主从结构 。锁存器在使能信号为高电平时,输入端信号会直接通过到输出端;在使能信号为低电平时,输出端的数据不会发生变化,就像被 “锁住” 了一样。

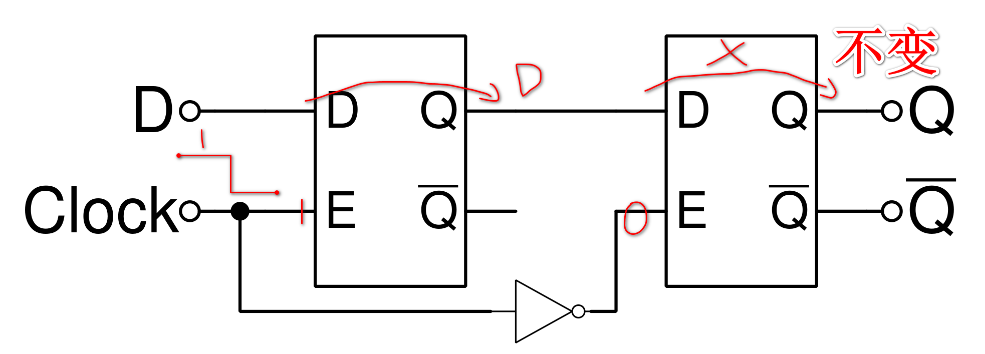

上图是时钟信号为低电平的情况,此时左边的锁存器处于锁存状态,而右边的锁存器属于直通状态。当时钟信号为高电平时,情况类似。此时右边的锁存器处于锁存状态,而左边的锁存器属于直通状态。如下图所示:

在时钟的上升沿,会将左边锁存器的输出送到右边锁存器,并锁住。问题是数据在电路中传递是需要时间的,如果在这个过程中,数据发生了变化,那么输出就不确定了,所以这个时间就是建立时间要求。同理,由于锁存器的锁存也需要一定的时间,因此输入必须继续稳定一段时间才能够保证数据被稳定锁存,这个时间就是保持时间要求。

-

建立时间是在时钟上升沿来临之前将数据锁存的时间

-

保持时间是在时钟上升沿来临之后传输门关断至锁存数据的时间

简单来说,就是数据的采样和变化都不是瞬态完成的,而是需要一定的时间,所以才有建立时间要求和保持时间要求。

2、什么情况下会发生亚稳态?

因为异步信号之间是没有确定的相位关系的,所以异步信号的采样可能发生在任意时间(无法预估),所以只要系统中有异步元件,那么亚稳态就是无法避免的。因此,亚稳态主要发生在异步信号检测、跨时钟域信号传输以及复位电路等常用设计中。

尽管同步信号之间的相位关系是明确的,但也并非没有发生亚稳态的可能,比如时序无法收敛就可能会发生亚稳态。因为同步电路之间的相位关系是明确的,所以综合工具可以对同步电路的寄存器之间进行明确的时序分析,只要给出了正确的时序约束并被执行,那么同步电路之间发生亚稳态的概率就可以忽略不计。

当发生亚稳态的时候,会造成什么影响呢?影响主要发生后级电路上,后级电路无法采样到一个确定的正确值,进而导致运算逻辑错误。

-

数据发生错误

-

逻辑功能发生错误,比如控制信号,握手信号错位

-

发生错误的时间可能随机,很难以复现相同的错误

-

很难以通过软件修复,即使能够修复,也可能需要牺牲性能和功耗

3、如何规避亚稳态?

既然亚稳态会对电路造成如此严重的影响,那么我们自然是要想办法规避了。

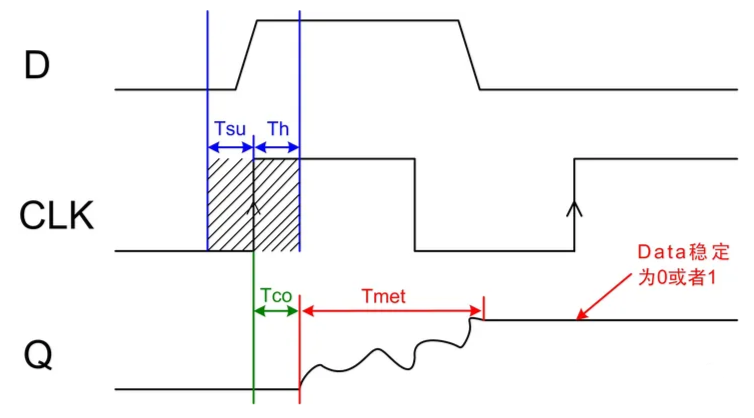

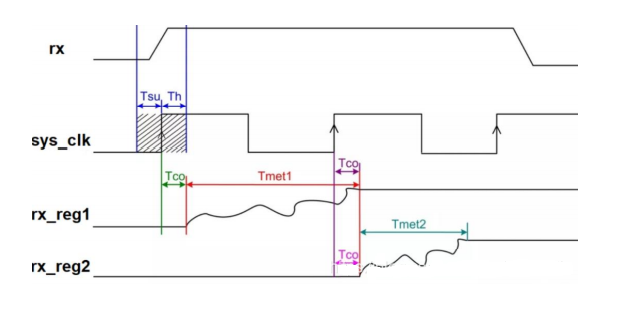

首先要明确的一点是:亚稳态是避无可避的,我们能做的只是降低亚稳态发生的概率。从下图中可以看出来,亚稳态发生后,会有一段时间处于不稳定的状态,在这段时间后输出还是会稳定在一个随机值。也就是说亚稳态自己会在一定的时间后收敛,那就简单了,我们只要在这个时间后再使用信号就可以规避掉亚稳态问题了。

这样的思路其实是正确的,但是有点小瑕疵:这个Tmet时间是不确定的,它可能是20ns,也可能是40ns,反正谁也说不准。但是我们还是可以顺着这个思路来解决亚稳态问题。

方法1:换更高级的芯片

前面说过,越高级的芯片,它的建立时间要求和保持时间要求也越短,只要这个采样窗口变小了,那落在它范围内的概率自然也会变小,进而降低亚稳态发生的概率。这个方法只要你老板同意,确实还行。但是这种活还没干完,就给老板加成本的事,我建议你还是别干。

方法2:降低时钟频率

不是说亚稳态过段时间后可以自己恢复吗?那我只要降低时钟频率(即增大时钟周期),等它自己恢复不就完事了吗?

方法也不错,只是很多方案的时钟在设计之初就已经定下来了,你搞到一半把时钟频率降了,最直观的影响就是系统性能变差了,不能满足最初的设计要求。只要领导能同意产品还没做出来,性能先降了一半,那这办法也不错。

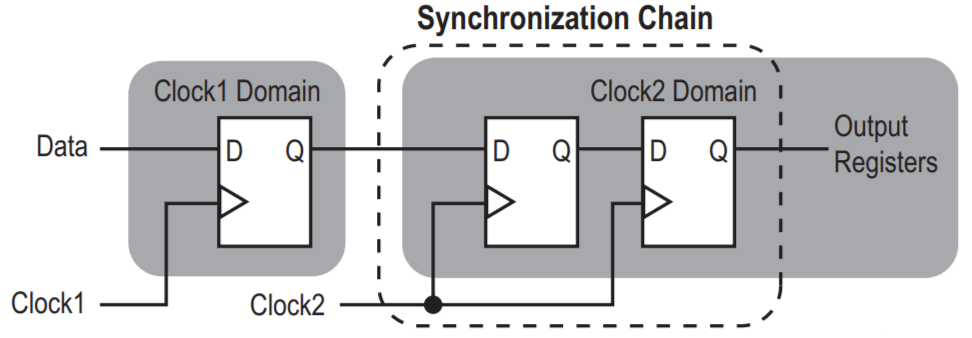

方法3:给信号打拍同步

给信号打拍同步,就是把可能会发生亚稳态的信号接到一定层级的触发器链路上,等待数个时钟周期后再使用。这样做的好处有两个:

-

异步信号变成了同步信号,可以做静态时序分析

-

使用同步后的信号实质上也是在等待亚稳态自己稳定

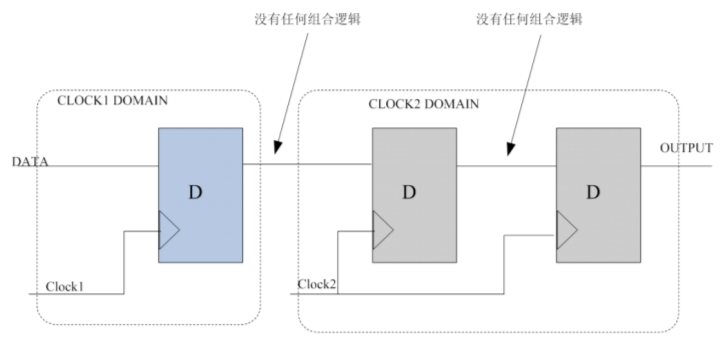

工程中的常见做法是用2个寄存器来同步,示意图如下:

它的时序如下:

并不是说,亚稳态在第1个寄存器就一定不能稳定,也不是说亚稳态在第2个寄存器就一定会稳定,理论上说,你甚至可以打3拍,打4拍,打5拍等等,这样亚稳态发生的概率会更低,只是打两拍,已经可以把亚稳态发生的概率降低到一个可以接收的范围内了。

当然,打两拍的做法并不是唯一解,实际应用还是要看自己的设计要求和器件情况来具体分析。除此之外,还有很多做法来解决亚稳态问题,但它们都是在打拍的基础上的延伸。

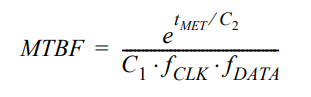

4、如何量化亚稳态发生的概率:MTBF

前面说了,亚稳态是无法被消除的,只能减少其发生的概率,那么这个概率该如何被量化?

在这里要引入一个平均无故障时间MTBF(mean time between failure)的概念。简单来说,就是这个芯片/IP/电路发生两次发生错误之间的时间间隔。

对于不同的系统和应用场景,MTBF的要求也不同。比如说对于我们的手机,应该没有人拿一个手机用三十年吧?如果能够保证MTBF大于30年,等效于在整个手机的使用寿命中,这个逻辑错误不会发生2次,那么针对这个错误来说,这样的MTBF是可以接受的。但是对于有些应用场景,比如通讯卫星,一个通讯卫星的寿命可能超过三十年,那么这种情况下MTBF 如果只有30年,那么就无法接受了。

MTBF 的计算公式如图所示。

-

C1 和 C2 是两个常数,和芯片制造工艺和工作环境(温度,电压)有关

-

fclk 和 fdata 和设计本身有关。fclk 即接收异步信号的时钟域的时钟频率,fdata 即异步信号跳变的频率。也就是说,时钟频率越高,异步信号跳变越多,MTBF 越小,电路越容易失败

-

tMET 是亚稳态稳定可用的时间,时间越长,亚稳态则越可能恢复到稳定状态,电路则越可靠。其值由寄存器的 timing slack 决定,如果有多个级联寄存器,则是其 timing slack 的和

根据这个公式,我们可以想出对应的提高MTBF的办法:

-

更高级的FPGA:实际上就是更小的C1和更大的C2

-

源时钟域异步信号要寄存器输出:寄存器输出可以避免毛刺,毛刺意味着什么,异步信号的跳变。也就是说寄存器输出可以减少异步信号的跳变,即减小 fdata 的值,使 MTBF 变大,电路则更不容易失败。

-

时钟频率越高时,同步器级联的寄存器数目越多:时钟频率越高,fclk 越大,MTBF 越小,电路越容易因为亚稳态失效。因此为了增大 MTBF 的值,可以通过增加级联的寄存器,从而增加 tMET 的值。

-

布局约束时,同步器级联的寄存器越近越好,尤其是当时钟频率很高时:如图所示,当 FF1 与 FF2 越近,FF1 与 FF2 的连线越可能短,FF2 的 timing slack 则越大,tMET 的值便越大,因而 MTBF 越大。Xilinx 提供了属性 ASYNC_REG 可以用来向工具声明哪些寄存器是同步器,工具便可以做相应的优化。

关于MTBF有一个误区需要澄清,就是MTBF只要大于产品的设计使用寿命就可以了,这其实是不严谨的。因为一个产品可能由多个系统组成,每个系统又是由多个子系统组成,每个子系统可能细分下去是由更小的单元组成。整个产品不发生失效的概率是所有部分不发生失效概率的乘积。所以越是小的单元,越要保证MTBF越高,这样才能不会导致整个产品的MTBF 有显著下降。

5、总结

-

建立时间要求和保持时间要求是FPGA中寄存器的固定属性,一旦这两个时间为例,就会产生糟糕的亚稳态

-

亚稳态会导致后级电路处于一个不确定的状态,会导致功能、控制、数据传输等出错

-

只要电路中存在异步数据交互,就无法规避亚稳态,能做的只是想办法降低亚稳态发生的概率,只要把亚稳态发生的MTBF控制在一个适当的值,即可视作解决了亚稳态问题

XNM-6VP高速存储卡

新品推荐

XNM-6VP 是一款基于KU115高性能FPGA的高速存储模块。支持高速缓存 16GB DDR4 SDRAM, 容量最高可达32TB的固态硬盘存储。支持RAID5/6/10,读写速率最高可达10GBps,支持专门为高速实时记录而设计的自定义文件系统。

该模块基于NVME固态硬盘,主要用于高速实时数据流的存储和回放,主要用于雷达、通信、电子、卫星等领域,包括高速ADC数据采样实时记录、DAC数据回放、基于光纤或者Rapid IO的高速数据记录等场景。

• 标准6U VPX架构模块;

• 最多支持8块NVME SSD;

• 支持8TB/16TB/32TB 三种规格;

• 支持标准文件系统;

• ExFAT标准文件系统;

• 实时记录功能;

• 文件在线管理;

• 自检与故障检测;

• 持续稳定记录带宽 ≥8GB/s;

• 持续稳定读取带宽 ≥8GB/s。

1

1