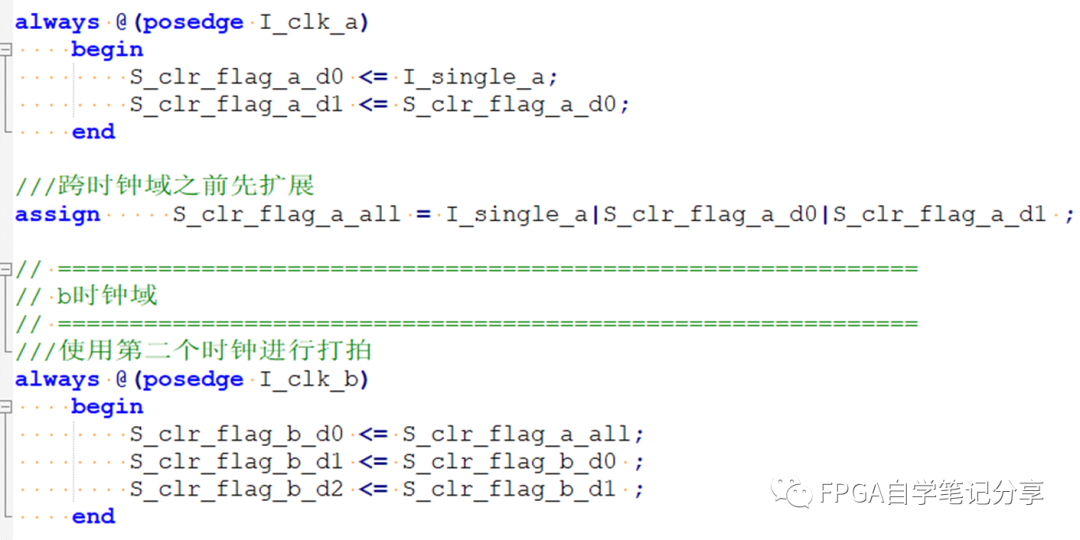

1、跨时钟域之间不能存在组合逻辑。跨时钟域本身就容易产生亚稳态,如果在跨时钟域之间存在组合逻辑会大大增加竞争冒险出现的概率。这一点在实际设计中通常会因为粗心而导致设计异常,如下边代码中的S_clr_flag_a_all信号,就是在扩展时不小心使用了组合逻辑,这种情况下由于竞争冒险,会导致跨时钟域后的b信号出现一个clk的异常电平。

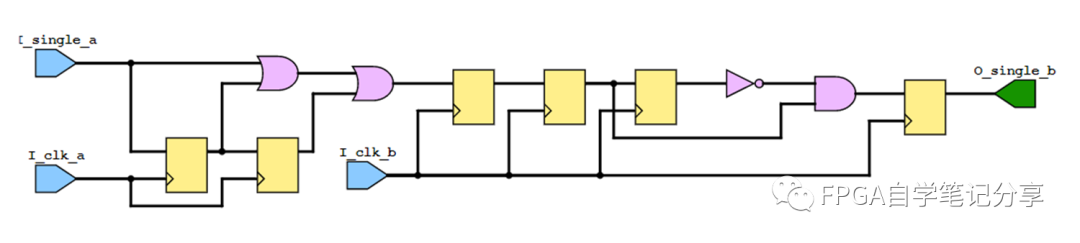

此时的跨时钟域电路为:

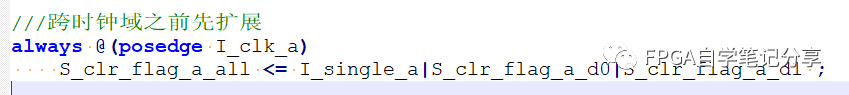

正确的处理方法是使用时序逻辑进行扩展:

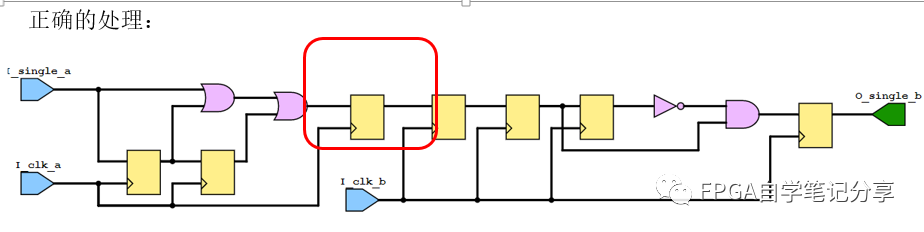

正确的电路为:

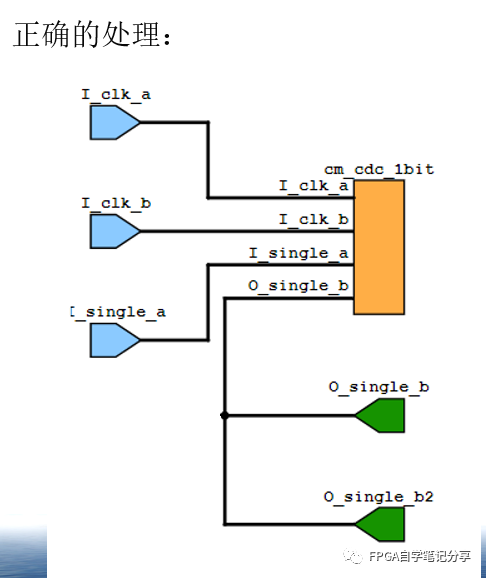

2、跨时钟域信号要集中在一个位置跨时钟域,然后再使用,不能分别跨时钟域处理。

如下图,a时钟域的a信号要在b信号内的b和b2两个位置使用,正确的处理如下:

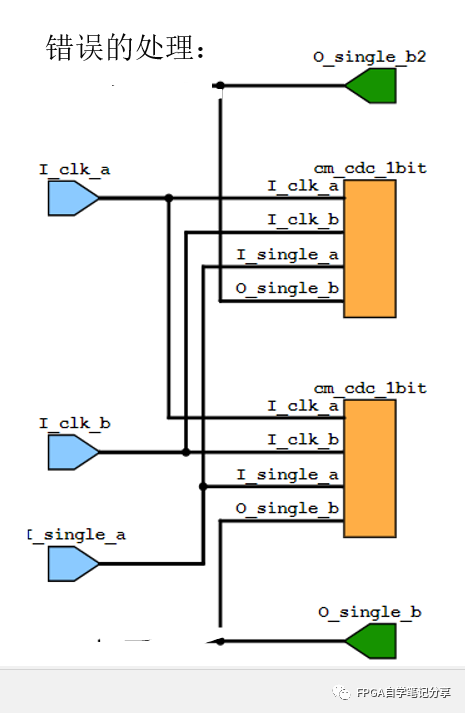

错误的处理方式如下,这种处理方式下,由于b和b2分别做的跨时钟域,由于时钟抖动、走线路径的原因,会导致b和b2不同步,如果该信号是一个关键的控制信号,会导致系统异常,要注意避免这种情况的发生。

0

0