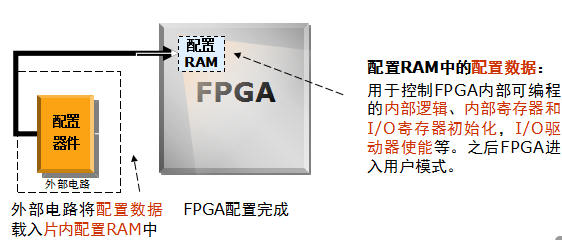

目前,大多数FPGA芯片是基于 SRAM的结构的, 而 SRAM 单元中的数据掉电就会丢失,因此系统上电后,必须要由配置电路将正确的配置数据加载到 SRAM 中,此后 FPGA 才能够正常的运行。

常见的配置芯片有EPCS 芯片 (EPCS4、EPCS8、EPCS16、EPCS64、EPCS128),还有通用的串行 SPIFLASH 芯片如 M25P40、 M25P16、 W25Q16 等。

配置(configuration)是对FPGA的内容进行编程的过程。每次上电后都需要进行配置是基于SRAM工艺FPGA的一个特点,也可以说是一个缺点。FPGA配置过程如下:

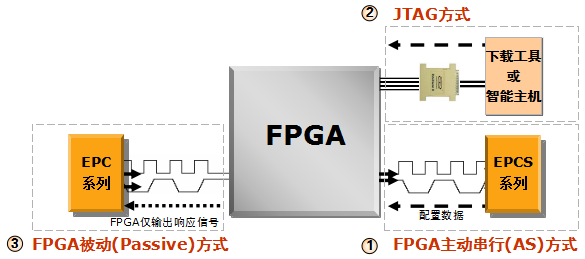

FPGA配置方式

根据FPGA在配置电路中的角色,可以将配置方式分为三类:

1.FPGA主动串行(AS)方式

2. JTAG方式

3. FPGA被动(Passive)方式

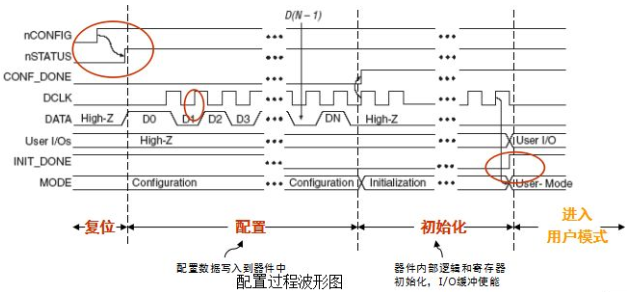

FPGA配置过程

FPGA的配置包括3各阶段:复位、配置和初始化。

当FPGA的nCONFIG管脚上出现一个从低到高的跳变以后,配置就开始了,同时芯片还会去采样配置模式(MSEL)管脚的信号状态,决定接受何种配置模式。

随之,芯片将释放漏极开路(open-drain)输出的nSTATUS管脚,使其由片外的上拉电阻拉高,这样,就表示FPGA可以接收配置数据了。在配置之前和配置过程中,FPGA的用户I/O均处于高阻态。

在接收配置数据的过程中,配置数据由DATA管脚送入,而配置时钟信号由DCLK管脚送入,配置数据在DCLK的上升沿被锁存到FPGA中,当配置数据被全部载入到FPGA中以后,FPGA上的CONF_DONE信号就会被释放,而漏极开路输出的CONF_DONE信号同样将由外部的上拉电阻拉高。因此,CONF_DONE管脚的从低到高的跳变意味着配置的完成,初始化过程的开始,而并不是芯片开始正常工作。

INIT_DONE是初始化完成的指示信号,它是FPGA中可选的信号,需要通过QuartusII工具中的设置决定是否使用该管脚。在初始化过程中,内部逻辑、内部寄存器和I/O寄存器将被初始化,I/O驱动器将被使能。

当初始化完成以后,器件上漏极开始输出的INIT_DONE管脚被释放,同时被外部的上拉电阻拉高。这时,FPGA完全进入用户模式,所有的内部逻辑以及I/O都按照用户的设计运行,这时,那些FPGA配置过程中的I/O弱上拉将不复存在。不过,还有一些器件在用户模式下I/O也有可编程的弱上拉电阻。在完成配置以后,DCLK信号和DATA管脚不应该被浮空(floating),而应该被拉成固定电平,高或低都可以。

FPGA配置模式选择

用户可以通过设置FPGA上的MSEL0、MESL1两个引脚的状态来选择配置方式。各种方式的MSEL0、MESL1设置如下表所列:

说明:

在上表中,如果只采用一种配置方式,则可以直接将MSEL0、MESL1连接到VCC(注意要与FPGA的IO口的供电VCCIO相同)或GND;

如果需要多种配置方式,那么MSEL要用控制器(单片机、CPLD等)来控制以进行切换;

MSEL管脚在配置开始前必须处于一个固定的状态,因此不能将MSEL管脚悬空。

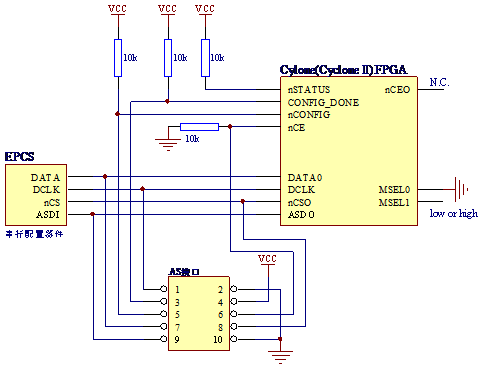

主动串行配置

主动串行配置方式(AS)是将配置数据事先存储在串行配置器件EPCS中,然后在系统上电时Cyclone IV FPGA通过串行接口读取配置数据(如果是压缩数据,还会进行解压缩处理)对内部的SRAM单元进行配置。

因为上述配置过程中FPGA控制配置接口,因此通常称为主动配置方式。在配置期间,Cyclone IV用过串行接口来读配置数据,来对里面的SRAM编程。串行配置器件的四个接口包括,串行时钟输入DCLK,串行数据输出DATA,低有效的片选信号NCE,串行数据输入ASDI。

主动串行配置电路图:

因为FPGA上的nSTATUS、CONFIG_DONE管脚都是开漏结构,所以都要接上拉电阻。FPGA的片选脚nCE必须接地。

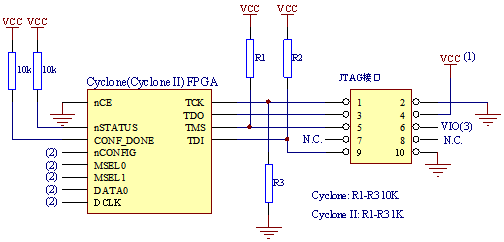

JTAG配置

通过JTAG接口,利用Quartus II软件可以直接对FPGA进行单独的硬件重新配置。Quartus II软件在编译时会自动生成用于JTAG配置的.sof文件。

如果同时使用AS方式和JTAG方式来配置FPGA,JTAG配置方式拥有最高的优先级,此时AS方式将停止,而执行JTAG方式配置。

利用Quartus II软件和USBBlaster等下载电缆可下载配置数据到FPGA。Quartus II软件可以验证JTAG配置是否成功。JTAG配置通过下载电缆使用SOF、Jam或者JBC文件直接对FPGA进行配置,这种配置方式只能用于调试阶段,因为,掉电后FPGA中的配置数据将丢失。

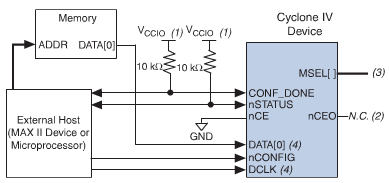

被动串行配置

被动串行PS配置方式是AlteraCyclone IV系列FPGA配置方式中比较常用的方式。但是,在工程应用中若采用这种配置方式,FPGA需要连接一个智能主机(比如复杂可编程逻辑器件CPLD/微控制单元MCU等)以给其提供配置时钟和配置数据。

在该配置方式下,智能主机在保证与存储配置数据的闪存通信无误的情况下,只需向FPGA提供一个DCLK信号和一个DATA0信号即可实现对FPGA的配置。另外,该DCLK信号还可以实现多种频率以满足用户对配置时间的需求,这是该配置方式的一大亮点。

本文介绍了以Altera型的FPGA芯片为例介绍了FPGA的上电过程,并描述了三种常见的配置模式,用户可以根据不同的需求来采用对应的配置模式,每种配置模式下对应的配置数据类型也是不相同的。

0

0